基于Cadence的CMOS反相器的特性分析与仿真

2021-05-21陆亚青

钱 香,陆亚青

(无锡科技职业学院,江苏 无锡 214028)

0 引 言

CMOS电路是同时采用NMOS管和PMOS管构成的一种电路,这种电路的优点是结构简单且规则,静态功耗非常小,所以在大规模和超大规模集成电路中用的较多[1]。CMOS反相器是静态CMOS逻辑电路的基本单元之一,下面先分析CMOS反相器的工作原理,再辅以软件仿真,分析其直流特性和瞬态特性[2,3]。

1 CMOS反相器的设计

文中设计的CMOS反相器中,NMOS管宽长比为2,PMOS管宽长比为5,输入信号为Vin,输出信号为Vout。输入低电平时,NMOS管截止,PMOS管导通,输出为高电平,输入高电平时,NMOS管导通,PMOS管截止,输出为低电平[4,5]。CMOS反相器的输出电压在0~VDD之间,是一种无比电路。

2 CMOS反相器的直流特性

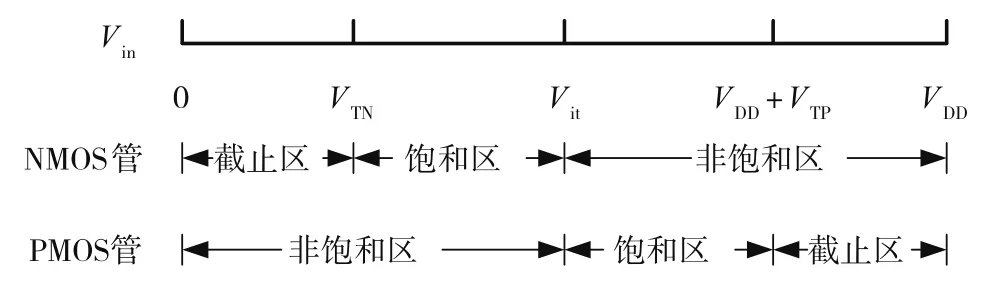

直流输入下,CMOS反相器输出电压随输入电平的变化关系即直流电压传输特性[6-8]。输入信号Vin从0增加到VDD,NMOS管一开始工作于截止区,然后进入饱和区,最后进入非饱和区。PMOS一开始工作于非饱和区,然后进入饱和区,最后进入截止区[1]。结合MOS管工作区域的条件,将输入信号用线段表示,并在线段上将MOS管的工作区标注出来,如图1所示。Vit是反相器电压传输特性中输入和输出相等时对应的输入信号电压值,叫转换电平,也是CMOS反相器输出发生明显变化的转折点[7]。

图1 MOS管工作区域

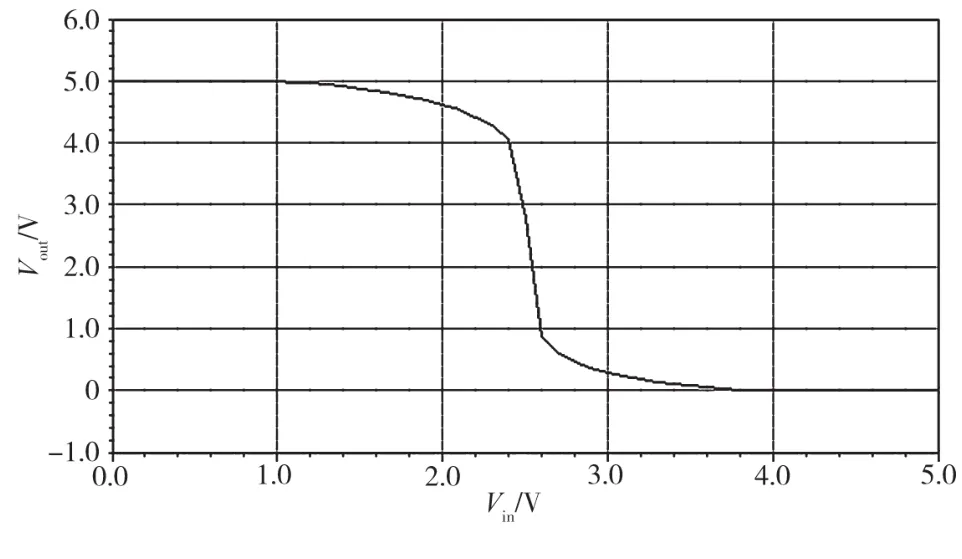

设置CMOS反相器电源电压为5 V,对输入信号进行DC扫描,扫描范围为0~5 V,得到CMOS反相器的直流电压传输特性曲线如图2所示。从图中可以看出,输入电压较小时输出电压为5 V,输入电压较大时输出电压为0 V。输入信号等于Vit时,理想情况下输出电压直线下降,实际情况下由于沟道长度调制效应等原因,是一段变化很陡的曲线。

图2 CMOS反相器的直流电压传输特性曲线

3 CMOS反相器的瞬态特性

在输入阶跃波的条件下,反相器的瞬态特性可以用反相器的上升时间和下降时间来表示。上升时间tr定义为使反相器的输出电平从0.1VDD上升到0.9VDD所需要的时间,下降时间tf定义为输出电平从0.9VDD下降到0.1VDD所需要的时间。设置图1的CMOS反相器电源电压为5 V,输出端增加一个2 pF的负载电容,输入信号设置为周期为1 μs的方波,对电路进行瞬态仿真,得到CMOS反相器的瞬态特性曲线。由瞬态特性曲线可知输入信号为高电平时输出为低电平,输入信号为低电平时输出为高电平,电路实现反相的功能。由CMOS反相器的电路图分析可以得到,在输出高电平状态或输出低电平状态时,CMOS反相器中只有一个MOS晶体管导通,理论上不存在直流导通电流,没有静态功耗,这是CMOS电路的最大优点[9,10]。

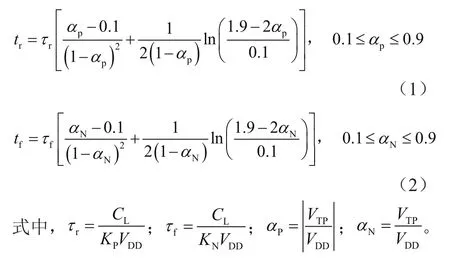

根据上升时间和下降时间的定义,可以得到上升时间和下降时间的表达式分别为:

从表达式中可得,上升时间和下降时间与负载电容的大小、MOS管宽长比的大小有关[1]。改变电路中的参数分别进行仿真,结果记录如表1所示。

一般在设计反相器时要求输出波形对称,即上升时间和下降时间相等。从表1的数据分析可以得到,当NMOS管宽长比为2,PMOS管宽长比为5时,CMOS反相器的上升时间和下降时间近似相等。在负载电容不变的情况下,上升时间随PMOS管宽长比的增大而减小,而下降时间随NMOS管宽长比的增大而减小。

4 结 论

本文用Cadence设计了一个对称型CMOS反相器,并对电路进行了直流特性和瞬态特性仿真,验证了上升时间、下降时间与负载电容的大小、MOS管宽长比的大小有关,且PMOS管宽长比影响上升时间的大小,NMOS管宽长比影响下降时间的大小。CMOS反相器是静态CMOS逻辑电路中的基本单元之一,理解其工作原理及特性对设计其他静态CMOS逻辑电路起到至关重要的作用。