FPGA跨时钟域的数据传输纠错协议优化方法

2021-05-12李建翔李北国杨玉华刘东海

李建翔,李北国,杨玉华,刘东海

(1.中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051;2.中北大学电子测试国家重点实验室,山西 太原 030051;3.北京航天长征飞行器研究所,北京 100076)

0 引言

在信息技术飞速发展的今天,对数据传输的速率、传输距离、误码率提出了更高的要求,更加注重三方面的均衡[1],不仅在航空航天领域,同样在引信领域,越来越多型号设备涉及到高速数据的传输以及需要对其数据进行校验,从而保证设备运行的可靠性及稳定性。

如今的测试测量任务中,尤其是恶劣环境中的测量,前人都已从硬件与软件两方面设计尽可能地降低数据传输的误码率,诸如解决信号在反射、串扰以及传输线损耗等方面的影响,在软件中也加入许多校验重传算法以保证数据传输的可靠性[2]。文献[2]从硬件软件两方面进行优化设计,采用8 B/10 B+CRC+ARQ重传校验的方式保证数据的可靠性,延长LVDS数据的传输距离。文献[3]设计了一种片间通信校验,经过多通道多轮校验,完成数据对齐,补偿由于外界干扰带来的路间延迟,从而保证后续双向通信可靠进行。目前常用的数据传输纠错方法均采用在发送端进行数据编码,接收端再对其进行校验,同时还需要传输链路具备重传纠错功能,在数据出错时及时向发送端反馈信息,重新传输正确的数据。然而目前的方法对于在跨时钟域情况下导致的亚稳态问题并没有解决,会造成重传以及确认指令的触发标志不能正确识别,从而引起数据传输错误。本文针对此问题,提出FPGA跨时钟域的数据传输纠错协议优化方法。

1 传统传输纠错协议

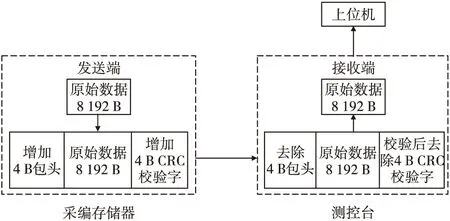

该传输协议已经运用于某型号采编存储器以及与之相对应的地面综合测控台,采编存储器主要功能是通过外部接口接收2路PCM数据,并将数据存储于Flash芯片中,同时也能够与综合测控台通过Hotlink接口进行通讯,远距离传输采用光纤传输,即采编存储器将接收到的数据打包发送给测控台,对其数据进行分析判定。在具体的测试过程中,测控台具备双向RS422链路通信,通过RS422接口上行链路发送启动记录指令,控制采编器启动记录,同时采编存储器将通过RS422接口下行链路返回工作状态至测控台,同时通过Hotlink接口将数据下发至测控台,传输链路框图如图1所示。

图1 硬件传输链路示意图Fig.1 Schematic diagram of hardware transmission link

422指令采取三判二机制,如图2所示,测控台连续发送三次指令,采编存储器若能识别到2次指令,便可执行该命令。在Hotlink链路发送数据的过程中,通过对数据进行CRC校验以提高数据传输的可靠性[4]。数据的具体传输过程如下:采编存储器在下发的每一包8 KB原始数据增加4 B的包头,并对此8 KB数据进行CRC运算,将4 B的校验字附在数据之后,此时形成8 200 B的数据,采编存储器通过Hotlink接口将数据发送出去。在接收端,测控台将再次计算所接收到的8 KB数据的CRC校验字,将计算结果与接收到的CRC校验字比较,如果二者一致,则说明接收数据正确,将数据去除包头和校验字后发给上位机,并通过422接口发出确认指令;如校验错误,则丢弃数据,并通过422接口发出重传指令;若测控台连续发送三次重传指令,测控台仍无法正确接收数据,则将当前数据发送给上位机软件,给采编存储器回复确认命令,并且开始下一包数据传输。以上所涉及返回的确认或者重传指令是在下一包数据的8 100 B之后进行检测,以决定是否重传。

图2 数据传输包格式Fig.2 Data transmission packet format

2 问题分析及优化方法

在经过大量的测试后,发现采编存储器向地面测控台下传数据的过程中,出现了两种类型的数据错误,对其作出归纳后,具体表现如下。

2.1 数据存在多8 KB无效数据的现象

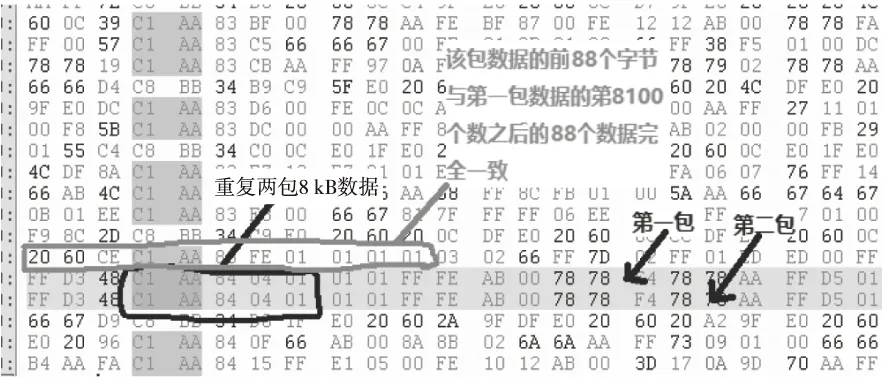

在如图3所标记的两包8 KB数据中,两包数据的前8 100个数据完全一致。同时第一包数据的第8 100个数之后出现4 B数据包头标志和88个数据,此处的88个数据与第一包数据之前的8 KB数据中从1~88的数据内容完全一致,如图4所示。

图3 存在两包数据完全一致Fig.3 There are two packets of data exactly the same

图4 在8 100 B之后数据出现包标志Fig.4 The packet mark appears in the data after 8 100 B

2.2 数据中存在丢失16 KB数据的现象

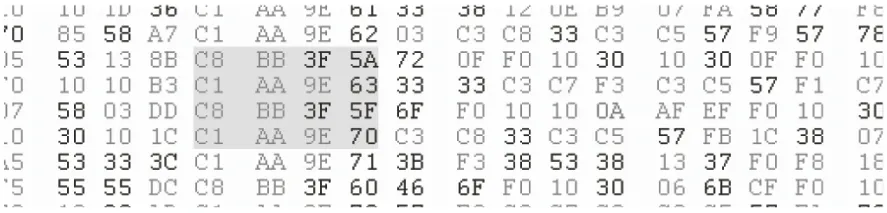

如图5所示,PCM2数据C8 BB 3F 5F和C8 BB 3F 5A之间丢失4 KB数据,PCM1数据C1 AA 9E 70和C1 AA 9E 63之间丢失12 KB数据,总共丢失16 KB数据。

图5 数据中丢失16 KB数据Fig.5 16 KB data lost in data

2.3 问题分析

在数据包具体的传输过程中,如2.1节所阐述,数据发送端(采编存储器)在发送完某包数据的前8 100个数据之后,数据接收端(测控台)会检测前一包数据是否需要重传,此时只会出现两种可能的结果,重传或确认,不管是什么结果,均认为是前一包数据的结果。但是在异常情况下,此处的确认指令可能是前两包数据的结果,前一包数据的结果未正常接收,或者是前一包数据的确认指令被新的重传指令所覆盖,因此会导致发送端发送的数据包不是接收端真正想要的,此时数据就会出现问题。在此种情况下,当接收端接收数据的过程中,只要识别到包头5A 54 5A FE之后,就会开始接收数据,但是数据是否为接收端真正想要的数据,我们无从知晓,因此就会出现如上所述的两种错误。

针对多8 KB无效数据的情况,当发送端(采编存储器)将第A包数据重传被正确接收后,应该下发确认指令,并且正常接收第B包的数据。假若此时该确认指令没有被正常接收,当其发送B包数据至8 100 B时,识别到的仍然是上一次的重传指令,则会继续发送A包数据,此时则会出现数据为8 100 B的B数据+92 B的A数据,导致CRC校验错误,如此往复重传三次,接收端(测控台)强制接收错误数据并发出确认指令,继续发送B包数据,因此就会出现实际情况中B包数据前多出8 100 B B数据+92 B A数据的情况,分析过程如图6所示。

图6 多8 KB无效数据原因Fig.6 Reasons for 8 KB more invalid data

针对丢16 KB数据的情况,当接收端(测控台)在接收A数据出现错误时,应该下发重传指令,此时应延时1 000个时钟重新识别包头以接收正确数据,在此时间里,实际上已经跳过下一包B数据的包头,等待A数据的包头。但此时若发送端(采编存储器)在发送B数据的8 100 B时没有接收到重传指令,仍然默认为上次的确认指令,因此会继续发送C包数据,此时接收端则开始接收C包数据,从而丢失了前两包数据,即问题所在,分析过程如图7所示。

图7 丢失16 KB数据原因Fig.7 Reasons for losing 16 KB data

从以上两种错误数据传输的过程进行详细分析,确定重传以及确认指令的触发标志存在异步时钟域的影响,标志在20 MHz时钟下产生,而在40 MHz时钟下识别标志变化,因此当标志发生变化时,发出重传或者确认指令,由于在40 MHz时钟下仅同步一次,所以可能出现亚稳态现象,导致触发标志变化未能正确识别[5],最终出现了如上两种错误。

近年来,FPGA作为软件中极为重要的一环,特别是在控制、通信、图像处理等关键设备中,且随着功能越来越复杂,单时钟域的FPGA已经逐渐不能满足功能需求,因此多时钟域的FPGA成为设计中不可缺失的一部分[6]。在不同的时钟域之间进行数据交互,亚稳态的现象就不可避免[7]。触发器在时钟沿的驱动下进行数据的采集与更新,如果建立时间与保持时间不能满足要求,使得触发器不能按照预期实现翻转,那么电路就会出现亚稳态,输出电压处于不正确的电平值,导致电路稳定输出的时间不可预知,且可能会存在振荡的风险[8]。

由跨时钟域导致的亚稳态现象具有如下特点:1) 亚稳态是双稳态电路固有的属性,是我们不可避免的,同时依概率发生[9],只能尽量减少其发生;2) 亚稳态的概率性及其对温度的敏感,使其很难在测试与验证中完全体现[10];3) 亚稳态会导致后端逻辑得到的值存在差异,进而影响次级传输,使得整个系统的功能可能与预期存在较大差异[11]。

根据所存在的问题,以及对其进行分析的原因,数据传输协议主要从两方面进行优化设计:

1) 标志判断优化:由20 MHz时钟下产生的重传、确认触发标志,在40 MHz时钟域下同步两次后再进行信号变化的判断,确保测控台的重传或确认指令能成功发送至采编存储器。

2) 接口协议优化:将422重传及确认指令的末位修改为包计数,例如“12 3X”,其中X代表包计数,取值范围为0~15。

2.4 发送端软件优化

发送端更改内容主要为在对8 KB数据增加包头时,在最后一位增加X,其取值范围为0~15,每发送一包数据,包计数增加1;同时每当数据发送至8 100 B时,对其判断是否需要重传,若需要重传,还需判定是重传当前包数据还是上一包数据;若不需要重传时,还需判断所确认的包计数是否为当前发送包计数减1,若为1,则不需要重传,继续发送当前数据包,若不为1,则需要重新发送前一包数据。流程如图8所示。

图8 发送端数据传输优化Fig.8 Data transmission optimization at the sender

2.5 接收端软件优化

接收端更改内容主要为当识别到下载指令信息有效后,开始识别包头,同时解析出包计数X,若X等于receive_cnt,则继续接收该包全部数据,同时根据数据计算出CRC校验码,将接收到的CRC校验码与计算的校验码相比较,若完全一致,则通过422接口向发送端发送该包数据的确认帧,反之则发送重传帧。

若X等于receive_cnt-1,说明接收端未能正确接收前一包数据的确认帧,则通过422接口向发送端发送receive_cnt-1包的确认帧;若X等于receive_cnt+1,说明接收端未能接收receive_cnt包的重传帧,则通过422接口发送receive_cnt包的重传帧。若长时间未接收到数据包头,导致错误计数达到27 576,则不断向发送端发送该包数据的重传帧,直到接收到正确的数据,流程如图9所示。

图9 接收端数据传输优化Fig.9 Receiver data transmission optimization

经优化后的数据包传输过程如图10所示,对每一步骤可能出现的情况均进行了详细的列举。

图10 优化后测控台与采编存储器之间数据包传输过程Fig.10 After optimization, the packet transmission process between the measurement and control platform and the acquisition and editing memory

3 实验验证与分析

对软件更改后,同时在上位机界面单元测试的底部,增加了Hotlink链路错误计数和重传计数两个显示窗口,便于更加直观明了地观察到数据传输是否出现错误以及错误计数,如图11所示。

图11 上位机界面图Fig.11 Interface diagram of upper computer

通过实际测试,对接收到的数据进行解析,如图12所示,为整包数据的测试结果。从图中可以看出,包头为“5A 54 FE”,其后为“FX”,“X”代表包计数,“X”的计数范围为0~15,与协议一致,可以很清晰明了地看出数据包是否连续,以便定位到数据是否出现多数或者丢数现象。

图12 数据包Fig.12 The packet

再次对PCM1的数据进行解析,如图13所示,帧头为“C1 AA”,经过传输的数据帧计数能够依次递增,没有出现丢数多数现象,修改后的协议能够解决所出现的问题。

图13 PCM1数据Fig.13 PCM1 data

利用ISE软件的ChipScope在线分析,对优化后的重传协议进行测试,某次实际测试结果如图14所示,当Error_flag_q为上升沿时开始进行重传,此时帧头为“5A 54 5A FF”,可以看出此时包计数为“E”,同时Retransmission_cnt开始重传计数,实现预期重传反馈功能。

图14 实时重传仿真Fig.14 Real-time retransmission simulation

经过多次测试,在Hotlink电缆为61.2 m(全部为粗缆),重传计数均为0,Hotlink链路错误计数均为0,传输速率约为6.4 MB/s,数据全部正确;Hotlink电缆为78.8 m(61.2 m粗缆和17.6 m细缆),重传计数为10~93,Hotlink链路错误计数为0,传输速率为约6.4 MB/s,数据全部正确;Hotlink电缆为90.8 m(61.2 m粗缆和29.6 m细缆),重传计数为2 000~8 000,Hotlink链路错误计数为0,传输速率为约6.33 MB/s,数据全部正确;在Hotlink电缆断开又重新连接后,数据依然能正常传输,数据全部正确;在422电缆断开又重新连接后,数据依然能正常传输,数据全部正确;在422和Hotlink电缆均断开又重新连接后,数据依然能正常传输,数据全部正确。因此,改进后的传输协议具备更强的链路适应性。

4 结论

本文提出FPGA跨时钟域的数据传输纠错协议优化方法。该方法通过对标志判断以及接口协议两方面进行优化,以使接收端和发送端达到更好的交互,确保重传或确认指令能成功发送,解决了由于跨时钟域导致数据传输出错的问题。仿真实验验证结果表明,优化后指令均能正确下发,数据传输错误计数均为0,数据全部正确,相较于传统的协议更加稳定可靠,具备更强的链路适应性。