封装抗辐射加固技术研究

2021-05-10李靖旸赵鹤然

李靖旸,赵鹤然

(中国电子科技集团公司第四十七研究所,沈阳110000)

1 引 言

卫星等航天器在空间运行时,不再受大气层的保护,电子器件直接受到空间环境中的太空辐射和高能粒子冲击,进而引发出各种辐射效应,导致异常工作状态。根据数据统计,国内外发生的航天事故中,约40%是由空间辐射引发的故障[1]。因此,使用航天器件前,对其进行专门的抗辐射加固处理非常必要。设计加固、工艺加固和封装加固是三种典型的抗辐射加固路径。设计加固和工艺加固是芯片被辐射后采取的应对措施,皆在消除辐射效应的影响[2]。而封装加固具有本质上的不同,是通过屏蔽空间辐射的方式,避免芯片受到辐射的直接影响。为实现理想的封装加固效果,有必要对空间辐射环境、辐射效应影响,以及各种不同封装材料及封装方法有全面深入的理解与把握。

2 空间辐射及辐射效应

2.1 空间辐射环境

空间辐射环境中存在着大量的粒子,其中包括电子、中子、质子、光子以及各种重离子。在地球轨道附近的空间辐射粒子,其主要来源有太阳宇宙射线、银河宇宙射线和地球辐射带[3]。

太阳辐射是空间辐射环境主要的因素,在太阳耀斑大爆发期间,大量带电粒子流与高能射线进入空间。爆发强烈时,地球轨道上的质子及氦离子通量将成倍增加,可达4 个量级;相对银河宇宙射线高能重粒子增加50%。这些高能质子会对地球轨道卫星上的电子设备有极强的破坏性[4]。

银河宇宙射线来源于太阳系之外,主要组成包含氦离子、质子及高能重离子。其离子密度极小、能量极高且各向同性。这些离子的通量峰值能量最小在100 MeV,最高达到1000 MeV。

地球辐射带,又名范艾伦带,分为内外两层,辐射粒子主要包含电子和质子。其中,带电粒子在高层大气和宇宙线的作用下形成高能粒子,经过地磁场不断作用形成电离辐射。

2.2 辐射效应

辐射效应,是辐射粒子与器件相互作用而引发的器件电性能退化。辐射粒子对太空卫星及航天器的电子系统所造成的损伤主要包括总剂量效应、单粒子效应、瞬时剂量率效应及中子效应。

总剂量效应:属于积累效应,是辐射引起的氧化物中的电荷累积。其中,氧化物包含隔离氧化层、栅氧化层和绝缘埋层。当电离辐射作用于器件时,会在这些氧化层中产生电子空穴对,少部分会很快复合移走,而未复合的会进而产生正电荷和界面态电荷,将对器件产生不利影响。电荷长期积累会导致内部漏电流增加,运算放大器输入失调变大,造成材料内部损伤、性能漂移,最终令器件永久损坏。

单粒子效应:作为一种瞬态效应,其产生机理是宇宙中的高能粒子入射到半导体器件中后产生电子空穴对,这些空穴对会引发电路逻辑状态翻转,可能还会产生闩锁。情况严重的将出现永久损伤,甚至导致电路烧毁[5]。

瞬时剂量率效应:该效应的产生通常是在一些特定情况下,如核爆炸产生大量高能射线,在短时间内沉积在半导体器件内,电离出大量的电子空穴对,引发器件内部产生较大的瞬时光电流。这种瞬时光电流会引发器件工作发生故障,例如出现闩锁、逻辑混乱等。

中子辐射效应:中子不带电,但穿透能力极强,如果入射中子的能量足够大,可使晶格内大量的原子产生位移,形成大的缺陷群。在半导体材料内,这些缺陷群在原子的禁带内部引入附加能级,令少数载流子与多数载流子的复合率增加,导致少数载流子寿命减少,从而影响到器件的电学性能。

3 宇航级器件封装加固

宇航器件不仅仅要应对空间环境带来的热、应力问题,更要考虑抗辐射性能,甚至在必要时,牺牲一部分计算性能和存储空间。由于设计加固、工艺加固都需要针对芯片进行专用的研制和开发,其设计周期、流片周期、测试周期都较长,成本也较高。

20 世纪70 年代,国外研究人员们开始重视CMOS 器件的抗辐射加固封装技术,核心是将集成电路芯片与空间辐射环境进行适当的屏蔽和物理隔离。试验证明,封装加固技术对于屏蔽中子和伽玛射线较困难, 但对于屏蔽空间辐射环境的高能电子和质子相对有效,尤其对地球辐射带的电子和质子来说,屏蔽效果明显。因此,对于宇航器件,封装加固是一种扩展使用寿命的直接而有效的途径[6-7]。

4 封装加固研究进展

4.1 金属层屏蔽

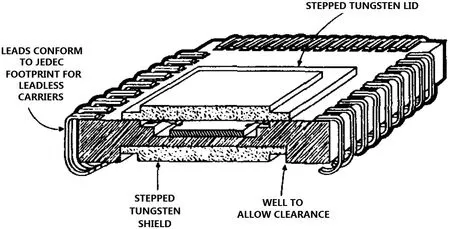

20 世纪70 年代,美国开始研究封装在辐射方面的各项性能,封装方式包括金属封装和陶瓷封装,采用重金属做屏蔽层的封装级屏蔽方法在半导体器件中开始大量采用。来自美国Maxwell 公司的D.G.Millward 和D.J.Strobel 设计了一种名为Rad-Pak的IC 封装结构,如图1 所示,将高Z 屏蔽金属钨层设计到封装结构中,上下采用阶梯状的屏蔽板,总剂量达到 100 krad(Si)[8]。

图1 Rad-Pak IC 封装结构图

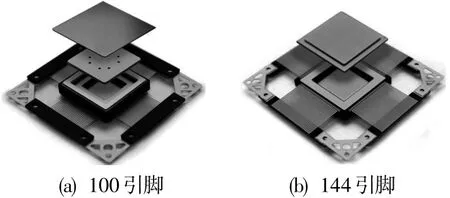

俄罗斯的JSC TESTPRIBOR 设计了专用的带有钨铜合金(85%W 和15%Cu)屏蔽盖的100 引脚和144 引脚陶瓷封装,用于太空抗辐射,如图2 所示。顶盖和底盖的厚度均为1.2 毫米,100 引线封装顶盖上有8 个孔,最上端为可伐盖板,厚度0.25 毫米[9]。

奥肯思北京科技有限公司公开了一种实用新型专利(CN 206558498 U),为一种基于抗辐照加固的芯片封装体,在芯片封装体中设计并安装上下抗辐照加固材料,厚度为0.3~2 mm 的钽片,用于抵挡来自芯片上下方的外太空高能辐射[10]。

图2 集成钨铜合金的抗辐射陶瓷封装体

中国航天科技集团公司第九研究院第七七一研究所发明了一种高密度系统集成计算机模块抗辐照封装结构(CN 202495444 U),采用多层材料复合的上盖板和底板,叠层钎焊钨铜板与可伐框架和盖板,得到高Z 值材料和低Z 值材料的叠层封装结构,形成IC 芯片与空间辐射环境的屏蔽和物理隔离,有效屏蔽辐射[11]。

诸如此类在封装体上下加装金属层的方法的缺陷也很明显:增加了器件的厚度和重量。重量的增加极大地提高了运载火箭发射时的成本。除此之外,屏蔽层与集成电路管芯相距较远,没有实现全方向屏蔽,器件侧面可能仍会受到辐射。

4.2 薄膜屏蔽

随着膜材料技术的发展,人们发现了具有辐射抵抗作用的薄膜,仅仅需要几十个微米厚度,就可以有效降低辐射剂量。

1987 年,日本专利62-125651 阐述了一种名为spotshielding 的抗辐照屏蔽方法。该方法是将一种双层屏蔽膜分别贴在已封装的半导体器件的上、下表面。双层屏蔽膜中的一层主要为高Z 材料,另一层主要为低 Z 材料[12]。

上海航天设备制造总厂发明了一种电子器件抗辐射加固封装结构(CN 103456719 A),包括含铅双马来酞亚胺基体、轻金属薄膜和重金属薄膜。轻金属薄膜的材质是铝,厚度为10μm 或者50μm;重金属薄膜的材质是钨,厚度为20μm,可实现平均抗辐射总剂量大于100 krad(Si),抗辐射效果良好[13]。

薄膜屏蔽在一定程度上提高了芯片的抗辐照能力,相对金属片,增重和增厚显著降低,但仍存在缺点:第一,器件侧面同样会受到辐射,没有实现全方向屏蔽;第二,屏蔽膜可以有效屏蔽电磁干扰辐射,对高能粒子产生的单粒子效应屏蔽效果不佳;第三,宇航级电子器件必须承受太空飞行时加速度产生的较大应力,双层膜容易产生撕裂或翘起。

4.3 陶瓷材料屏蔽

高温共烧陶瓷工艺(HTCC)应用于抗辐照屏蔽的最大亮点在于该工艺能够将钨浆料和生瓷带共烧成具有屏蔽功能的多层陶瓷板。屏蔽功能和钨铜相当,但密度较小,能够有效减轻产品的整体重量。

中国电子科技集团公司第十三研究所发明了一种能够增强辐照屏蔽的陶瓷外壳(CN 102361023B),包括由五层氧化铝陶瓷层构成的陶瓷外壳本体,在其上下表面各增加一层氧化铝陶瓷层,在各个氧化铝陶瓷层的上表面设有采用金属化浆料印刷的起布线作用的线条和起辐照屏蔽作用的图形。相比常规陶瓷外壳,使用此种设计,对空间电离总剂量的辐照屏蔽效果被提高了10 倍以上[14]。

2005 年,法国3D PLUS 公司研制出一种名为WALOPACK 的新型抗辐照封装结构,采用抗辐照高温共烧陶瓷外壳,如图3 所示。其采用HTCC 工艺将多层钨浆料和氧化铝陶瓷制作成陶瓷板,再以该陶瓷板构成密闭封装腔体。3D PLUS 公司已经采用这种结构封装了16 Mb SRAM 器件和8 Mb EEPROM器件,实现了3D 抗辐射屏蔽,可承受的电离总剂量(TID)达到 200 krad(Si)[15]。

图3 3D PLUS 公司的WALOPACK 封装结构

HTCC 封装的半导体器件能够实现3D 全方位屏蔽,组装工艺也简单易行,缺点在于需要针对不同型号尺寸的芯片、不同的组装工艺定制不同的专用陶瓷外壳和盖板。

4.4 包封料屏蔽

利用具有屏蔽功能的胶体将芯片包封起来,也可达到屏蔽效果,实现抗辐照。这种屏蔽胶是将屏蔽粉料以很高的密度填充在树脂中,再添加调节剂控制胶体黏度。

James W.Sloan 等人公开了一种这一类的保护集成电路管芯的方法[16]。封装前,将液态聚酰胺前体化合物沉积在管芯的有源表面上,待初始沉积物固化后,即可在其顶部上层叠相同材料的其他沉积物,从而增加保护材料的厚度。足够厚的聚酰胺涂层可为封装提供α 粒子防护。这一方法的缺点是用于容纳聚酰胺层的空间非常有限,所提供用来保护芯片免受辐射所需的保护材料的厚度可能不足。

采用芯片包封方式进行抗辐照屏蔽的难点在于制备高性能的屏蔽胶体。高填充密度的胶体与裸芯片接触时,其中的金属颗粒可能接触到键合丝或者基板的表面走线,临近颗粒间若发生接触就有可能具有导电性并导致短路。只有利用绝缘强度很高的树脂结合剂将金属颗粒完全浸润并使其始终处于悬浮状态,才能避免短路发生。

Michael Featherby 等人发明了一种屏蔽胶(US 6455864 B1),将屏蔽颗粒分散在粘接剂中[17]。其主要成含有钨粉,环氧混料和其他增补剂。应用于封装屏蔽的结构如图4 所示。这种屏蔽具有高效、经济的优点,其使用方式灵活,可采用模塑、填充、喷涂、包覆等,不仅能够用于封装抗辐射,还可作为人类太空防辐射涂料使人体免受辐射影响。

屏蔽胶优点为使用简便灵活,可局部器件屏蔽,也可以对整个产品屏蔽,且填充过程不占用过多的组装空间。

图4 采用屏蔽胶的封装结构示意图

4.5 塑料封装屏蔽

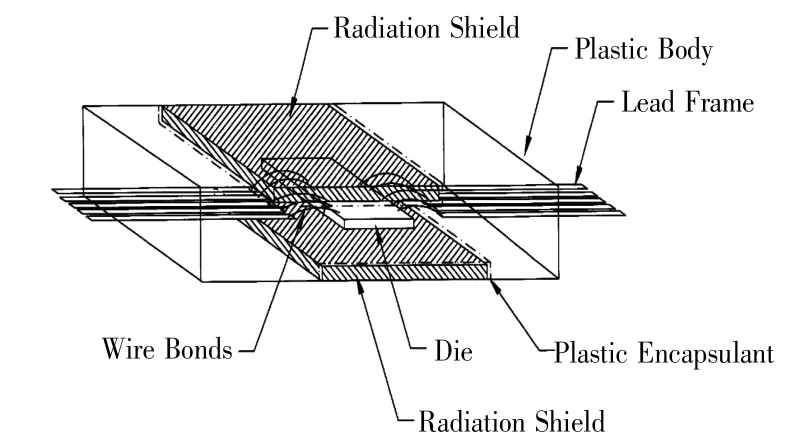

Joseph J.Dlugokecki 等发明了塑料封装重构方法(US5406117A)[18]。该方法将屏蔽材料嵌入组装前的塑料封装体用来提供辐射屏蔽,屏蔽结构如图5所示。采用机械研磨法将塑封后的芯片顶部底部的包封料去除,之后贴装屏蔽材料,最后用附加的包封材料完成密封。

图5 塑料封装重构的剖面示意图

大部分常规塑封器件都可采用这种方法进行重构,重构后的塑封器件外形尺寸变化不大,不影响表面贴装工艺。其缺点是研磨工艺复杂,容易破坏器件内部键合引线,重构后器件厚度略有增加。另外,附加的包封材料需要与原包封料相匹配,同时需具备较强的抵抗水汽渗透的能力。

David J.Strobel 等人发明的塑料封装重构方法(US5889316)[19],结构更加简化。它是通过提供一种新的和改进的工艺来实现的,结构如图6 所示。通过该工艺,有选择地除去形成集成电路的塑料体封装的塑料并用具有特定配方的辐射屏蔽材料代替,即可以根据空间应用需求,定制屏蔽材料。

图6 一种抗辐射塑封结构示意图

5 封装加固技术展望

虽然各国科研工作者长期致力于封装加固技术的研究,但是目前在技术层面仍面临诸多挑战。对于“寸土寸金”的航天应用来说,增重是不得不考虑的关键问题之一。针对这方面问题,未来研究的重点,主要可能集中在以下几个方面:

1) 提高器件有效屏蔽面积比率。封装加固保护的对象是芯片,但是,实际投入的屏蔽材料的面积往往是芯片的数倍之多。因此,封装设计师要尽量减少封装屏蔽的尺寸,从而减少器件的增重。

2) 提高相同质量密度下材料的抗辐射性能。高、低原子序数的金属材料在屏蔽中发挥着不同的作用,新型高分子材料也是研究的热门,如何发挥各材料的特点,制备高性能复合抗辐射材料,是提高相同质量密度下材料的抗辐射性能的重要途径。

3) 开发高性能新材料。近年来,高分子材料、纳米材料等新型材料技术的逐渐成熟,为辐射屏蔽注入了新的活力,研究新型高性能材料的屏蔽机理对指导封装加固的实际工作有重要意义。

除了增重问题,长期服役可靠性仍然是空间应用中的基本要求。不论是一体化屏蔽封装,还是后期涂覆、制备的抗辐射涂层,都应通过元器件的环境测试,屏蔽材料不损坏、脱落,屏蔽性能不退化。

6 结 束 语

对空间辐射带环境以及辐射效应的影响有正确的理解,才能够在确定封装材料与方法时作出正确的选择,确保外太空严酷环境下的器材的正常使用。上述阐述主要从理论层面而言,而在实际应用中,可制造性决定封装加固器件能否实际应用,故此在提升抗辐射指标和确保器件的气密性、绝缘性、耐腐蚀性不降低的同时,还应充分考虑不同批次加固器件的一致性等,这也将在后续研究中作进一步探讨。