一种Ka频段高密度高集成瓦式T组件的设计*

2021-04-25罗鑫

罗 鑫

(中国西南电子技术研究所,成都 610036)

0 引 言

目前,二维有源相控阵按照组装方式主要分为砖式和瓦式[1-2]。砖式结构是芯片放置方向垂直于相控阵天线阵面孔径,电路采用纵向集成横向组装,由于纵向不受限于半波长可根据设计需求扩展,Z向尺寸大,因此,这种结构集成度较低,在实际应用中很难实现中大型阵列规模并保证TR组件长期可靠的工作[3]。而根据系统应用的要求和技术发展情况,有源相控阵天线正朝着小型化、高性能、低成本等方面不断发展[4]。若继续采用集成相对较低的“砖式”结构方式,有源相控阵天线很难实现小型化、轻重量设计。

随着频段的不断扩展,瓦式TR组件在有限的半波长平方内难以完成高密度集成TR组件设计[5]。当前微波及毫米波器件的制造工艺主要分为以互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)或双极互补金属氧化物半导体(Bipolar CMOS,BiCMOS)为代表的硅基半导体工艺和以砷化镓(GaAs)或氮化镓(GaN)为代表的III-V族化合物半导体工艺两大类。GaAs(或GaN)工艺制造的元件的优势在于可以获得较大的输出功率和较低的噪声特性,但另一方面,该工艺也存在集成度低、成本高、无法集成大规模数字电路、工艺一致性较差等问题。CMOS是一种基于硅衬底和标准制造流程的集成电路工艺,虽然在最大输出功率和噪声性能方面逊于GaAs工艺,但具有集成度高、功耗低、成本低等优势,已成为制备大规模集成电路的主流工艺技术。而瓦式TR组件的器件采用唯一一种毫米波器件制造工艺,难以同时满足集成密度、功能密度、射频性能以及可实现性的需求[6]。此外,当收发天线阵面共口径,同时工作使用时,需要在TR组件的末级或者前端放置滤波器,保证接收天线的灵敏度,而通常瓦式天线阵面和滤波功能层分离模块设计,难以实现整个天线的低剖面。

针对上述分析,本文基于瓦式架构,为解决安装空间受限的问题,并且保证一定功率的输出,提出了一种采用CMOS工艺与GaAs工艺相结合的芯片异构集成方案,充分发挥了CMOS工艺强大的数模混合集成能力和化合物半导体工艺优异的射频性能,并将两类芯片在平面内直接异构拼装,在集成密度、功能密度、射频性能以及可实现性等多个方面获得了良好的平衡。利用成熟的多层印制电路板(Printed Circuit Board,PCB)技术,将滤波功能层二维平面一体化集成,通过层间垂直互联实现与天线连接,降低组件的纵向高度。该组件具有良好的工程实现性,可靠性高,有效减少了毫米波有源相控阵天线组件的芯片数量,降低相控阵天线T组件成本,简化了外围电路,提高了横截面的集成度。

1 系统组成和工作原理

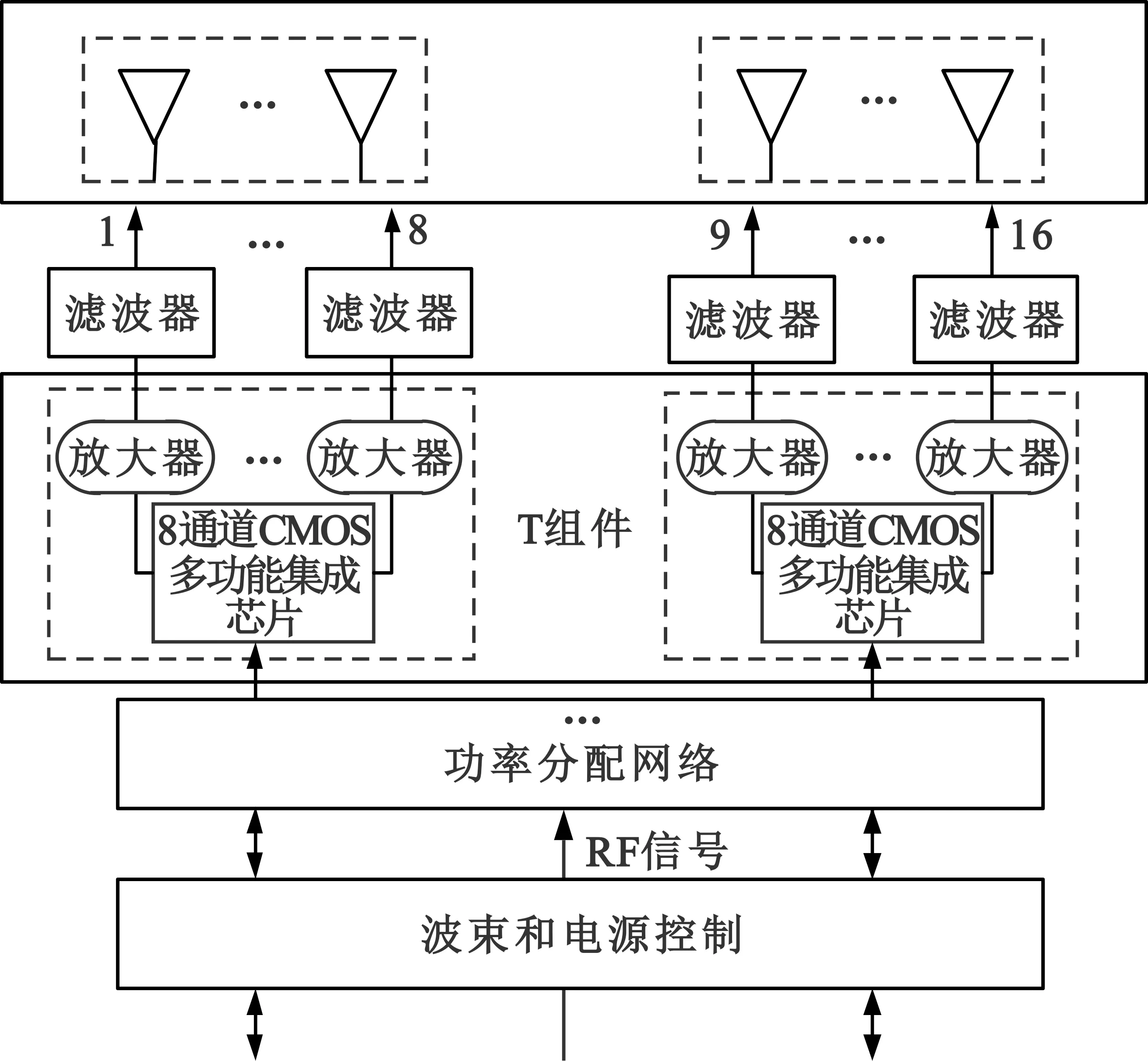

在测控通信领域,由于Ka频段相控阵天线的发射链路和接收链路通常为全双工工作状态,且发射链路和接收链路的工作信号均为连续波信号形式,接收和发射信号工作频率相隔较近,为确保收发链路正常工作,相控阵天线需保证收发通道之间的隔离度要求,为此相控阵发射天线和相控阵接收天线往往采用分开设计,将相控阵天线的T组件和R组件分别进行独立设计,如图1所示。由于阵面横向口径空间受限,接收天线与发射天线虽然分开设计,但间隔很近,空间隔离有限,为了使得功放发射时耦合到接收通道发射频点功率不饱和,在R组件前端增加一级滤波器,滤波器位于接收通道的最前级,因此在确保足够带外抑制的同时必须严格保证极低的损耗,才能尽量降低R组件的噪声系数。同时功放工作时耦合到接收通道中接收频点上的噪声功率不影响正常信号接收。在T组件末端增加滤波器,本文要求20 dBc的带外抑制和小于等于1 dB的插入损耗。

图1 Ka频段相控阵天线原理框图

T组件作为Ka频段相控阵天线的核心部件,由于Ka频段发射天线相邻阵元之间半个波长长度间距狭小,每个发射阵元后端要依次连接功放芯片、移相器芯片等器件,导致T组件没有足够空间来安置,采用常规的T组件集成方法非常困难。本文采用基于两种工艺的套片集成方案,以4×4为子阵进行模块化设计。图2给出了本文T组件的原理框图,每个通道射频信号先1分2功分,然后经8通道CMOS多功能集成的单芯片移相放大,最后经末级GaAs功率放大器再次放大滤波后送达天线。每8个通道共用1个8通道CMOS多功能集成的单芯片控制移相和放大信号,9个芯片就可以实现8个通道功率分配、相位移相、功率放大的功能。

图2 瓦式T 组件原理框图

2 瓦式T组件集成设计

2.1 架构设计

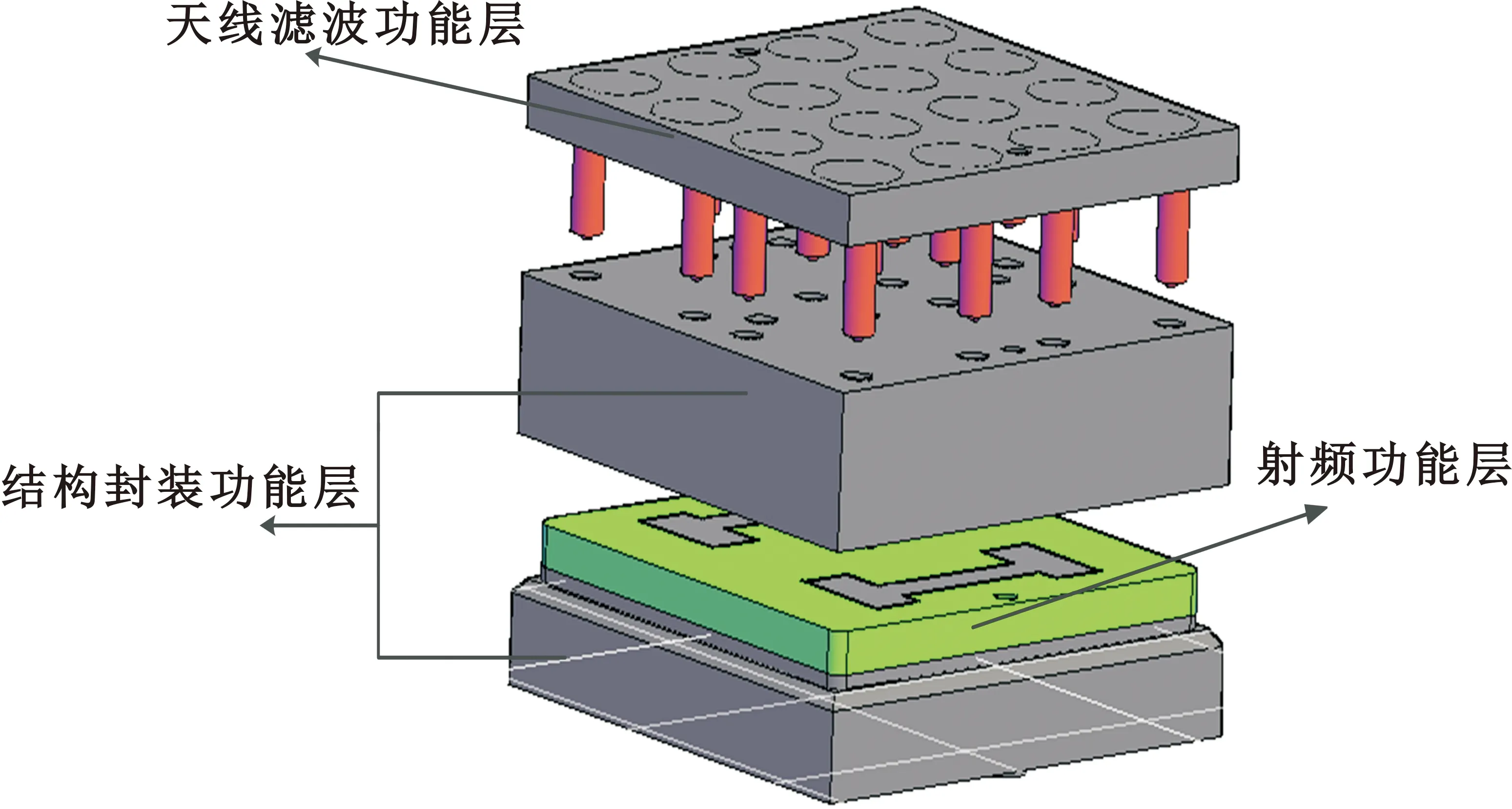

为了保证在扫描角范围内不出栅瓣,相控阵天线要求阵元间距d满足

(1)

式中:λ为波长,θmax为最大扫描角。取最大扫描角为60°,可计算出阵元间距应小于等于0.536λ。本文发射阵元间距取为5.5 mm,在5.5 mm×5.5 mm单元面积内集成所有芯片、滤波电容、馈电和低频控制焊盘、射频接口等功能单元,各通道实现功率放大、移相衰减、信号滤波的功能。根据图2的工作原理,该T组件分为三大功能层,分别是天线滤波功能层,结构封装功能层和射频功能层,如图3所示。

图3 Ka频段瓦式T组件集成架构

天线滤波功能层包括辐射阵面、滤波器,采用多层PCB 技术,一体集成,实现信号的滤波和发射。结构封装功能层包括上、下腔体和射频接插件,主要作为射频和低频接插件、多层电路板和芯片器件的载体,实现组件的气密封装。射频功能层包括芯片器件和多层电路板集成的射频网络和馈电网络,实现功率分配、射频信号相位移相、功率放大的功能。

2.2 T组件专用多功能芯片套片

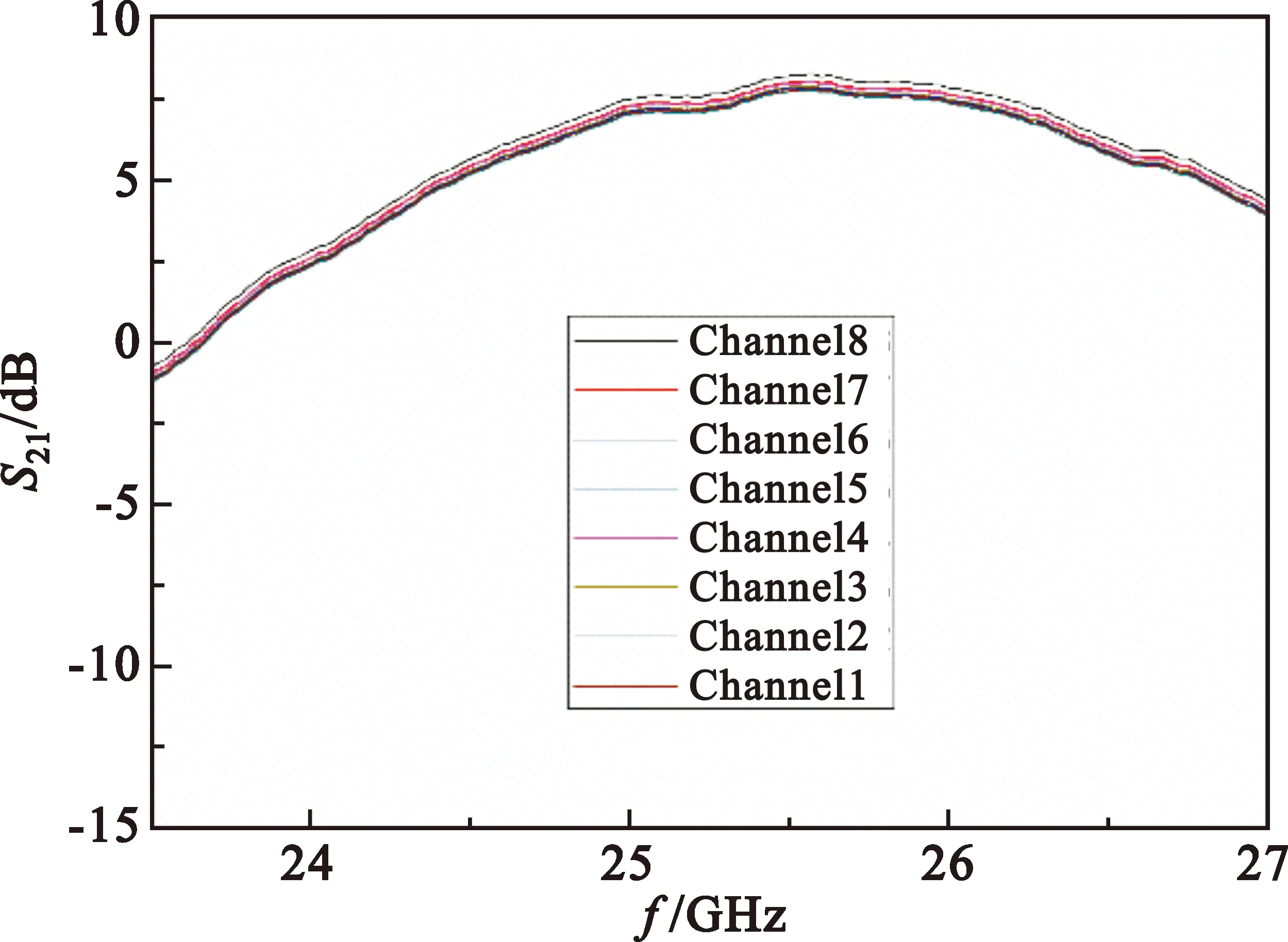

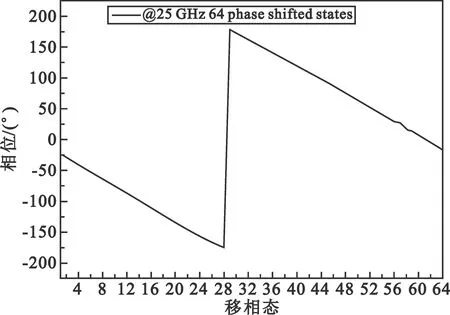

组件以5.5 mm为单元间距,4×4子阵设计,在有限的空间同时满足小间距高密度集成和优良的单通道射频性能,传统GaAs多功能集成芯片已经不能满足集成需求。采用CMOS工艺的多通道多功能集成的单芯片代替,而单片的CMOS多通道多功能集成芯片很难满足发射功率的需求。为了在集成密度和射频性能取得良好平衡,本文提出一种基于8通道CMOS多功能集成的单芯片作为核心芯片(Corechip),并级联8个相同的GaAs工艺制造的功率放大器芯片,2.5维异构集成。8通道CMOS多功能芯片的单芯片集成了模拟电路、数字电路和射频电路,实现了对信号的预放大、数字幅相控制、增益随温度变化自动补偿的功能,如图4所示,每个通道功率的输出P-1 dB为5 dBm,芯片面积约15 mm2。Corechip芯片集成度和功能密度的提高,有效减少了芯片数目的同时简化了外围电路的设计,提高了单元电路面积的集成度,从而解决了空间受限的问题。图5和图6给出了芯片的测试数据。

图4 8通道CMOS多功能集成的单芯片原理框图

(a)芯片8通道间幅度一致性测试

图6 25 GHz时芯片单通道64移相态

同时外部与GaAs工艺制造的功率放大器芯片(面积约2 mm2)2.5维异构集成,由8通道CMOS多功能集成的单芯片输出多路移相、放大后的射频信号给GaAs功率放大器芯片,输出功率P-1 dB为22 dBm,弥补8通道CMOS多功能集成的单芯片输出能力不足的问题,保证每个通道的输出功率。两种工艺芯片的异构,发挥了采用CMOS工艺的Corechip,具有集成度高、功耗低、成本低、多功能的特点,而GaAs工艺制造的功率放大器芯片具有效率高的优点,实现了构建的8通道在集成度和功率之间的一个平衡。8个通道的总面积为242 mm2,每8个通道需要9个芯片,芯片总面积为31 mm2,约占8个通道总面积的12.8%。

2.3 瓦式T组件滤波功能层二维平面一体化集成技术

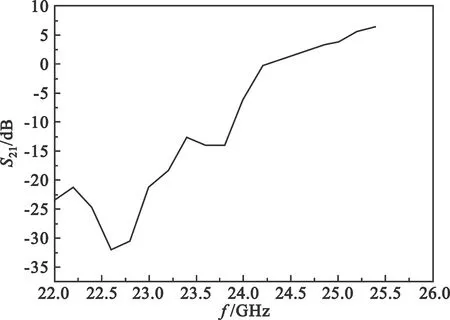

收发共口径相控阵天线全双工工作时,为保证收发组件之间的隔离度,在收发组件的前级要增加一级滤波器,传统的砖式在X-Y平面上集成,导致纵向尺寸大,而瓦式T组件通常组装滤波器的方式是垂直于T组件的芯片面,纵向组装。根据瓦式架构多通道周期平面拓展的布局特点,本文利用多层复合板高密度集成技术设计了一种高容差埋置型支节耦合滤波器,将各通道对应滤波器单元在X-Y平面内等间距周期性展开,构建出与瓦式横向集成纵向组装架构相匹配的滤波功能层,以此替代传统滤波器单通道分离纵向集成的方式。天线和滤波功能层通过层间垂直互联,一体化设计,以毛纽扣压接方式直接安装在T组件上,实现与T组件一体化集成设计,解决了收发信号相互串扰严重的问题,降低了T组件的Z向高度,简化了互连,降低了成本。图7为实测天线和滤波器集成后的增益曲线,在22~23 GHz频段内滤波器的抑制度大于20 dBc,保证了天线测试时接收天线正常工作。

图7 滤波器集成后的增益曲线

2.4 瓦式T组件高低频垂直互联设计

基于子阵模块化设计,垂直互联包括高频和低频,高频主要包括天线阵面和T组件、T组件和功率分配/合成网络,低频主要包括T组件和波束控制、波控器和电源模块。本文采用毛纽扣连接器进行高频连接,将毛纽扣用上腔体固定在天线滤波功能层和射频功能层之间。图8为采用毛纽扣射频互联的T组件16通道实际的无源插损。

在低频垂直互联方面,子阵模块对外连接采用高密度弹性插针方式实现。高密度弹性插针连接器的优点在于,不需要对插的连接器,不需要焊接,两面均通过内部的弹簧设计直接与需要对接电路板的表贴焊盘相连。

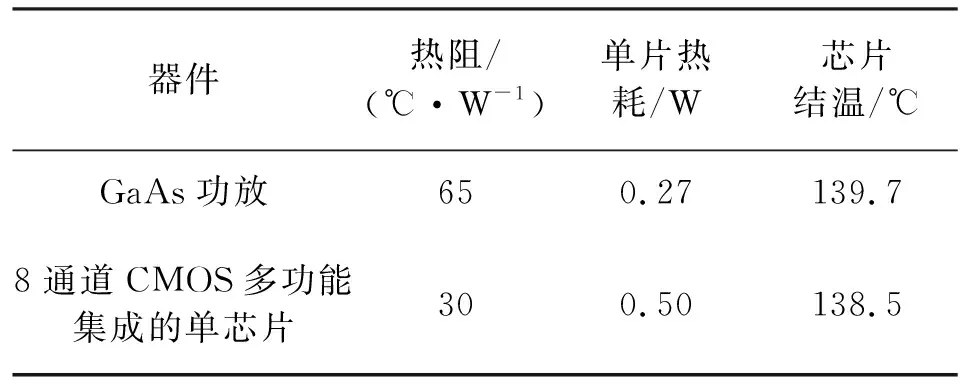

3 环境适应性设计

GaAs功率放大器芯片和8通道CMOS多功能集成的单芯片直接贴装于腔体表面,以利于芯片散热,以使传热路径热阻最小。通过采用快速导热的VC板技术和高效储热的相变储热技术,将芯片所产生的热有效地导出去,保证所有芯片器件的结温能够在允许的温度范围内可靠工作。在热仿真试算中,设定初始环境温度为55 ℃,工作一段时间后,组件达到热平衡状态时,T组件内部温度最高的壳温达到约123.5 ℃。根据结温=壳温+热阻×热耗,芯片结温温度仿真计算结果见表1。

表1 芯片结温温度仿真计算结果

GaAs功率放大器芯片和8通道CMOS多功能集成的单芯片最大沟道温度建议不超过150 ℃,经仿真计算,该T组件可以安全工作。

本文中,选择4×4阵元为基本单元模块的规模,将天线滤波功能层面和T组件阵列按每组4×4单元的形式进行分组,每组作为一个复合模块,天线滤波功能层面通过16个毛纽扣与T组件相连接,多层PCB板嵌套焊接在下腔上,T组件内的GaAs功率放大器芯片和8通道CMOS多功能集成的单芯片安装在下腔上,以利于芯片散热。T组件对外射频输入连接采用1个SSMP插座,低频焊盘裸露于下腔背面,采用高密度弹性插针方式实现低频连接。

为适应平台环境适应性的要求,采用金属腔体将所有芯片和多层PCB板包裹在其中的办法,每个T组件需要单独封装并且保证气密性。T组件的射频入口采用标准的SSMP插座,用铅锡焊焊接在T组件的下腔体上。采用铅锡焊封焊技术对上、下腔体缝隙做密封焊接处理。由于上、下腔之间无螺钉,采用定制的夹具,用于封盖时对T组件的固定。通过密封测试,组件满足平台要求。

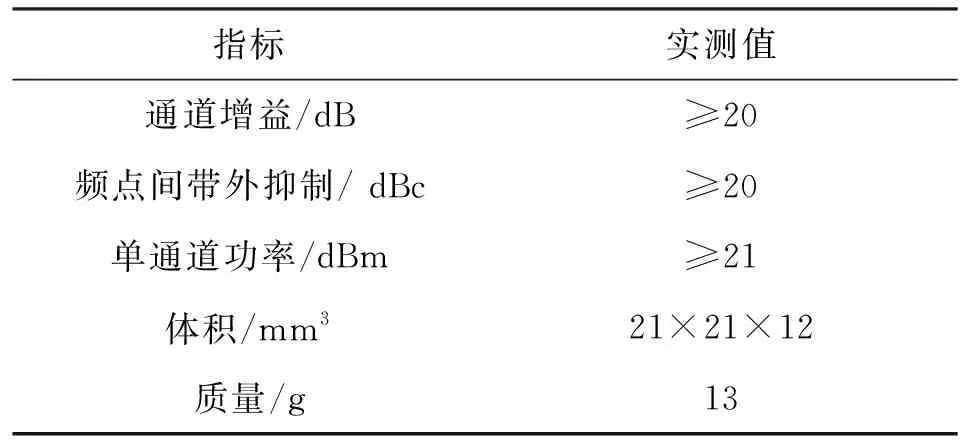

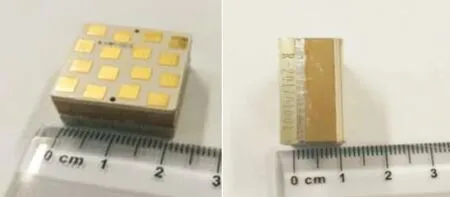

4 实物及其测试结果

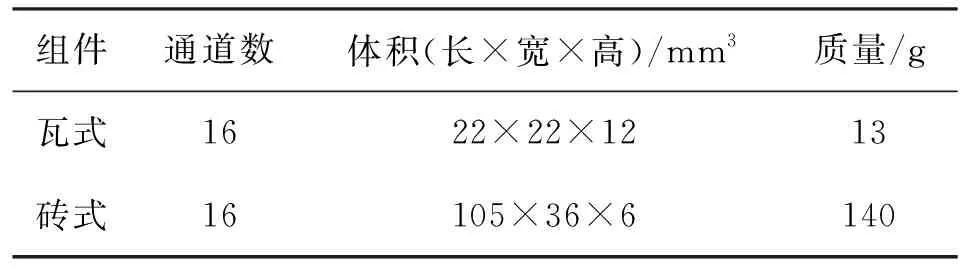

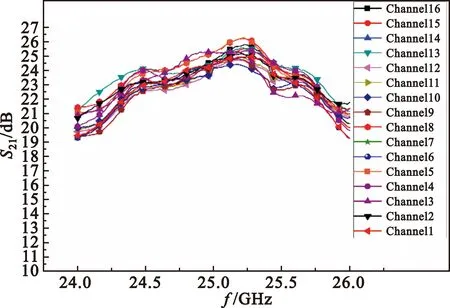

基于以上的设计分析,成功研制出Ka频段瓦片式T组件,测试指标满足整机要求,实测参数如表2所示。图9为本文所研制4×4 瓦式T组件的实物图,表3为砖式T组件的参数对比,图10为T组件16通道幅度和相位一致性测试曲线。

表2 实测指标

图9 瓦式T组件实物

表3 Ka频段瓦式、砖式组件参数对比

(a)16通道幅度一致性测试曲线

5 结 论

本文介绍了一种工作在Ka频段瓦式T组件的集成设计方法,采用CMOS工艺的多通道多功能集成的单芯片作为Corechip的技术路线,突破了基于CMOS多通道多功能单芯片异构集成和应用、带有滤波功能层瓦式T组件二维平面一体化集成等关键技术。基于该方案设计的4×4通道瓦式T组件,在集成密度、功能密度、射频性能以及可实现性等多个方面获得了良好的平衡。与同频段同功能的砖式T组件相比,体积缩减75%,重量降至1/10,具有成本低、质量轻、小型化的特点,能适应不同应用平台的装载要求。