ANT 系列分组密码算法的FPGA 高速实现*

2021-04-24王建新刘芮安肖超恩

王建新,刘芮安,肖超恩,张 磊

(北京电子科技学院 电子与通信工程系,北京 100070)

0 引言

随着信息技术的发展,信息安全问题日益受到重视。在网络空间安全维护、发展的进程中,密码技术在公钥基础设施、GSM 鉴权、电子信封及区块链等[1]领域中起到了关键作用。分组密码算法是保障信息机密性和完整性的重要技术手段[2],在智能终端、无线传感网络等领域广泛应用[3]。目前,所使用的分组密码多为国外设计,且传统分组密码如AES[4]等在资源有限的情况下并不适用。我国自主设计的商用分组密码算法以SM4 算法为主。

近年来,提升科技创新的保障效应和网络安全的动力机能[5]成为网络空间治理的重要目标。为推动密码算法技术进步,中国密码学会举办了全国密码算法设计竞赛。ANT 系列分组密码算法由山东大学网络空间安全学院王美琴[6]等提交,经公开评议、检测评估和专家评选已入选竞赛第二轮名单。

近年来,轻量级密码算法逐渐成为研究热点[7],如HIGHT[8]、PRESENT[9]、PICCOLO[10]、LED[11]、LBlock[12]和Zorro[13]等。作为一款国产轻量级密码算法,ANT 系列分组密码算法具有抗侧信道攻击、适合bit-slice 多路并行实现等优势[6],具有一定的研究价值及应用前景。

为了适应第五代移动通信、物联网等高新技术对密码算法高速实现的需求[14],本文采用流水线结构,对ANT 算法进行高速、高数据吞吐率的硬件设计实现。

1 ANT 系列分组密码算法介绍

1.1 ANT-128/128 分组密码算法

ANT-128/128 分组密码算法采用128 bit 长度主密钥K=k2n-1||k2n-2||…||k0,并可以分为:

K1||K0作为LFSR 的初始状态。每次先取出当前低位寄存器Ki中的n 比特作为当前轮的轮密钥ki,然后进行LSFR 的状态更新,(i+1)作为轮常数(i 为当前轮数),如图1 所示。Ki+1经过A 操作迭代变换3 次,如图2所示。

图1 ANT-128/128 算法密钥扩展结构图

图2 A 操作结构图

在ANT-128/128 算法中,常数t0=7,t1=1。

1.2 轮函数

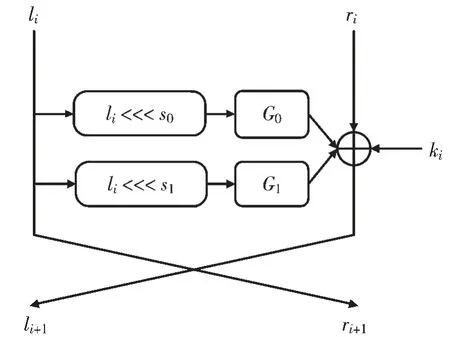

ANT-128/128 分组密码算法轮函数结构如图3 所示,其中,(s0,s1)=(3,16)。为保证加解密一致,最后一轮左支经过轮函数后不进行交换。

图3 轮函数结构图

1.2.1 非线性函数G0 、G1

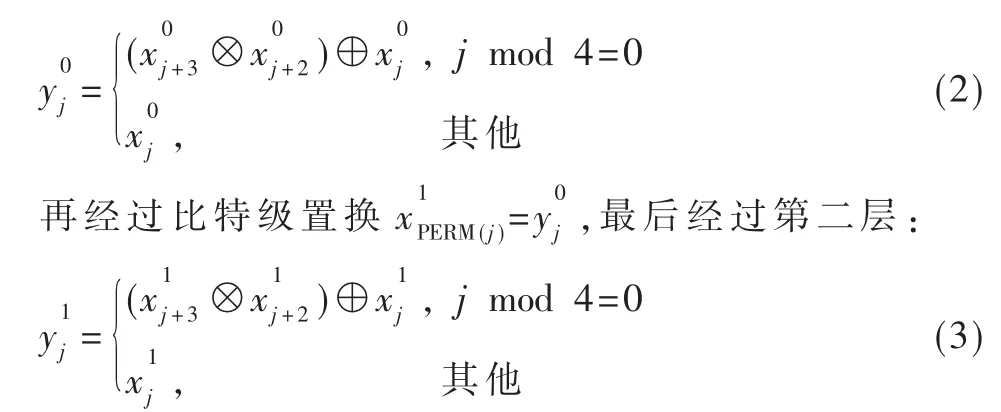

G0、G1为非线性函数,包含两层,两层中间是一层比特级的置换。

(1)对于G0:y1=G0(x0)

先经过第一层:

其中,0≤j<n。

(2)对于G1,结构与G0相同,仅作比特位与模数的变换,在此不作赘述。

1.2.2 比特级置换PERM

在ANT-128/128 算法下,比特级置换PERM 的表达式如下:

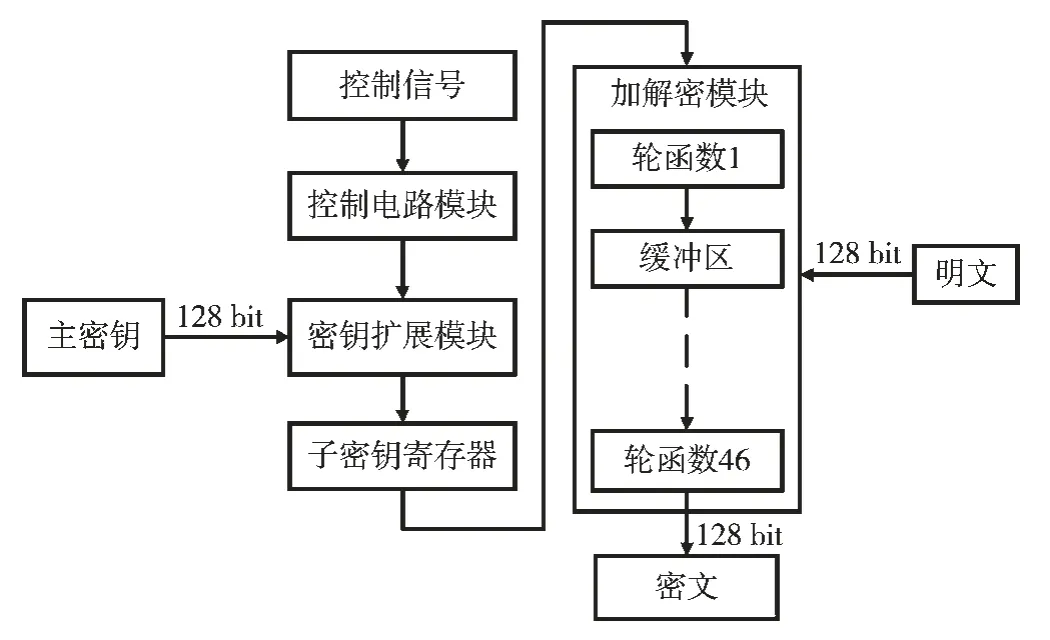

2 功能模块设计

本文采用Verilog HDL 语言以Quartus II 15.0 为平台进行工程实现。系统由两个主要部分组成,分别为密钥扩展模块和加解密模块。本文使用了有限状态机(FSM)[15-16]的设计思路对两个模块进行工程实现,并采用流水线结构对加解密模块进行性能优化,以提高数据吞吐率。系统整体结构框图如图4 所示。

图4 系统整体结构框图

图4 中,在控制信号置位后,密钥扩展模块读取128 bit主密钥并进行子密钥扩展,存储于子密钥寄存器中,供加解密模块调用。加解密模块读取明文,并以流水线的形式同时开始各轮函数运算,在经历46 轮后,生成128 bit密文。下面将对三个模块设计方案进行详细说明。

2.1 密钥扩展模块设计

ANT 密钥扩展模块基于LFSR 实现,采用有限状态机结构,能够达到“状态更新一次,寄存器移位一次”的效果。密钥扩展模块定义的输入端口有:时钟、主密钥以及复位,设置状态字寄存器。当系统检测到复位信号时,电路将从空闲状态转换为工作状态,并在每一个时钟上升沿到来时转换到下一状态。每一轮完成后,生成的子密钥将会存入相应的寄存器,供轮函数调用。经历46 轮后,密钥扩展完毕。密钥扩展模块流程如图5 所示。

图5 密钥扩展流程图

在密钥扩展模块中,为保证数据的扩散性,算法设计了A 操作并对其进行三次迭代,其实质是对比特分组的移位和异或。为提升运算速度,本文经过计算得到A 操作迭代三次后的输出表达式,并将其整体例化为元件。该设计方式无需调用三次“A 操作”,只需调用一次“A 操作三次迭代”,省去了四次异或运算与四次移位。在密钥扩展中,由于各轮中该部分功能相同,只需实现一次元件,并在各轮中依次调用,从而大大节约了硬件资源。

A 操作经计算后的表达式为:

其中,i 为轮数,x[7]、x[6]…x[0]为A 操作输入均分成的8 个32 比特的分组。

2.2 轮函数设计

ANT 轮函数采用Feistel 结构,在每一轮中,左侧输出涉及两个循环左移、两次G 操作和三个异或运算,右侧输出等于左侧输入,不参与运算。对于循环左移,由于各次移动位数相同,本文直接采用位拼接的方式改变输入信号,省去了移位运算。

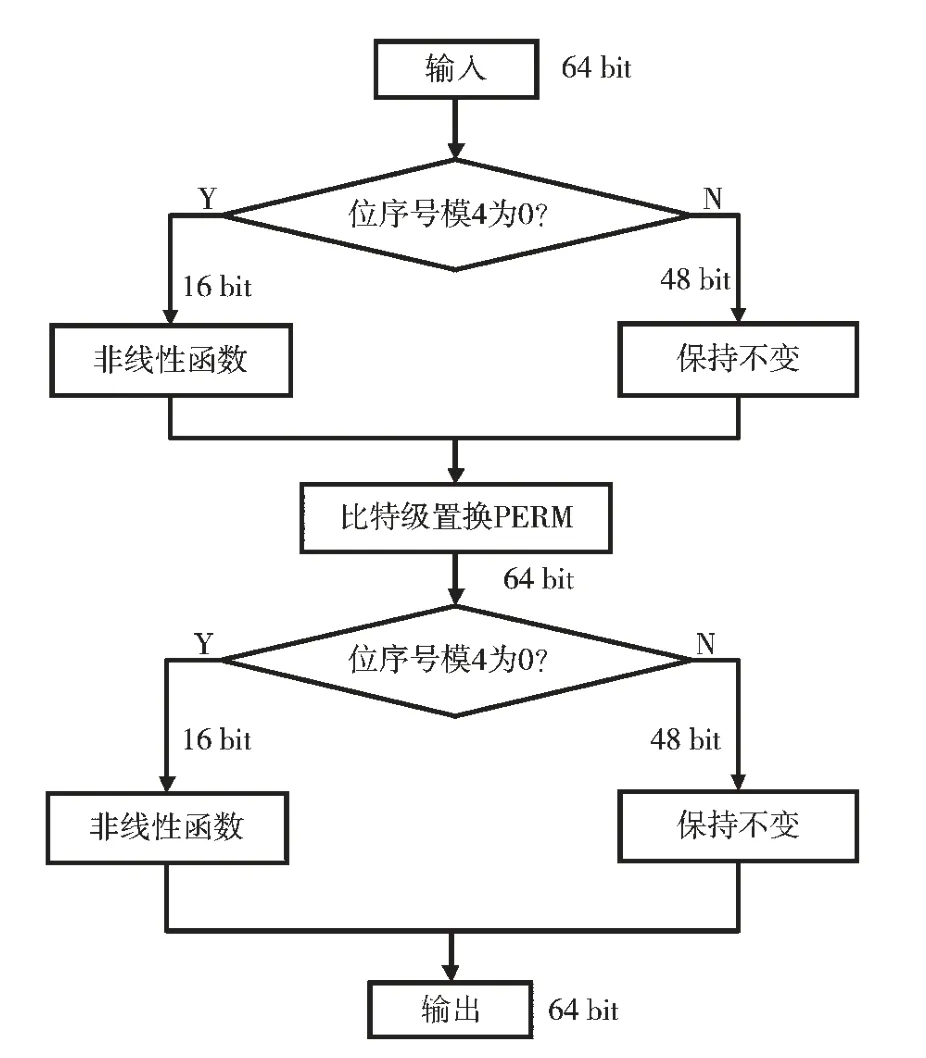

G0、G1操作是比特级非线性函数,仅采用比特级的与操作、异或操作和PERM 置换操作[6]。由于各轮中比特置换PERM 完全一致,本文则直接对相应比特位进行线网型赋值,不进行单独例化,从而减少不必要的运算和资源占用。G0、G1操作功能一致但各轮输入输出信号不同,例化为元件,供各轮调用。G0实现流程如图6 所示,G1与G0操作类似,仅模数不同,故此处不再赘述。

图6 G0 操作流程图

2.3 加解密模块设计

ANT 加(解)密模块中各轮相同功能模块只需实现一次并对其重复调用。由于轮函数每一轮的左输出即为下一轮的右输入;每一轮的右输出即为下一轮的左输入;又因为每轮右输入的值与上一轮左输入的值相同,采用有限状态机方式,定义了左右两组寄存器,实现数据在状态跳变时的依次传递。当系统检测到密钥扩展完成后,状态机跳转至工作状态,读取明(密)文数据。当状态依次更新时,各轮进行左右数据交换,并进行加(解)密运算,以此类推。ANT 算法加解密结构一致,本文仅以加密过程为例。具体流程如图7 所示。

2.4 流水线设计优化

本文采用流水线结构[16-19]对算法进行速度优化。流水线是一种通过增加空间的利用来减少时间消耗的时空映射技术[20],对电路逻辑进行系统分割,在各部分之间插入寄存器暂存中间数据,将大操作分解成若干个小操作。每一个小操作的时间短且支持并行计算。

图7 加密模块流程图

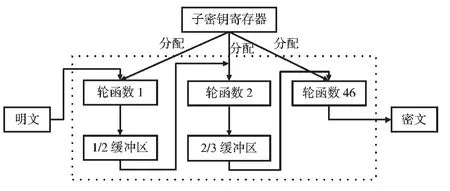

ANT-128/128 算法包含46 轮加解密运算,采用流水线结构可以实现轮运算的并行操作,大大提升加解密效率。在具体实现中,本文采用46 级全级流水线结构,每一轮函数运算结束后,其结果存入缓冲区中,供下一轮函数运算调用。同时,其本身也将从上一轮运算的缓冲区中提取数据,开始下一轮运算。与非流水线结构相比,该方法能够使效率显著提升。基于流水线的加密模块流程如图8 所示。

图8 基于流水线的加密模块流程图

图8 中,轮函数1 使用第一组明文开始运算,将结果存入1/2 轮缓冲区,同时读取下一组明文。轮函数2读取1/2 轮缓冲区中的数据,将结果存入2/3 缓冲区,并再次从1/2 缓冲区中读取新的数据,以此类推。

3 仿真验证与性能分析

本文采用Altera 公司Cyclone V 系列的5CGXFC7D6-F31C7ES 芯片,以Quartus II 15.0 为开发环境对算法进行系统仿真验证与性能分析。

3.1 密钥扩展模块结果与性能分析

密钥扩展模块仿真波形如图9 所示。为方便观察,图中仅列出了00 轮至05 轮、10 轮至15 轮以及最后一轮的数据。算法作者给出的部分子密钥标准向量值如表1 所示,可以得出:仿真结果与标准向量值一致。

表1 部分轮次子密钥标准向量值

密钥扩展模块性能参数如表2 所示。其中,逻辑单元1 663 Slices,占总逻辑资源的3%;寄存器3 185 Slices;综合最大工作频率247.52 MHz。

表2 密钥扩展模块性能参数

图9 密钥扩展模块仿真波形图

3.2 加解密模块结果与性能分析

本文利用Verilog HDL 语言进行了基于单轮单个分组数据的加密,并已将各轮子密钥存储于寄存器中。其中,采用有限状态机设计的仿真波形如图10 所示,采用流水线设计的仿真波形如图11 所示。算法作者给出的密文标准向量值如图12 所示,仿真结果与标准向量值一致。

由表3 可知,采用有限状态机设计的加解密模块占用资源较少,但运算速度不高,其吞吐率v1为:

表3 加解密模块性能参数对比

采用流水线设计进行优化后,虽然占用资源较多,但可以获得更高的工作频率,使得数据吞吐率得到极大提升。流水线设计的最大工作频率为338.52 MHz,其吞吐率v2为:

图10 采用有限状态机设计的仿真波形图

图11 采用流水线设计的仿真波形图

图12 算法作者给出的密文标准向量值

算法作者给出的硬件仿真(基于HJTC110nm 标准元件库)数据中,加密吞吐率约为1.3 Gb/s,而本文所得加密吞吐率为43 Gb/s,约为其吞吐率的33 倍。可见,ANT分组密码算法的加密吞吐率在经流水线结构优化后显著提升。

4 结论

本文对ANT-128/128 分组密码算法进行了相关研究,在用有限状态机结构对算法进行硬件实现后,采用流水线设计对加解密模块进行效率优化,并对二者进行了性能对比。其中,面向速度优化的流水线设计大大提高了加解密速率,在工作频率339 MHz 下,生成一组128 bit 的密文,速度达到43 Gb/s。后续将会对其面积、速度进行更深入优化,进一步提升算法运行效率。