电力无线专网规划精准实测设备的FPGA设计与实现

2021-04-13罗义军

罗义军,杨 凡,李 劲

(1.武汉大学电子信息学院,湖北武汉 430072;2.武汉纺织大学电子与电气工程学院,湖北武汉 430200)

0 引言

电力通信系统是保障电力能够安全地正常运作的重要载体,为了满足智能电力通信网在带宽、实时性、安全性的要求,基于分时长期演进(TD-LTE)技术,在国家无线电委员会批准的230 MHz电力专用频谱上研究开发的新型电力无线宽带系统是一种电力无线专网,系统采用正交频分复用技术(OFDM)、载波聚合、干扰抑制、灵活的帧结构以及2层安全保护等关键技术,实现对电力业务的定制开发[1]。

随着电力设施数量的增加,电力无线专网基站的规划与建设显得更加重要。为推动互联网与电力系统各领域深度融合和创新发展,国家电网公司开展了全球能源互联网前瞻研究[2]。但目前国内外涉及电力通信无线专网尚无一整套融合现场精准实测的规划仿真系统,基站仿真长期存在着基站选址不准确、频段选取不科学、接入方式不可靠等问题。在智能电网快速发展的背景下如何获取海量真实的基站数据,成为电力无线专网规划亟需解决的问题。

针对电力无线专网通信基站规划上述存在的问题,本文从电力无线专网频段需求出发,设计实现一款针对电力无线专网230 MHz频段范围的射频接收机及频谱分析硬件设备,为计算机基站规划仿真提供真实可靠的现场基站数据。

1 系统整体设计与原理分析

1.1 系统整体设计

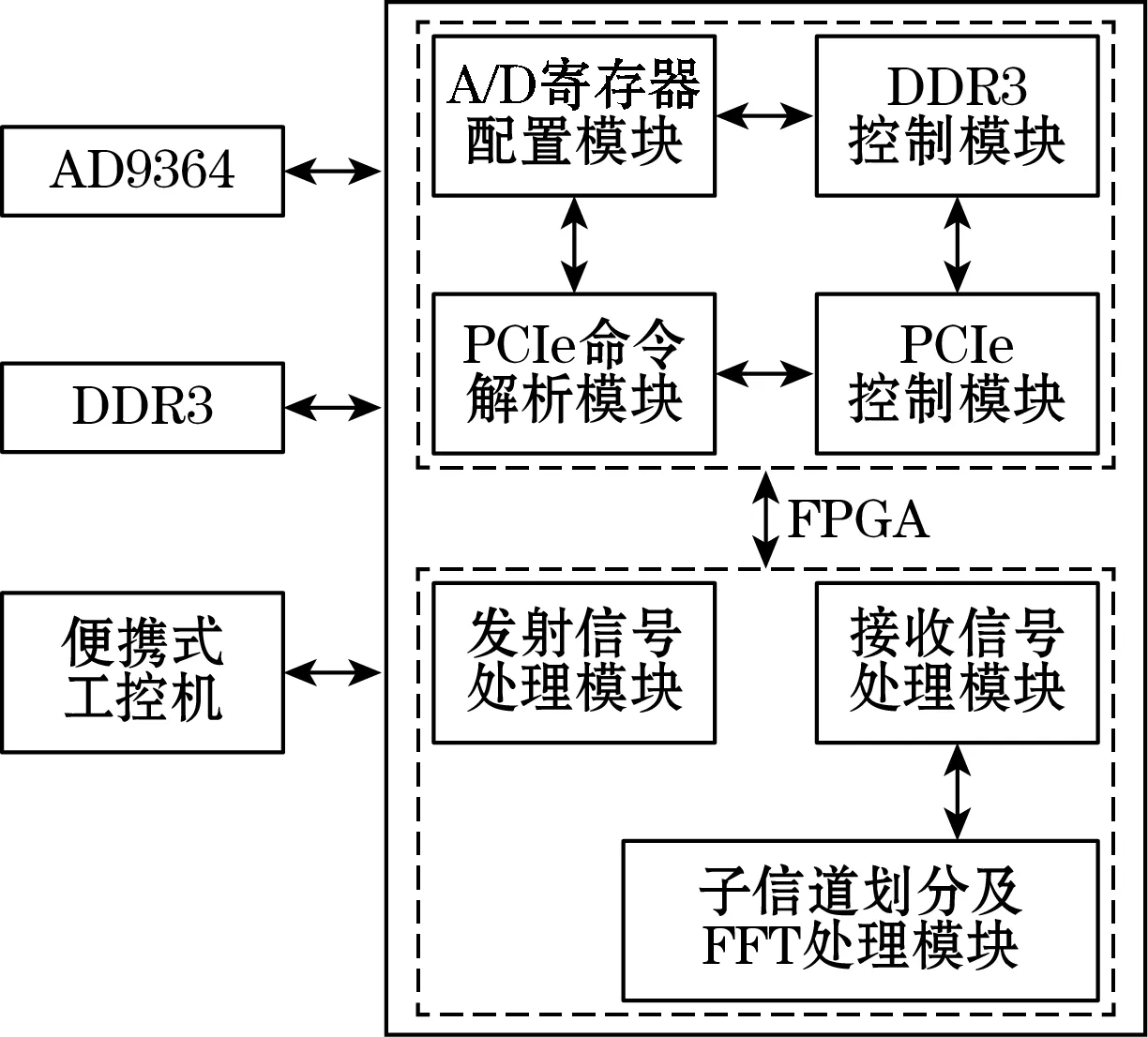

根据电力无线专网的功能需求,整个硬件架构包括FPGA载板,AD采集子板和外部存储板。其中FPGA设计包括A/D控制模块、数据处理模块、信道化模块、DDR3缓存控制模块、PCIe控制模块等。FPGA选用XC7K325TFFG900,FPGA整体方案实现见图1。

图1 系统整体设计框图

射频接收是电力无线专网硬件系统的核心功能,为了简化系统的结构,系统选用AD9364射频收发子板作为A/D采集模块,完成整个系统的LTE 230 MHz模拟射频信号接收过程。AD9364支持频段70 MHz~6.0 GHz,支持TDD和FDD模式,接收器噪声系数小于2.5 dB,拥有强大的收发增益控制等。FPGA载板通过FMC接口与AD9364子板进行数据交换和配置。

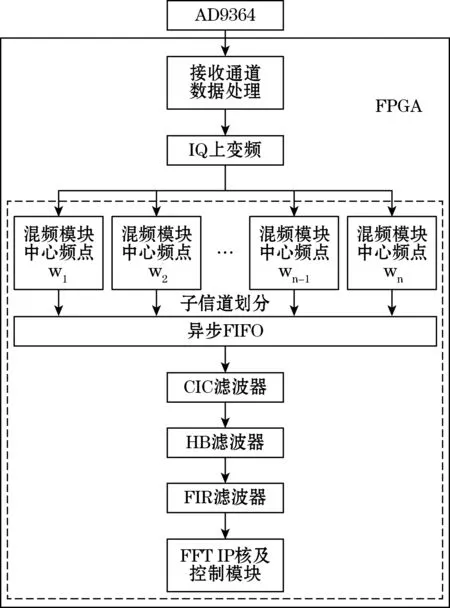

AD9364正常工作时,如图2的接收通道操作所示,FPGA接收到AD9364的信号还需要进行一系列处理,接收通道模块需要对信号进行差分转单端,时序对齐,双倍数据速率(DDR)转单倍数据速率(SDR),信号拼接处理,然后信号会经过子信道及FFT运算。

图2 AD9364接收通道模块设计框图

为了实现100 Hz的频谱分辨率,系统采用数字信道化技术,将信号分为10个子信号,每个子信号的频谱内容等分,互不干扰,通过下抽子信号,达到降采样目的,最后多通道的FFT结果拼接,实现预期的频谱分辨率。子信道划分及FFT模块设计框图见图3。

图3 子信道划分及FFT模块设计框图

1.2 原理分析

频谱分析是本系统的核心功能之一,硬件FFT相比于软件FFT,运算速度快,精度可控。由数字信号处理知识可知,信号采样频率和FFT点数决定频谱的分辨率。在FPGA实现中,FFT IP核采样点数有限制,为提高频谱分辨率,频谱分析采用数字信道化手段。采用多通道滤波的结构,将接收信号转换为多路信号处理,每个子信道的有效带宽中心频率不同,其他参数相同,每个通道通过混频操作将接收信号搬移至信道零中频位置。如图3所示,子信道信号经过混频,CIC、HB滤波,低通滤波后,完成数字信道化操作;通过降低输出信号采样率,达到每个通道更高的频谱分辨率,最终将多个通道频谱拼接在一起,得到信号的整体频谱图。

每个子信道将独立地进行混频,采样率下抽,低通滤波操作,如式(1)所示:

(1)

式中:wk为第k信道中心频率,MHz;BW为扫频带宽,MHz;N为子信道数量。

图4中,N个子信道将最大扫频带宽BW以奇型信道均匀划分,每个子信道具有相同的有效带宽BW/N,每个子信道对应的中心频率wk以带宽为步长增加。这种划分方法结构简单,易于实现;通过将接收信号划分为10个窄带信号,每个信号独立进行FFT操作,达到了输出频谱分辨率100 Hz的要求。

图4 奇型信道均匀划分

2 系统FPGA设计

2.1 AD9364控制及接收通道设计

AD9364芯片需要进行正确的配置才能正常工作,配置文件由ADI配置软件生成,经Python处理后供AD9364控制模块调用。FPGA使用SPI通信协议配置AD9364寄存器。上电后,AD9364控制状态机初始状态为寄存器配置状态,对AD9364进行初始化配置;配置结束后,FPGA会根据读取的AD9364锁定状态选择是否进入通道测试状态;通道测试状态下,AD9364会进入环回测试模式,在该测试模式下,FPGA向AD9364发送的数据通过AD9364接收通道回传至FPGA,以此测试FPGA与AD9364的发射通道的数据完整性;这个环节会调节接收数据的延时,保证接收数据的正确。然后状态机跳转至初始化结束状态,AD9364退出测试模式,开始正常工作。操作流程如图5所示。

图5 AD9364控制状态机示意图

正常工作下,控制状态机等待上位机的指令。接收到指令后,根据指令解析得到寄存器需要读写的数量及是否需要AD9364重新进行校准锁定;如果需要重新校准锁定,状态机会跳转至寄存器配置状态,流程与上电初始化的操作一致,但此时寄存器配置内容由上位机发送到FPGA,不再使用初始化配置内容;如果不需要重新校准锁定,状态机会直接进入寄存器读写状态,等待读写结束后,状态机重新回到等待状态,等待上位机的下一次指令。

根据图2的结构,FPGA对接收的信号,包括数据,时钟及指示信号进行差分信号转单端信号处理,接收随路时钟加入到全局时钟网络,为数据处理提供数据时钟;然后单端处理的数据信号进行时序对齐;时序对齐后的数据还需要进行IDDR操作取出I、Q路数据,将接收时钟上升沿数据取出作为I路数据,下降沿数据取出作为Q路数据。由于芯片接口位宽限制,一个时钟周期AD9364只能传输一半的I、Q数据,FPGA需要根据rx_frame判断当前I、Q数据是完整I、Q数据的高六位还是低六位。图6为AD9364控制及接收通道数据处理的模块顶层的RTL图。

图6 AD9364控制及接收通道顶层RTL图

由于接收数据需要2个时钟周期才能处理一个完整信号,所以接收时钟频率是AD9364的数据速率的2倍。LTE 230 MHz的频率范围为223~235 MHz,经过计算及为了后续FFT操作方便,确定采样频率为65.536 Msps,信号带宽16.384 MHz,接收时钟为131.072 MHz,接收通道中心频率229 MHz。

2.2 子信道划分及频谱分析处理部分

如图3所示,数字信道化模块的输入是一个中频信号,实际操作中,AD9364输出至FPGA的信号是I、Q基带信号,已经在零中频附近。所以这里需要对I、Q基带信号进行上变频操作,搬移至信号采样率的1/4处。如式(2)所示:

ch(t)=I(t)·cosw(t)-Q(t)·sinw(t)

(2)

式中:ch(t)为中频信号,MHz;I(t)、Q(t)为基带信号,MHz;w(t)为混频中心频率,MHz。

将I路信号与cos相乘,Q路信号与-sin相乘,并把2路信号相加;将信号搬移至16.384 MHz,完成IQ调制上变频,混频正弦波由DDS IP核提供。如式(3)、式(4)所示:

In(t)=ch(t)·cosωn(t)

(3)

Qn(t)=ch(t)·-sinωn(t)

(4)

式中:In(t)、Qn(t)为第n子信道的I、Q信号,MHz。

调制中频信号并行进入N个信道,每个子信道信号与设计好的不同频率的正弦波进行混频,分为2路,一路与cos相乘,为信道I路信号,另外一路与sin相乘,为信道Q路信号;每个子信道的中心频率如表1所示,由于信道1、10的频谱范围不在223~235 MHz,FPGA不实现通道1、通道10。

表1 子信道划分中各子信道中心频点

如图3所示,FPGA实现过程中,为了节省资源,DDS,CIC,FIR,FFT IP核都使用了多通道设置,多通道的设置提升了资源使用率,但是CIC,FIR IP核的多通道属于时分复用,需要提升系统时钟频率,同时,FFT IP核运算周期固定,提升系统时钟频率可以减小FFT的计算耗时。为了将数据同步到更高的时钟域,在混频输出到CIC模块输入之间需要使用一个异步FIFO同步数据的时钟域。虽然FIFO的读时钟是写时钟的N倍,但是CIC模块的输入数据更新周期也是N个读时钟周期,所以FIFO的深度不需要太大,等到数据存到一定数量,读写可以同步进行,这个过程不会产生FIFO溢出。同步后的信号经过CIC滤波,CIC滤波器可以在采样率下抽时防止频谱混叠,CIC IP核参数设置中,下抽倍数选择10,级联参数为3,代表下抽10倍采样速率,级联参数的设置使CIC的旁瓣抑制能力达到了-40.38 dB;经过HB滤波,HB滤波器可以实现下抽2倍采样速率的同时防止频谱混叠,并且实现一个较为陡峭的过渡带,最后经过FIR低通滤波,滤除带外多余信号;数字信道化使得输出的信号采样率下抽20倍,采样率变为3.276 8 MHz。

下抽后的信号传入FFT IP核,经过32 768点数的FFT操作,可得到100 Hz的频谱分辨率。FFT控制模块将分离的I,Q 2路子信号组合成FFT IP核规定的数据格式,FFT IP核的接口协议为AXI4-Stream,每个FFT输入数据通道的低16位为通道实部数据,高16位为通道虚部数据,8通道数据依次组成256位数据;FFT控制模块控制FFT处理转换的开始,FFT处理结束后,控制模块将频谱分析结果存入对应的FIFO,然后转存至DDR3。图7是接收信道化及FFT模块顶层RTL图。

图7 接收信道化及FFT模块顶层RTL图

3 测试结果

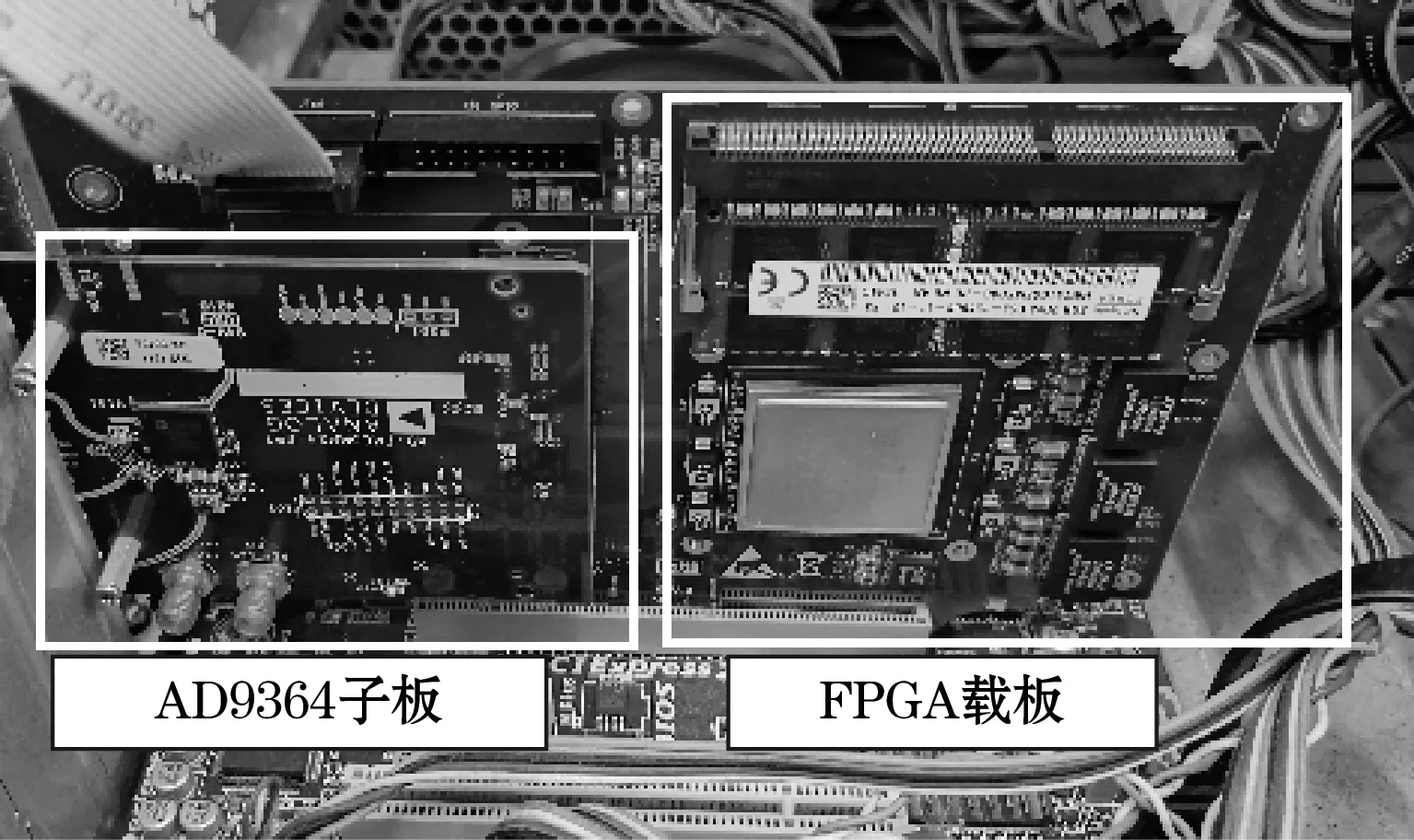

根据图1的系统结构,搭建了一套电力无线专网精准实测设备。如图8所示,FPGA载板与AD9364子板采用FMC接口连接,然后插入到上位机的PCIe插槽;使用Verilog HDL语言在Vivado 2019.1环境中完成系统的设计与调试工作。开发完成后对FPGA进行测试,测试过程主要分为2个部分。

图8 整体联调示意图

3.1 信号接收部分测试

接收部分使用USB射频信号源产生一个230 MHz的正弦信号,AD9364接收中心频率为229 MHz,接收信号采样速率为65.536 MHz。如图9所示,经过AD9364处理过的信号在FPGA中被正确拆分,显示了系统良好的信号接收功能。

图9 AD9364采集230 MHz单一点频信号

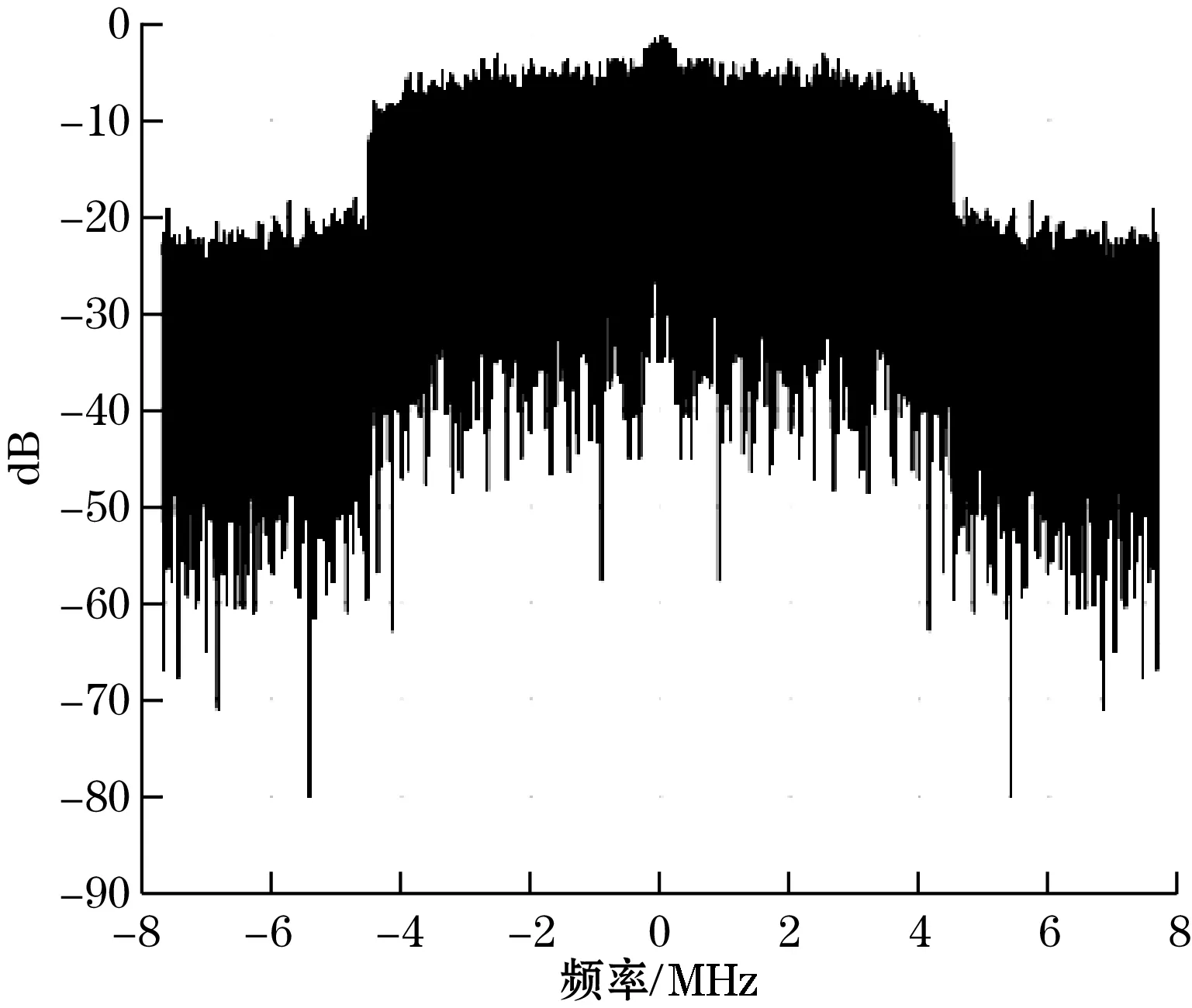

3.2 频谱分析部分测试

频谱分析部分模块使用LTE 10 MHz的信号作为测试输入。通过上位机对PCIe发送指令,FPGA进行频谱分析,通道数据存于DDR3,然后通过PCIe传至上位机存储;经过MATLAB的频谱拼接等后续处理后。结果如图10所示,显示了系统良好的频谱分析能力。

图10 LTE接收信号经过FPGA处理后信号归一化频谱拼接图

经过仿真分析,从子信道化到后续的FFT,整个过程耗时12 ms,与MATLAB的相同频谱分辨率数据处理耗时相比,速度提升大,频谱输出结果与MATLAB运算结果相比,差异不大。所以硬件FFT相对于软件FFT,损失小部分精度但速度得到较大提升,获得了高实时性。

3.3 资源使用分析

最终经过综合和布局布线之后,FPGA的整体逻辑资源消耗情况如表2所示,可以从图中看到,FPGA逻辑资源丰富。布局布线后,LUTRAM、FF、DSP等资源消耗比并不高;FPGA在子信道及FFT部分使用了复用设置,使得整体的逻辑资源占用大幅度下降。为后续设备升级提供了必要的资源预留。

表2 FPGA资源使用表

4 结束语

本文设计并成功实现了体积小型化的射频接收及频谱分析设备,该设备可以用于电力无线专网规划精准实测项目中,为项目的规划算法提供硬件支撑。经过测试验证,该系统能够正确地发送和接收LTE 230 MHz的电力无线基站信号以及实现接收数据硬件FFT操作,系统整体的FFT运算能力和运算速度有较大的提升。与传统的射频接收机相比,该系统集成度高,小型化,兼容性高,携带方便,实时性高,成本低。该系统的成功实现为电力无线专网提供了必要的硬件平台。