基于时钟移位的动态寄存器设计与二进制序列的实现

2021-03-23刘蓉

刘蓉

(扬州大学物理科学与技术学院,江苏 扬州225002)

在现代超大规模集成(VLSI)技术中,高速性能是最重要特性之一。通过在超大规模集成电路设计中引入高速算法,可以做到在数据处理中是非常小的延迟。一般高性能集成电路的特点是它们工作时的时钟频率较高。因此,高速设计可以提高各设计阶段的性能。时钟信号由同步性元件执行,如触发器(FF)或锁存器,其如何操作取决于所应用的时钟脉冲。在实际计算的系统中可能存在两种计时错误,即保持时间违例和设置时间违例。当输入信号在时钟主动转换后变化太快时,就会发生时间步长的计算错误。在设定时间误差时,信号到达太晚,错过了应该提前的时间。信号到达时间的变化有很多原因,是输入数据的变化、电路的不同操作、温度和电压的变化以及设计中各个部分的特性参数差异导致的。

人们曾多次尝试利用混沌现象产生随机数,尤其采用一维混沌映射来设计出各种类型的混沌序列。在蒙特卡罗模拟中,随机数的产生是最重要的环节。此外,为了提高蒙特卡罗模拟的准确性,我们需要周期很长的随机数,最好是无限周期的物理随机数。产生具有特定统计性质的非周期随机数的方法之一是后处理物理随机数或模拟混沌电路产生的非周期随机数。例如,我们提出了使用LFSR(线性反馈移位寄存器)生成相关二进制序列的后处理方法,其中利用了混沌理论的伯努利映射。然而,这种基于LFSR 的后处理生成的二进序列的自相关函数并不是指数消失的,即它们不是马尔科夫二进序列。

1 新移位寄存器方法构建

1.1 保持模式触发器

HM-FF 触发器的单时钟脉冲基于扫描寄存器,使用3 个复用器组成D-FF,如图1 所示。

图1 保持模式触发器

图2 无保持模式触发器

与D-FF 等其他触发器相比,具有保持模式(HM-FF)的单时钟脉冲多一个输入和一个输出。除了时钟和Din (数据输入),scan-enable(scen)存在。Scan-output (Sout)是额外添加的输出。内部逻辑提供以保持模式运行的寄存器,它可以绕过寄存器直接驱动(Scin)的值。

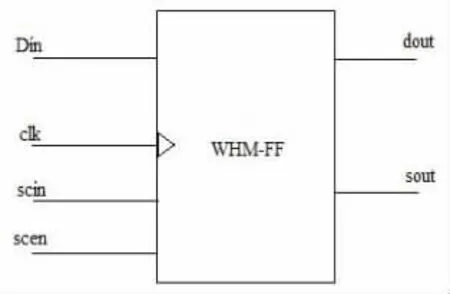

而无保持模式单时钟脉冲(WHMFF) 触发器基于扫描寄存器,使用2 个多路复用器形成D-FF,如图2 所示。与传统的D-FF 相比,单时钟脉冲无保持模式(WHMFF)触发器多一个输入和一个输出。除了时钟和Din (Data in),还有scan-enable(Scen)。Scan-output (Sout)是额外添加的输出。它被用来减少保持模式(HM)触发器的单时钟脉冲的面积。

1.2 移位架构

采用单时钟脉冲保持模式(HM-FF)触发器可以构造串行输入串行输出(SISO)移位寄存器。这种类型的移位寄存器串行地接收数据,即一次接收一位数据,并在其输出上串行地产生存储的信息。这里,四个具有保持模式(HM-FF)触发器的单时钟脉冲级联。由于每个HM- FF 只能存储一位,寄存器最多可以存储四位。更多的触发器可以级联存储超过4 位。时钟在一个时间内应用于所有触发器同步计时。另外还有一个信号叫扫描使能信号,它有两行选择信号,扫描使能信号选择输出信号。使用Scan enable 的主要优点是它在一个时间内只选择特定的输出,从而减少了定时延迟。

虽然锁存可以用来替换FFs,但由于其宽透明窗口,出现了定时限制。因此,PL RFs 可以在FF 和latch RFs 之间提供最佳的折衷,因为它们的定时模型接近FFs,同时它们消耗更少的面积和电力。唯一额外的开销是增加脉冲发生器。然而,这个开销很小,因为相同的脉冲将在相同寄存器的锁存器之间共享。此外,由于脉冲电路控制锁存的透明度,它可以取代FF RFs 写入逻辑所需的时钟门控单元。

2 动态电平结果及二进制序列

2.1 动态电平实验结果

利用Xilinx Virtex 6 低功耗系列,对采用D-FF、单时钟脉冲保持模式 (HM-FF) 触发器和单时钟脉冲无保持模式(WHM-FF)触发器的移位寄存器进行静态时序分析比较。从设计中得到的延迟比较如下。

图3 触发器的延迟比较图

使用UMC 28nm 技术实现了具有不同寄存器数目的普通32 位射频。由于SRAM 的位元是用最小的尺寸设计的,由标准单元组成的存储单元预计会大得多。然而,对于小尺寸的RFs,SRAM 外围电路的区域开销可能非常大。比较不同的实现,基于PL 的RFs 的面积总是比对应的FF 要小20%以上。与SRAM 相比,区域上的差异将取决于寄存器的数量。对于32 字RF, PL RF 的面积比SRAM 高出17%。

2.2 二进制序列

假设我们有如图3 所示的具有正或负自相关的非周期随机二进制序列,将其输入到所提出的后处理电路中。目标是(p1,p2) =(1/4,1/4)和(p1,p2) =(3/4,3/4)的2 态马尔可夫源。

二值序列后处理后的自相关函数,在这些k = 4 的情况下,我们发现一些较大的误差。另一方面在k = 10 的情况下,我们找不到这样的误差。为了研究误差与k 之间的关系,我们使用自相关函数与相应的理论自相关函数MSE。

2.3 新型寄存器方案特点

与传统寄存器方案相比,多端口RFs 是超标量微处理器的关键部件。然而,随着端口数量的增加,面积和功耗都显著增加。多端口sram 的直接实现方式是增加更多的接入晶体管。因此,位单元需要更大的尺寸。加上多余的字行和位行布线,内存大小可以随端口的总数呈二次增长。为了减少面积,使用了两种技术:时间多路复用和阵列复制。在时间多路复用中,同一个端口可以在同一个时钟周期内被访问多次。在数组复制中,内存数组被复制到两个或多个银行,每个银行都有一些读端口,同时共享相同的写端口。类似地,标准单元RFs 可以扩展为具有多个读和写端口。

由于PL 操作依赖于使用脉冲发生器,这些脉冲发生器可以在相同的时钟周期内多次访问相同的寄存器。此外,还可以将其他脉冲发生器分组,对读或写过程执行一些必要的控制操作。这将导致拥有一个具有许多虚拟端口的RF,这些虚拟端口由数量少得多的物理端口生成,使用一些控制逻辑用于读和写端口。在这些控制逻辑中,除了保存一些中间数据如内部读写地址和数据外,还使用不同的脉冲组来产生所需的控制信号。

3 结论

在本文中简要地研究了不同的寄存器文件实现,比较了用SRAM 和触发器实现1R1W 寄存器文件的传统方法,提出了一种适用于小尺寸寄存器文件的脉冲锁存实现及基于动态MCML三态缓冲区的动态寄存器。对所提出的寄存器的检查表明,在存在时钟重叠时所提出的寄存器的行为会发生偏差,因此提出了两种处理方法。为了实现高速设计,讨论了不同的触发器和移位寄存器。提出了利用单时钟脉冲保持模式(HM-FF)触发器、无保持模式(WHM-FF)触发器和移位寄存器实现D-FF 的各种实现方法。比较了各模型静态时序分析的各个方面。该方法针对Xilinx Virtex 6 族,在速度上有一定的提高。与现有方法相比,该方法可减少41.9%的延迟。仿真结果表明,当k 足够大时,所提出的后处理电路可以产生马尔可夫二值序列。此外,简要讨论了多端口寄存器的文件结构,并介绍了一种新的脉冲锁存器实现。与其他实现相比,提出的虚拟端口实现在面积和电力方面都有巨大的节省。