一种时序型总线硬件木马的植入与检测

2021-03-18黄姣英李胜玉杨达明

黄姣英,李胜玉,高 成,杨达明

(北京航空航天大学可靠性与系统工程学院,北京100191)

0 概述

随着集成电路规模的不断扩大和结构复杂程度的不断提高,集成电路的设计和制造均向全球化发展,安全问题日益突出[1]。现有RS 系列总线集成电路具有传输距离长、抗干扰能力强、传输速率高等特点,并且利用FPGA 实现RS 系列总线集成电路串口通信可以使整个系统更为灵活、紧凑,减小整个电路的体积,提高系统的可靠性和稳定性[2]。

近年来,研究人员对硬件木马检测技术以及总线硬件木马的设计、激活以及防护等问题进行了研究。2009 年,JIN 在寄存器传输级(Register Transfer Level,RTL)设计插入了多个硬件木马电路,当木马电路被激活时,造成输出信息被替换和芯片功耗增大,失效、加密信息通过RS232 接口和键盘指示灯泄露等破坏系统功能[3]。2011 年,WANG 等人提出一种带有启用信号的k位同步计数器硬件木马,即常规时序型硬件木马,它有一个确定的触发时间2k-1时钟周期,其中k是计数器中状态元素的数目[4]。2012 年,康涅狄格大学的SALMANI 等人提出一种能够有效缩短木马激活时间的结构,通过在扫描链中插入该结构,可以在测试中提高木马节点的激活概率[5]。同年,凯斯西储大学的NARASIMHAN 等人提出了一种合理利用硬件木马的功能,并通过在数字IP 中的状态机内植入非恶意的木马来实现IP 版权保护的方法[6]。

总线集成电路的功耗与时钟频率有很大关系,在基于侧信道硬件木马识别的过程中,经常以时钟频率作为信号采集样本集的一个特征值[7]。2016 年,华南理工大学的黄哲在寄存器传输级设计了一个基于时钟倍频的可逆计数器硬件木马触发电路,并进行实验仿真验证[8]。2017 年,华南理工大学的黄山提出一种以RS232 电路为目标,利用其波特率倍频特性和停止位特性,在RTL 层设计了一款信息泄露型硬件木马电路[9]。

本文设计一种基于可逆计数器的硬件木马,在一般情况下隐藏于电路中,当特定的阈值触发可改变RS232 总线集成电路的正常传输功能,达到攻击者设定的目的。该木马可以根据实际传输数据位数灵活植入,以在与常规时序型硬件木马同位数和同触发参数下完成更多的总线数据传输。

1 时序型硬件木马

硬件木马从结构上可划分为时序型和组合型2 种,并且具有静默和攻击两种活动状态[10]。根据这两部分特点本文称为触发结构(Trigger)和有效载荷(Payload),有效载荷需要触发结构给定指令信号,但触发结构的运行不依赖有效载荷[11]。时序型触发结构特点是结构简单、体积小、便于选择监测信号且容易隐藏在集成电路中的正常时序结构中,集成电路中大量的时序结构网络,为时序型触发结构的设计与植入提供了条件。

根据触发信号来源,硬件木马触发条件可分为内部触发和外部触发[12]两大类。内部触发条件是电路中某个节点或者组合节点的产生,外部触发条件是集成电路外部输入的信号,通常由接收外部环境变量信号形成或外界人为攻击操作而产生。有关基于时序逻辑的木马中一般包含寄存器时序电路,其激活可通过内部触发条件计数器实现[13]。

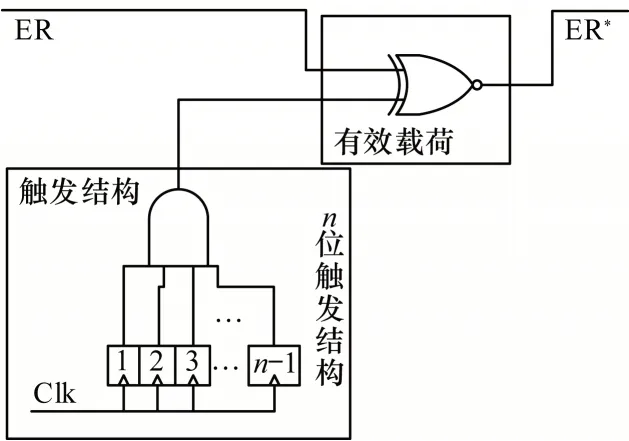

如图1 所示,时序型硬件木马触发结构可以调整时间寄存器位数n与触发阈值m,几何级地降低触发率,大幅降低硬件木马被逻辑功能检测的测试向量激发的可能性,基于时序型的硬件木马具有极低的误触率,并且要比组合型硬件木马更难被检测[14-15]。

图1 n 位同步计数器时序型硬件木马Fig.1 n bit synchronous counter sequential hardware Trojan

2 基于总线硬件木马的载体设计

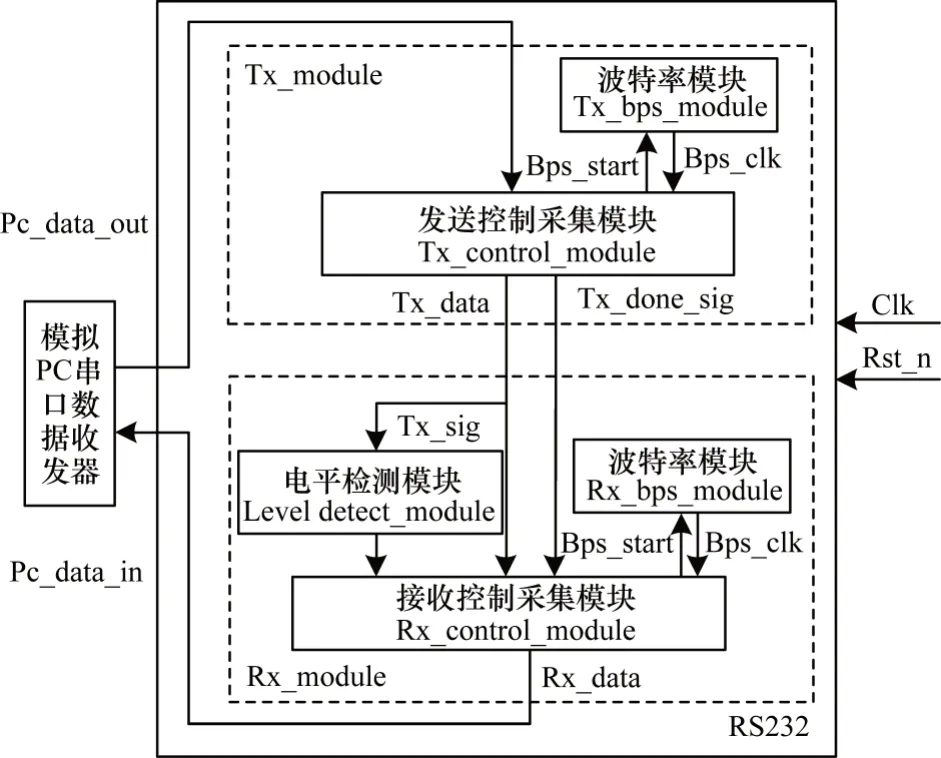

本文针对常规型和可逆型硬件木马,在Verilog代码层设计相应的RS232 总线代码作为硬件木马的载体。如图2 所示,RS232 总线集成电路数据传输系统包括模拟串口数据收发器和RS232 模块两部分。

图2 RS232 总线集成电路数据传输系统Fig.2 RS232 bus integrated circuit data transmission system

2.1 模拟串口数据收发器

本文设计一种模拟PC 功能的串口数据收发器,可以对所设计的RS232 总线平台实现串口数据的发送和接收功能,并将发送和接收的数据用$display 函数显示,通过显示信息判断RS232 总线数据传输系统是否正常,排除无关变量的干扰。

2.2 RS232 模块

RS232 模块可分为顶层模块、接收模块和发送模块,每个模块都可以作为时序型硬件木马的目标电路。本文采用接收模块作为本次硬件木马植入的载体,未植入木马的接收模块部分Verilog 代码如下:

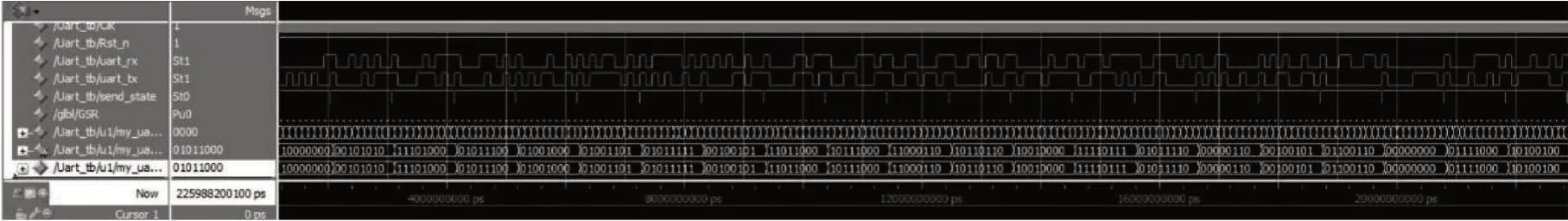

本文运用Modelsim 仿真反映RS232 总线集成电路数据传输系统能否正常运行。首先采用模拟串口数据收发器随机发送500 个数据,从图3 可以看出,RS232 总线通过接收模块接收到Rx_data 数据并通过发送模块发送Tx_data 数据,验证了RS232 总线集成电路数据传输系统能够正常运行。

图3 RS232 模块接收和发送数据仿真图Fig.3 Simulation diagram of RS232 module receiving and transmitting data

3 可逆时序型硬件木马的植入

通过特定的方法把微小恶意电路模块放入正常目标电路中的过程称为硬件木马的植入[16]。本文采用25 MHz 系统时钟为RS232 总线集成电路数据传输系统的内部环境,运用ISE 将常规型与可逆型硬件木马从RTL 层解析为Verilog 代码并插入到上述RS232 接收模块代码中,同时采用代号为num2 的4 位计数器,常规时序型硬件木马部分Verilog 代码如下:

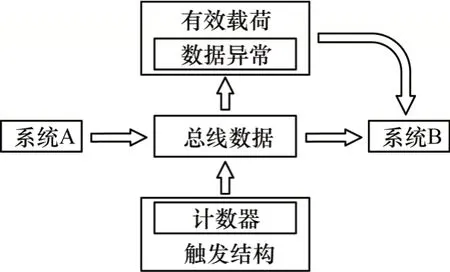

图4 所示为基于总线数据的硬件木马工作流程。本文在原有总线数据传输系统基础上添加了一个计数器和木马的硬件代码,当计数器值没有达到攻击者所设计的触发阈值时,木马在计数器内处于休眠状态,系统A 传输到系统B 的总线数据一切正常;当计数器数值达到设计触发阈值时,总线数据发生异常,系统B 接收到异常数据。

图4 总线硬件木马工作流程Fig.4 Working procedure of bus hardware Trojan

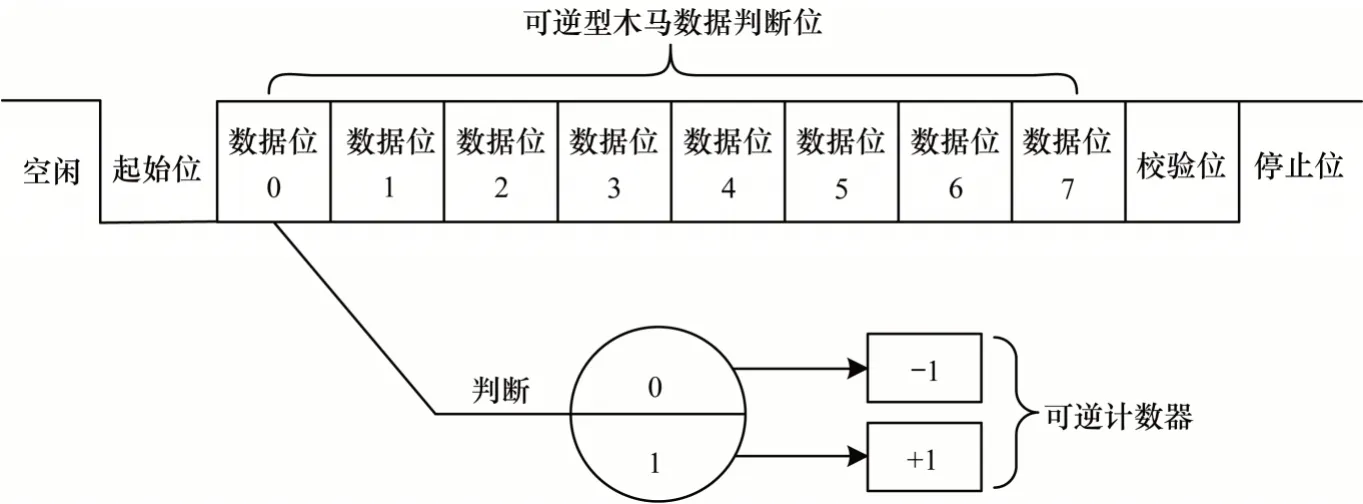

两种硬件木马根据总线数据判断位植入到总线集成电路的工作原理如图5 和图6 所示。

图5 常规时序型木马植入示意图Fig.5 Schematic diagram of conventional sequential Trojan horse implantation

图6 可逆时序型木马植入示意图Fig.6 Schematic diagram of reversible sequential Trojan horse implantation

从图5 可以看出,常规时序型硬件木马计数器只能在每帧数据完成传输时进行加1 的操作,此时木马处于静默状态,当计数器数值增加到所设置的触发阈值时,有效荷载被触发进而对总线数据进行攻击造成其异常,此时硬件木马属于攻击状态。

从图6 可以看出,本文设计的是一种基于总线传输数据内部的新型时序型硬件木马,可以根据数据传输情况先对数据最高位、最低位或者中间位进行“0”“1”判断,实现木马计数器数值变化的依据,体现了可逆型木马的灵活性。以本次选取传输的8 位数据为例,设置最高位为判断位,当最高位为“1”时,num2 计数器数值加1,当前最高位为“0”时,num2 计数器数值减1,当最高位为“0”且num2 计数器数值为“0”时,计数器数值保持不变。

4 激活验证与数据分析

为了保证实验数据的准确性,有关数据随机性问题本文采用Matlab 随机函数y=dec2bin(randi([0,255],500,1),8)生成一组500 个8 位0~255 的数据,将生成的随机数据复制在模拟PC 串口数据收发器来进行总线数据传输。为提供大量实验样本,本文利用本次搭建的总线数据传输平台完成了100 次数据传输,进一步减少实验数据的误差。

当两种木马计数器num2 触发阈值分别达到0,1,…,15 时,硬件木马有效荷载被触发,总线数据丢失并且输出数据00000000,每组数据需要先后16 次设置触发阈值,同时记录每次激活时已传输数据的个数。

为验证可逆型硬件木马的优越性,本文随机选取了1 组常规型和4 组可逆型数据在同位数计数器且同触发值情况下进行数据分析,如图7 所示。

图7 同触发阈值下两种木马已传输数据对比Fig.7 Comparison of transmitted data between two kinds of Trojans under the same trigger threshold

从图7 可以看出:

1)当触发阈值为0~3 时,可逆型组与常规型组已传输数据个数相差无几。

2)当触发阈值为4~15 时,常规型组已传输数据个数按正比例增长,但可逆型组显示为类指数型增长。

上述结果表明,在具有更多传输数据需求情况下,可逆时序型木马在有效荷载触发前可以传输更多数据,即具有更低的触发率,进而导致该木马在逻辑测试中难以激活,因此不能生成合适的特征向量被检测,具有更强的隐蔽性。

5 硬件木马的检测

影响传统硬件木马检测率的关键检测因素是硬件木马的大小和激活率[17]。

本文采用侧信道硬件木马检测技术对两种木马进行检测对比[18]。侧信道分析技术通过芯片在正常运行中的功耗[19]、时间延时[20]、电磁信息[21]或者热[22]进行监测,然后对采集的侧信道数据进行处理与分析,最后对目标样本进行对比来判断有无木马。

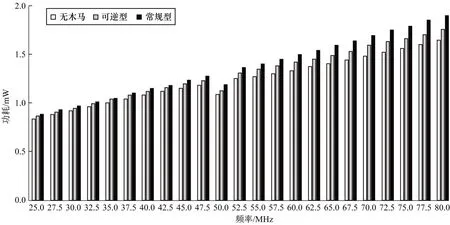

随机抽取3 组数据,设置能成功传输500 个总线数据的前提条件,运用ISE 通过PLL 锁相环改变总线传输环境,控制时钟频率为25 MHz,每增加2.5 MHz 分析一次被植入和未植入硬件木马电路的FPGA 功率,直至80 MHz,运用Xpower 对其进行功耗数据采集分析。如图8 所示,随着时钟频率的增加,常规型硬件木马比可逆型硬件木马与无木马的总线传输系统的功耗差异比数值要大,若更有效地检测可逆型硬件木马则需要测试更长的时钟周期。

图8 两种木马功耗仿真对比Fig.8 Simulation comparison of power consumption of two Trojans

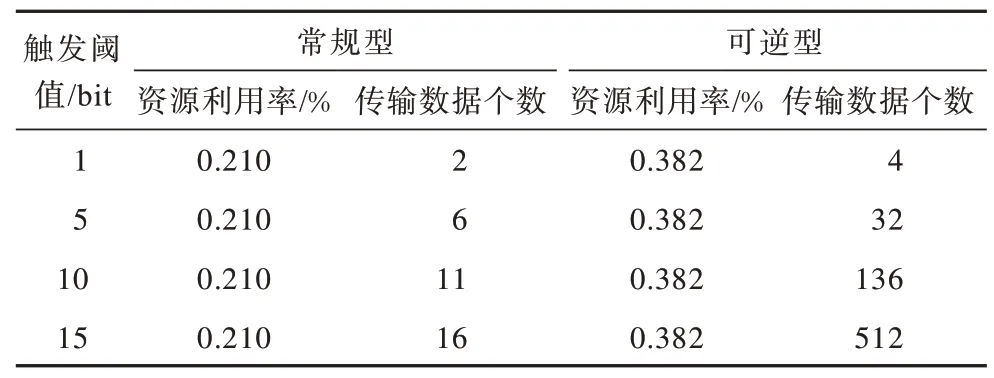

在两种硬件木马触发阈值相同的情况下,电路特性对比如表1 所示,可逆型比常规型slice 资源利用仅多出0.172%,但激活率却降低了近89%。当总线集成电路其他功能越复杂时,资源利用越多,则可逆型硬件木马相比同级别的常规时序型木马更有优势。

表1 两种硬件木马电路特性对比Table 1 Comparison of circuit characteristics of two hardware Trojans

6 结束语

RS 总线硬件木马的设计不仅是对现有硬件木马类型的补充,也是对硬件木马检测技术的加强。本文在常规时序型硬件木马的基础上,设计一种新型的可逆时序型硬件木马。该木马潜伏周期随触发阈值的增加呈类指数型增长,同时在完成一次触发时复位,可形成较常规时序型硬件木马更长的触发周期,并且在总线传输数据量越大的情况下隐蔽性越强。仿真结果表明,相对于基于时钟频率的时序型硬件木马,本文可逆型硬件木马基于总线内部数据,受时钟频率影响较小,进一步增强了隐蔽性。本文设计的可逆时序型木马在RS 系列总线集成电路防护领域具有广阔的应用前景,可为后续总线硬件木马的设计及研究提供支持。