一种多功能雷达干扰信号发生设备

2021-02-23王守权高伟亮李宝鹏

王守权,高伟亮,李宝鹏,田 涛

(海军航空大学青岛校区, 山东 青岛 266041)

现代雷达所处的电磁环境复杂,周围存在着诸多有意干扰和无意干扰信号,如何确保雷达在复杂电磁环境中发挥应有的作战效能是雷达抗干扰训练要解决的重点问题[1 -3]。以矢量信号收发仪为开发平台,利用上位机+FPGA技术开发了一种便携式多功能雷达干扰信号发生设备(以下简称雷达干扰设备),将SDIF(序列差直方图)信号分选算法和DRFM(数字存储技术)技术相结合,实现了雷达信号侦察、雷达干扰信号生成、雷达测试功能标校等功能。雷达干扰设备可作为雷达训练的配套设备,为雷达提供贴近实战的电磁干扰环境,检验评估雷达装备的抗干扰性能,验证标校雷达的探测性能,对雷达作战效能的发挥有十分重要的意义。

1 功能需求

复杂电磁环境下开展雷达装备抗干扰测试,雷达干扰信号发生设备产生的干扰信号样式要多;对不同体制雷达的干扰效果要理想,干扰实施操作要灵活。因此,系统设计了3种主要功能:雷达信号侦察、雷达干扰信号生成、雷达标校。与行业领域同类型设备相比[4-6],增设了雷达信号侦察和雷达标校功能,使得系统应用范围和干扰效果得到了提升。

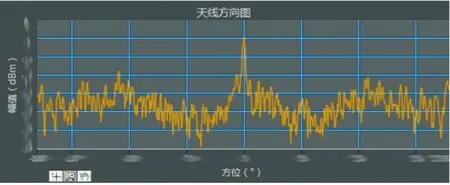

系统可自动侦察当前电磁环境中存在的现有各种体制的雷达信号,分析其时域、频域、PDW(脉冲描述字)参数,显示信号的波形图、频谱图、天线方向图等信息,并根据雷达参数数据库对辐射源类别进行识别。

根据侦察雷达信号参数情况,可自动或人工设置干扰目标速度、加速度、功率、目标个数、航迹等参数,实时产生多种类型的雷达干扰信号,主要包括:多通道目标干扰、密集假目标干扰、压制干扰、示样干扰、间歇干扰、距离拖引和目标分离。

利用雷达与干扰机的位置确定相对距离、方位,通过对比系统干扰航迹数据和雷达记录的虚拟航迹数据,对雷达的定位、测距性能进行验证和标定,以消除由于维修、元件老化、设备变形等因素造成的零位偏差。

2 系统方案设计

2.1 硬件架构设计

系统硬件采用为PXIe-5644R VST主体模块,搭载FPGA功能架,5644R VST内含Xilinx Virtex-6 FPGA,可使用LabVIEW FPGA 对模块进行编程,以实现快速测量、闭环测试和复杂算法工程开发[7-8]。如图1所示,系统硬件主要由NI PXIe-5644R VST、零中频发射接收机、模/数转换器、环形器、喇叭天线组成,主要分为雷达信号侦察和干扰信号生成两大功能模块,雷达侦察的信号参数可为雷达干扰信号生成提供先验信息。将短时傅里叶变换(Short-Time Fourier Transform,STFT)、DRFM、天线方向图生成、PDW获取、多普勒信号调制等功能模块放到FPGA上实现,充分发挥FPGA高效高速,定时精准的优点。将PDW显示、信号分选、地图功能、信息存储、干扰数据生成、雷达标校等功能放在上位机上实现。

图1 硬件设计方案框图

系统硬件工作功能流程如下:被侦测的雷达信号经天线接收后传输至雷达目标模拟系统,经零中频接收机、经下变频后被采样存储,得到I/Q基带信号,经ADC(模数转换)、数字均衡、数据抽取后进行计算和存储。发射时通过DMA、寄存器与干扰设备控制软件进行数据交互控制,根据软件生成的干扰数据进行时延控制、幅度和多普勒调制处理,通过数字差值、数字均衡、DAC(数模转换),经零中频发射机上变频为射频干扰信号,经RF-OUT端口发射出去。FPGA使用Xilinx IP实现FFT运算,通过自定义IP实现数字信号处理、DRFM等功能。

2.2 软件功能设计

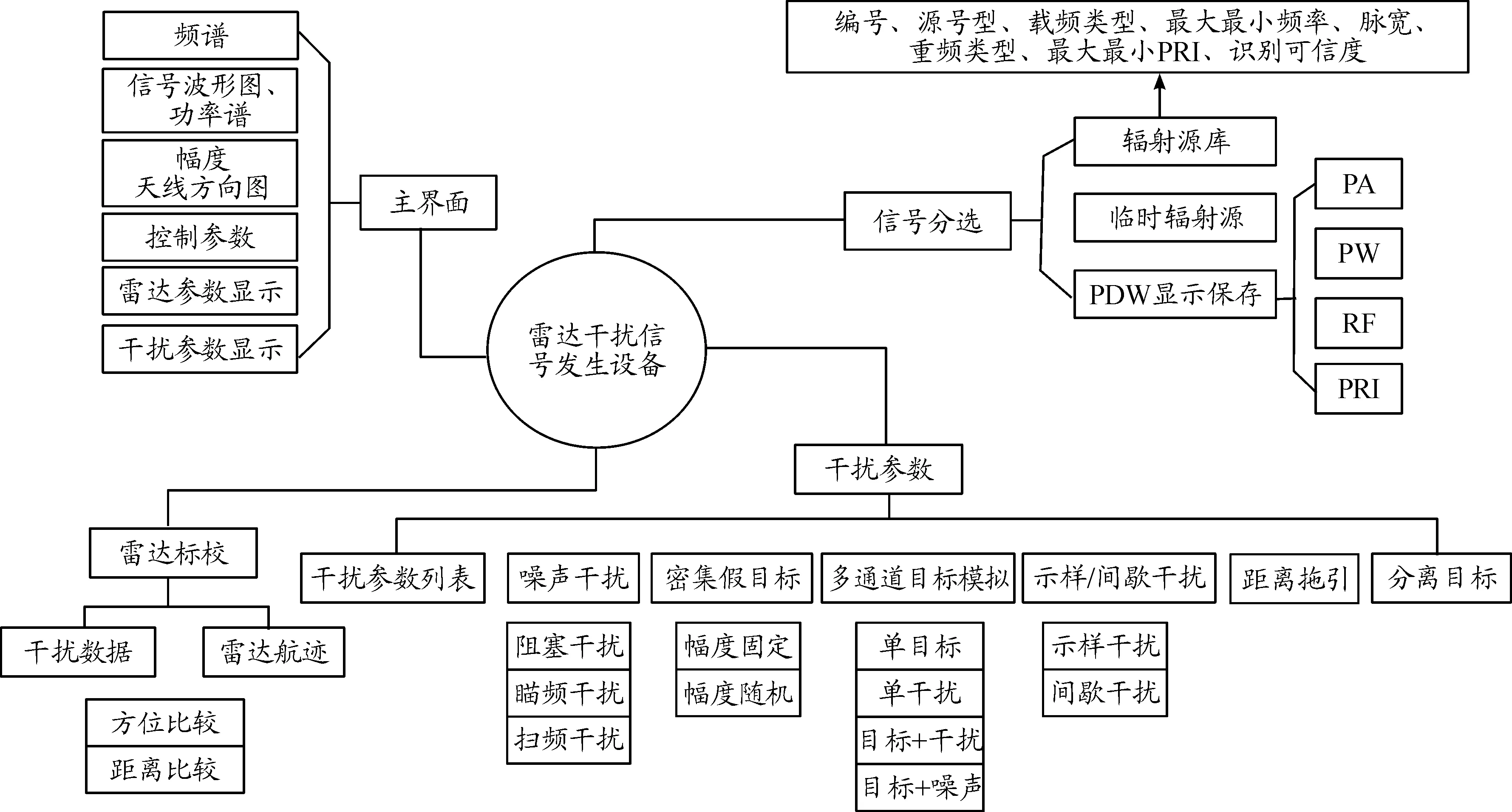

上位机软件用来设置和显示侦察分选、干扰控制、信号波形、天线方向图等参数信息。如图2所示,系统可显示和保存被侦测信号的PA、RF、PW、PRI等PDW数据,以便进行更好的雷达特性分析和辅助信号分选。将信号分选结果存入临时辐射源表格中,可选中识别可信度高的雷达参数存入辐射源库,也可从外部文件中直接导入雷达参数,不断丰富辐射源库。当干扰已知雷达时,可以跳过侦察,直接从辐射源库中选定该雷达参数进行干扰操作,使操作更加地高效便捷。

设备可以释放噪声干扰、密集假目标、多通道目标干扰等干扰多种类型的干扰。其中,噪声干扰主要包含阻塞干扰、瞄频干扰、扫频干扰等3种样式;密集假目标干扰的点迹幅度可以设置为固定或随机,有3个通道可以释放密集假目标,每个通道最多可以释放255个运动的点迹;多通道目标干扰可以释放单目标/多目标、单干扰/多干扰、模拟目标+干扰,模拟目标+噪声等多种样式的干扰;示样/间歇干扰可以释放目标+示样干扰或者间歇干扰;距离拖引干扰可以模拟目标被雷达跟踪后,释放假目标摆脱雷达的跟踪;分离目标可以模拟目标到达设定距离后释放假目标,用于模拟敌机攻击目标雷达的场景。

图2 软件设计方案框图

3 信号侦察与干扰实现方法

3.1 雷达信号侦察与分选

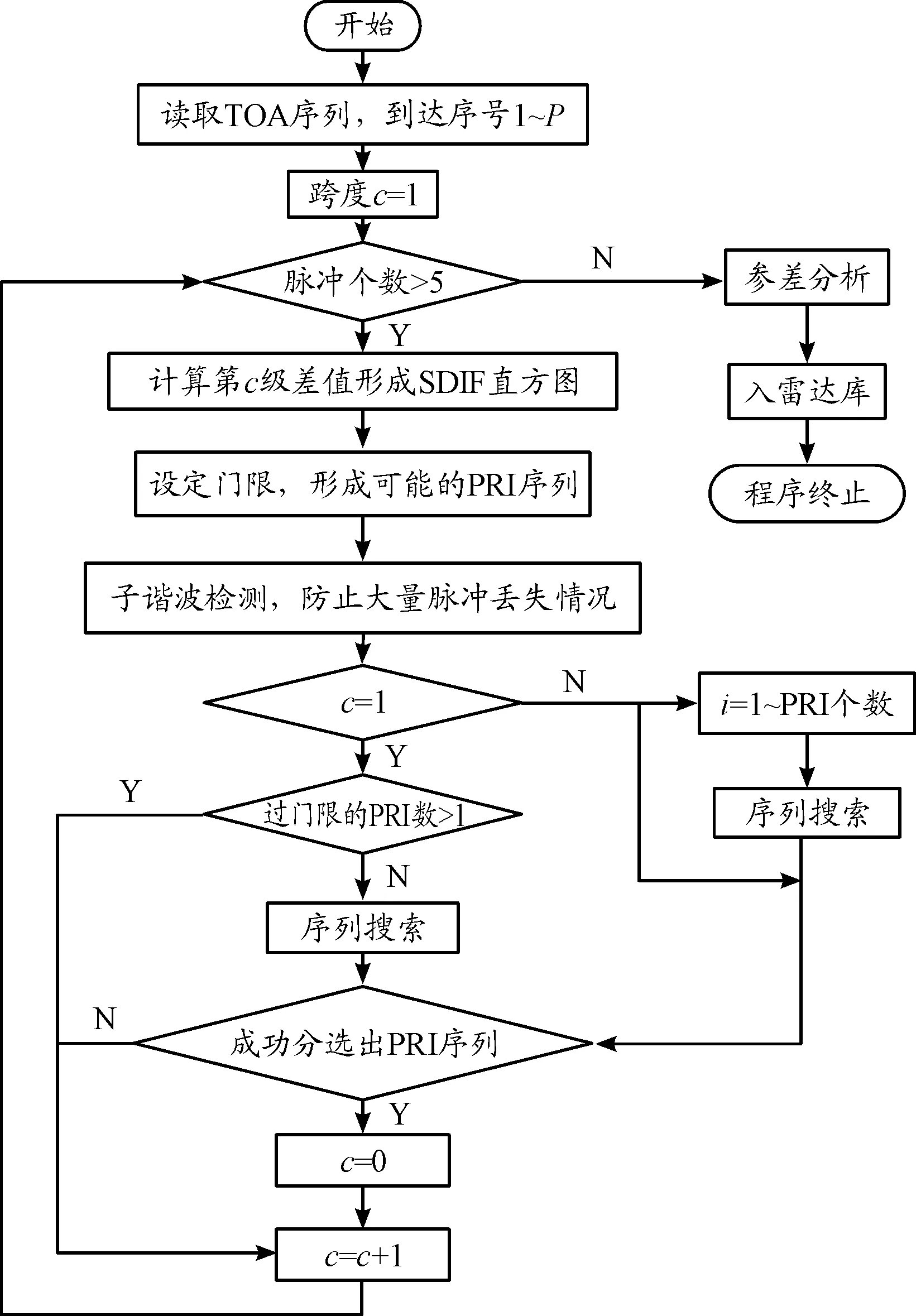

信号分选是雷达侦察的关键技术,需要从截获的大量脉冲信号流中分选出有用的信号,由于目前空域中辐射源种类非常多,且雷达信号形式多样,使信号分选这一过程非常复杂[9]。考虑到算法的计算复杂度及分选效果,选用算法复杂度低、性能优异的SDIF算法作为雷达信号分选算法。SDIF算法由PRI测定及序列检测两部分组成,PRI的测定时SDIF算法的关键。如图3所示,算法基本工作过程如下。

计算相邻两个脉冲的TOA之差构成第一级差值直方图,计算检测门限;子谐波检验后将所有超过门限的值看作是可能的PRI值进行序列检索。若成功地分离出脉冲序列,则重复此过程,直到分离出所有的脉冲列或剩下少于5个脉冲为止。若序列检索不能分离出脉冲序列,则计算下一级差,设立新门限,重复整个过程,最后完成参差鉴别。SDIF门限计算方式为:

(1)

式(1)中:E是总的脉冲数;N是直方图总的格数;c是差值级数;x和k是常量系数,其值是由经验决定的,x、k的值为小于1的正数。

图3 SDIF信号分选算法流程框图

雷达侦察与分选实施流程如图4所示。干扰控制软件通过DMA获取FPGA端的TOA(脉冲到达时间)数据,用于信号分选。通过SDIF算法高效地完成信号分选后,FPGA根据信号分选的结果进行STFT,计算雷达信号频率、带宽、幅度、类型等信号参数,将雷达信号参数放入临时辐射源表格,辐射源库可根据后面分选出的相似结果不断更新,可以将识别可信度高的雷达参数存入辐射源库,也可以将原有的雷达辐射源参数导入辐射源库。侦察分选结果以PDW的数据形式保存。为了更好实施干扰,可以从临时辐射源表格或辐射源库中选定雷达参数,为干扰提供射频相关的参数。

图4 侦察实施流程框图

3.2 干扰信号生成

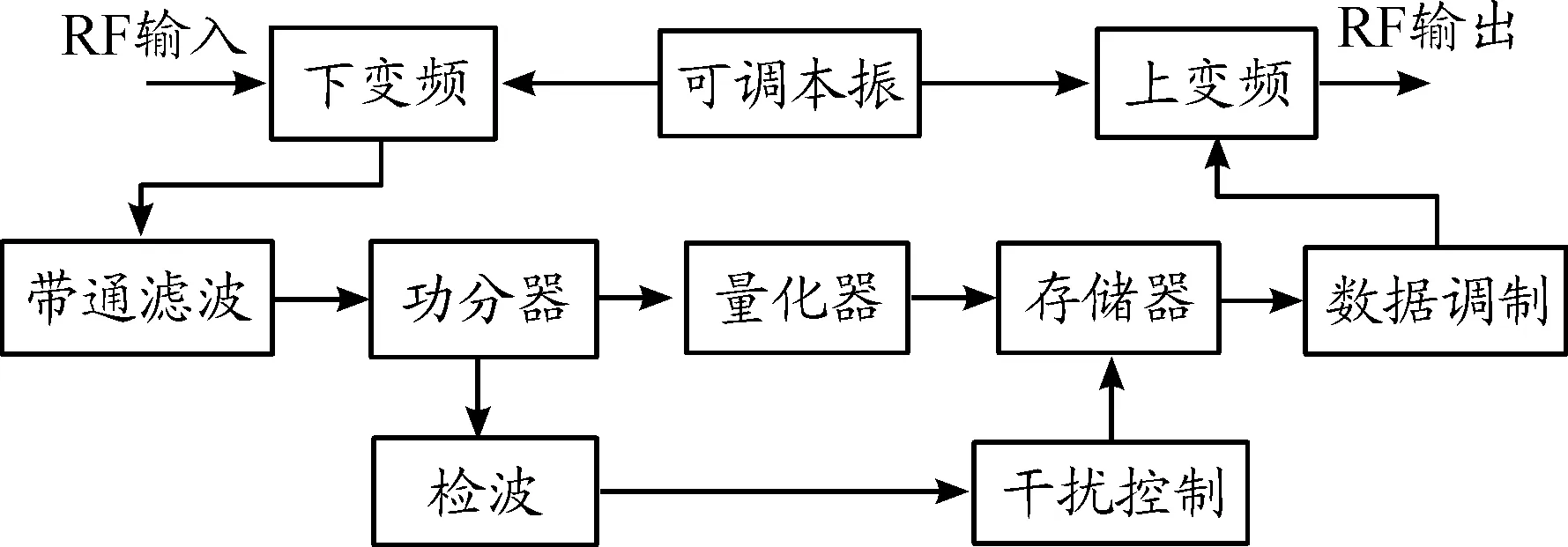

干扰信号生成采用DRFM技术机制,DRFM工作原理如图5所示,首先对侦察的雷达信号进行量化存储,然后在干扰信号生成阶段,通过对存储的雷达信号参数进行调制并转发出去,当被干扰雷达对接收到的干扰信号进行相干处理时,会得到较高的增益,形成假目标尖峰,从而欺骗并扰乱雷达的检测和跟踪[10-11]。

由于系统对信号存储转发需要一定的处理时间,因此DRFM对当前脉冲周期存储的信号延迟一个或几个脉冲周期后,再转发出去并形成干扰回波。DRFM通过对接收到的射频信号进行高速采样、存储、变换处理和重构,实现对信号捕获和保存的高速性、干扰技术的多样性和控制的灵活性。

图5 DRFM工作原理框图

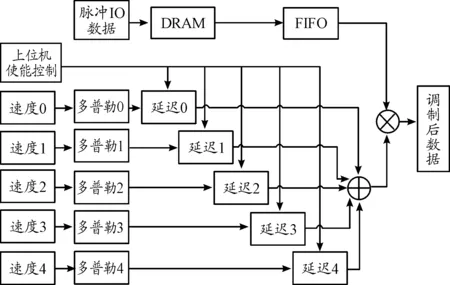

DRFM工作方式如图6所示,系统进行DRFM时,判断脉冲上升沿到来后,开始将脉冲的I/Q数据存入DRAM存储块,脉冲到来的TOA以及PW写入寄存器。上位机将干扰数据通过DMA传输到FPGA,FPGA解析参数,提取每个干扰数据的速度信息,生成多普勒数据。FPGA中用一个U64的计数器控制时间,根据速度及每个干扰数据设置的距离,计算需要延迟多少计数,与脉冲到来的TOA相加,当计数器值计到该值时,产生触发信号。采用握手的方式从DRAM中读取脉冲I/Q数据,并存入FIFO中,取出FIFO中的数据与多普勒数据调制后发出。

图6 DRFM工作方式框图

干扰实施主要分为一般干扰、侦察干扰2种方式。一般干扰是指配置好干扰参数后手动释放干扰,侦察干扰是指配置好干扰参数后,先进行侦察,锁定电磁环境中的雷达后,再释放干扰。不同类型的干扰实施设计流程如图7~图9所示,具体过程大体相似,分为以下几个步骤:在上位机配置距离、速度、加速度、上限速度、功率、假目标个数等参数,FPGA接收配置参数后,通过延迟、多普勒调制、幅度控制、脉冲存储后进行重复转发技术生成干扰信号。

图7 噪声干扰设计流程框图

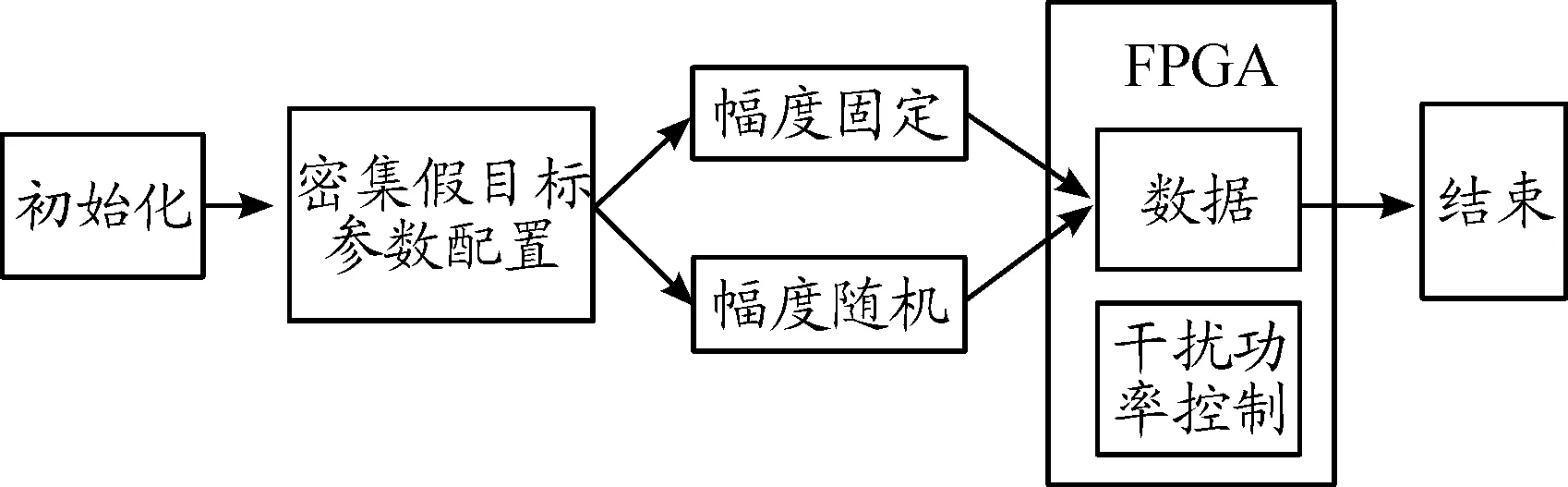

图8 密集假目标干扰流程框图

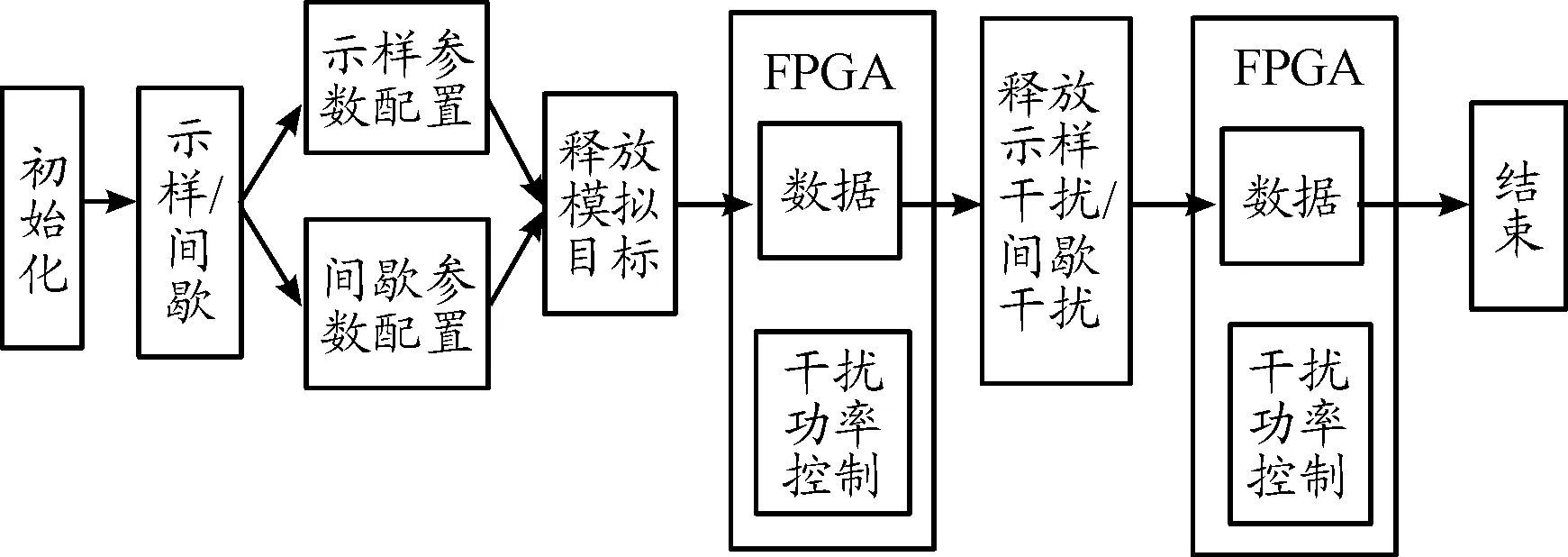

图9 示样/间歇干扰流程框图

距离拖引干扰实施流程如图10所示。配置目标与干扰参数后,通过定时控制目标与拖引干扰的释放时机,使目标在运动过程中,按规律释放拖引干扰,不断重复该过程,直到退出距离拖引干扰。FPGA接收上位机配置目标和干扰通道的距离、速度、加速度、上限速度、功率、定时等参数,通过延迟、多普勒调制、幅度控制、脉冲存储转发技术,按规律实现距离拖引干扰。

分离目标干扰实施流程如图11所示,配置目标与干扰参数后,通过距离控制子目标干扰的释放时机,使目标在运动过程中,在指定地点释放子目标干扰,结束后,子目标消失。FPGA接收上位机配置目标和干扰通道的距离、速度、加速度、上限速度、功率参数,通过延迟、多普勒调制、幅度控制、脉冲存储转发技术,实现分离目标干扰。

图10 距离拖引干扰设计流程框图

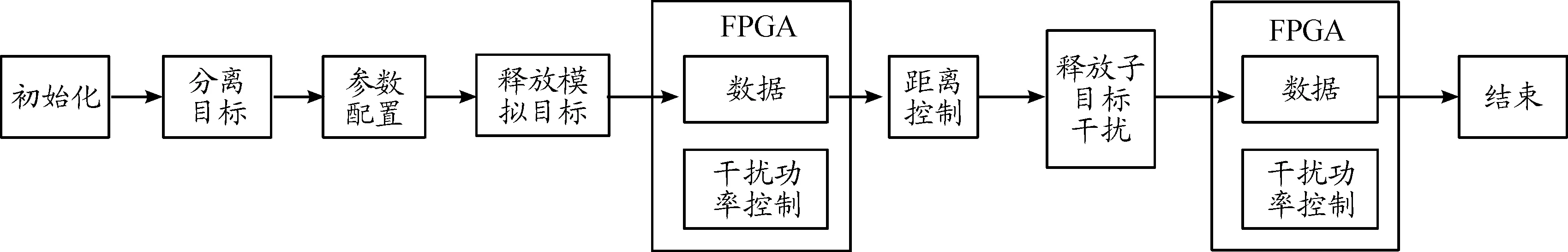

图11 分离目标干扰设计流程

4 系统测试

为测试雷达干扰设备性能,选用目标雷达作为配试设备进行相关技术指标与主要功能测试。系统主要射频参数测试情况如表1所示。

表1 射频参数测试值

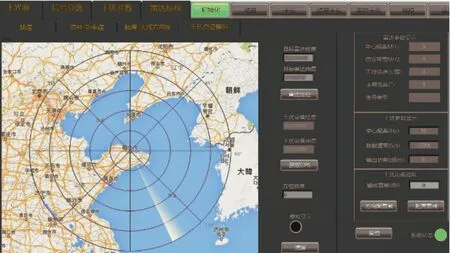

设备人机交互主界面如图12所示,可以进行参数设置和数据显示选择等操作。侦察的雷达信号PDW参数如图13所示,天线方向图侦测图如图14所示。设备对被测雷达实施干扰,相对于其他类型的干扰设备[12-15],压制干扰系数提高大于10%,欺骗成功概率大于20%,干扰实施时间降低3~5 s。以上测试结果充分验证了该设备的实用性和有效性。

图12 设备主界面

图13 PDW参数显示界面

图14 天线方向图侦测图

5 结论

为了给雷达设备抗干扰测试提供理想的复杂电磁信号环境,以VST为硬件平台开发设计了一种多功能雷达信号发生设备,应用SDIF信号分选技术、DRFM干扰生成技术,实现了高精度的雷达信号分选和干扰信号生成功能,设备还可以利用干扰数据实现雷达标校功能。系统测试结果表明,系统射频指标高,对雷达信号侦察截获概率高,分选结果正确率高,产生了多种样式的干扰信号,能有效地对雷达实施各种样式干扰。