电流模控制高效同步DC-DC 芯片设计

2021-01-16陈文琦

陈文琦,张 涛,刘 劲

(武汉科技大学 信息科学与工程学院,湖北 武汉 430080)

当今,电源管理芯片的设计和研究是一个非常热门的研究点。随着电子设备逐渐趋向于小型化和智能化,DC-DC 转换器因其低成本和高效率越发受到青睐[1-2]。DC-DC 转换器的优点是效率高、可以输出大电流、静态电流小,缺点是输出纹波大、稳定性较差[3]。电源管理芯片一般采用电压模式控制和电流模式控制。电压模式结构简单但输出纹波较大且输出响应较为缓慢;而对于电流模式而言,输出响应快、消除延迟且增益带宽大,但其需要高性能的电流采样电路才能达到快速响应的目的。同时小型化电子设备中不仅需要芯片面积尽可能小而且在电量一定的情况下尽可能地延长工作时间,在一些精密电子设备中对电源清洁度有非常高的要求。这就需要提高电源转换效率的同时尽量降低纹波电压的大小。针对上述问题本文设计了一款同步高效的降压型DC-DC 电源芯片。该芯片采用华润上华0.18 μm工艺,采用峰值电流控制模式并设计了带补偿的电流采样电路。运用死区缓冲技术设计了死区缓冲器,使得芯片能达到高转换效率。

1 整体系统框架以及工作原理

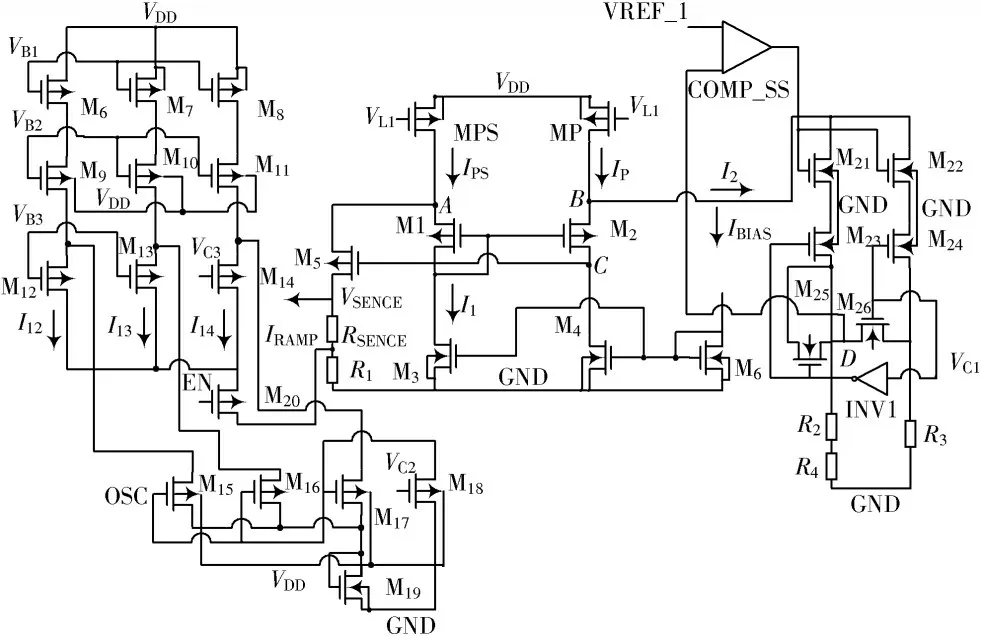

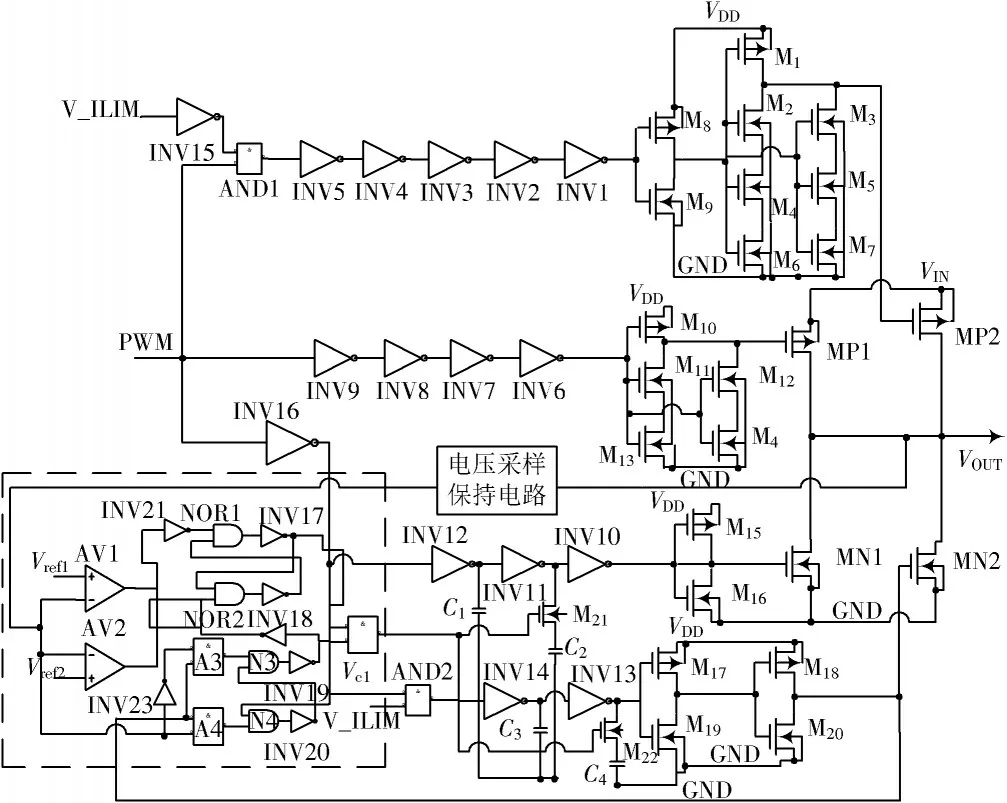

如图1 所示为所设计的降压型DC-DC 电源芯片的内部结构以及外围电路。内部应用电流模式控制的电压外环与电流内环的双环控制方式产生PWM,主要由带隙基准模块、电流检测模块、误差放大器模块、电流补偿模块、逻辑控制模块、软启动模块以及其他保护电路组成[4]。其中,误差放大器模块、电流补偿模块分别是电压外环与电流内环的核心。基本工作原理是在开始阶段软启动电路,使得电路缓慢启动,误差放大器通过反馈端得到变化的电压与带隙基准产生的参考电压进行比较得出的误差放大信号,与带电流补偿的电流采样模块所产生的信号两者再进入比较模块后产生占空比可变的PWM 信号,最后经过逻辑驱动电路驱动功率管,控制其关断从而实现稳定输出的目的。

图1 芯片的内部结构以及外围电路

在外围电路中由于输出电容的等效电阻ESR 与等效电感ESL 是产生较大的纹波电压的主要原因,目前ESL 的影响几乎可以忽略不计。因此在外围电路的选择中选取了ESR 小的陶瓷电容,并采取并联电容的形式降低ESR 来达到低纹波电压的目的。为了进一步减小输出纹波并增加瞬态响应,增加了前馈电容C1,COUT是滤波电容,同样是为了降低输出纹波大小。

2 主要模块设计及分析

2.1 电流检测电路

电流检测电路是电流模式电流内环的核心部分,其作用是对片外电感电流的变化进行准确及时的采样,以确保系统的正常工作。如图2所示,与传统的电流采样电路不同,本文设计了电流补偿并在B点增加了反馈回路。该电路的功率管MP 与采样管MPS 镜像比为M∶1 进行电流采样,采样管中的电流为功率管的。采样精度为:

式中:电流为微安级;M 值远大于1。可知该结构采样精度高,且电路结构简单。

M1,M2在相同的偏置电流下相互匹配,M1,M2和M5构成负反馈使B 点的电位与A 点电位相同。为了防止M5的偏置状态因为电流I1变化而产生变化,在B,C 两点引入系统失调导致采样精度下降[5],因此设计了由NMOS 管M21~M26,反相器和比较器构成的反馈回路,来消除系统失调。其工作原理是:当采样电流IP变大时,VC1取高电平,使得M24导通,此时D 点为低电位,比较器输出高电平,支路导通抽取电流使得M1,M2偏置电流相等,同时保证M5的偏置状态稳定。同理,当采样电流IP变小时,VC1取低电平,使得M23导通,此时D 点为高电位,比较器输出低电平,支路逐渐停止抽取电流。

图2 电流检测电路

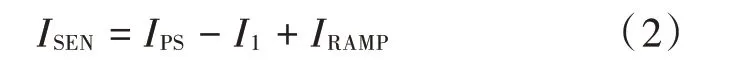

为防止采样电路在轻载状态时MOS 管M5因为电流减小而进入亚阈值区,导致环路延迟使得电路采样效果变差,在输出端引入了补偿电流。使得此时流过输出端所在支路的电流为:

为了保证在轻载状态下也能实现高速高精度的电流采样[5],应保证IRAMP略大于I1,因此将产生补偿电流的MOS管M12,M13和M14的宽长比设计为,补偿电流为:

2.2 误差放大器模块

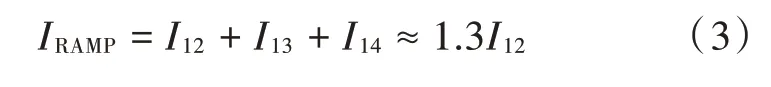

误差放大器模块作为电压外环是产生PWM 控制波的主要模块,该误差放大器采用两级栅极驱动运放结构。如图3 所示,M1~M4和M6~M11分别为差分放大器的第一、二级放大结构。

图3 误差放大器

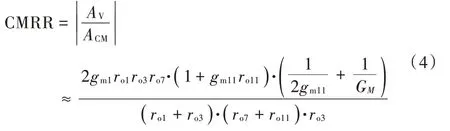

出于对共模抑制比的考虑,将使用多个大宽长比MOS 管并联的方式来减缓失配对共模抑制比的影响。C2是密勒补偿电容,利用电容倍增技术将电容与全差分放大结构相结合,在输出端与误差放大器之间构成环路补偿,有利于增强环路稳定性。密勒补偿电容的特点是能将两个极点分裂开,使主极点向原点方向移动[6]。目的是使它们远离复平面的原点,从而提高相位裕度。经整理得共模抑制比为:

误差放大器的补偿网络由电阻和电容组成,经计算,确定电容的大小在微法级。在版图中,大电容所占面积通常很大,为了减小补偿网络所占芯片面积的同时不影响补偿网络的效果,因此本文设计采用电流模的电容倍增技术利用小电容C3和电流镜构成的倍增电容与电阻R2组成补偿网络。

2.3 逻辑驱动电路

在DC-DC 转换器中,主要采用同步整流技术来提高转换效率[6]。影响效率的有静态电流损耗、导通电阻损耗、开关损耗以及驱动损耗。死区时间的长短取决于负载电流和输入电压。高低侧功率管的死区时间如果不合适则会带来额外的损耗,造成芯片效率的下降。如果死区时间过长,电感电流会让低侧开关体二极管被正向偏置,并且输出端被拉低至负二极管正向电压,这导致输出电流和开关频率增加,造成损耗增加。而如果死区时间不足,可靠性下降可能会导致高低侧功率管同时导通从而危害整个电路。本文利用死区缓冲技术设计了死区时间可切换的死区缓冲器来避免输入电压的变化,导致死区时间不合适所带来的额外损耗,死区缓冲器见图4。

1)将死区时间设置为低电压,当输入电压变化时,避免在高电压下的不同负载电流死区时间过小对效率产生的影响,此时只有将死区时间延长,转换器才具有更高的效率。本文设计如虚线框中由窗口比较器AV1与AV2,电压采样保持电路和锁存器构成的死区时间控制电路。其中,电压采样保持电路是由运放电容组成。当输入电压由低变高时,VC1变为高电平,该缓冲器通过采样保持电路对低侧功率管的电压进行采样,将采样值通过参考电压Vref1和Vref2设置的最佳死区时间(约为50 mV)的目标窗口比较器,若采样值在目标窗口内,说明死区时间合适保持原状态即可。若采样值在目标窗口外,说明死区时间较短,控制电路控制开启NMOS 开关管来增加电容C2和C4,稍稍延长死区时间。当输入电压由高变低时,为避免死区时间过长,则关断电容C2和C4恢复原死区时间。

2)在DC-DC 转换器中,因为电感电流的作用,关断损耗通常是大于开通损耗,功率管的导通与关断时间与反相器的宽长比成反比,因此将缓冲器的NMOS 管采用多个大宽长比串联的方式,PMOS 管采用多个大宽长比并联方式增加MOS 管的宽度,加快高电平的产生,有利于提高关断的速度,从而有效降低关断损耗。将高低侧的功率管各改为一大一小并联,MP1 和MP2 在启动时有约0.7 ns 的延时,其作用是为了防止芯片启动时产生瞬时大电流对电路的损害。当过流保护模块的输出V_ILIM 为高,此时只有大尺寸功率管关闭,小尺寸功率管可以正常工作,相比于同时关闭,这样能降低一定的开关损耗。

图4 死区缓冲器

功率管在版图设计上采用曲栅结构,版图中晶体管的栅极采用平缓的大角度的弯曲方式延伸,晶体管的栅极采用135°的弯曲方式,能有效避免90°局部雪崩击穿现象的发生。这样的版图结构能够减小芯片的面积,提高芯片在极端条件下的稳定性。

3 仿真与测试

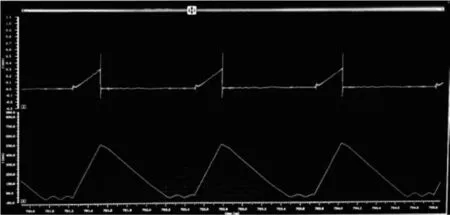

本文在Cadence 软件中搭建模拟仿真平台,选用华润上华0.18 μm 工艺,采用图1 外围电路对DC-DC 转换器的内部模块和转换系统进行了仿真。输入电压为5 V,输出电压为1.8 V,负载为18 Ω。仿真误差放大器的共模抑制比CMRR 为136 dB,增益为55 dB,相位裕度为51°。如图5 所示,采样电路在轻载下的仿真结果从上到下为采样电流和电感电流,响应时间约为13 ns,表明响应速度达到要求。

图5 电流检测电路仿真结果

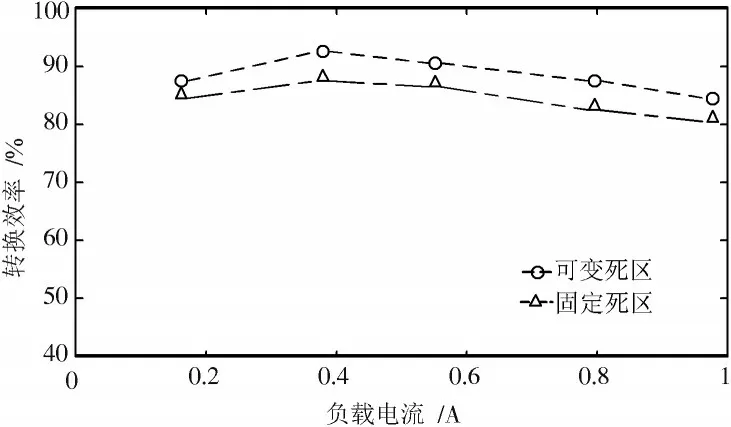

如图6 所示,在输入电压为4 V 的条件下采用死区时间可调的死区缓冲器与固定死区时间下负载电流与转换效率的关系对比,提高了约2%的效率。

图6 负载电流与转换效率的关系

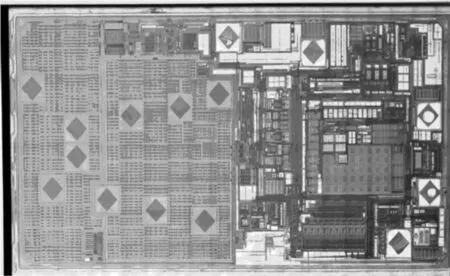

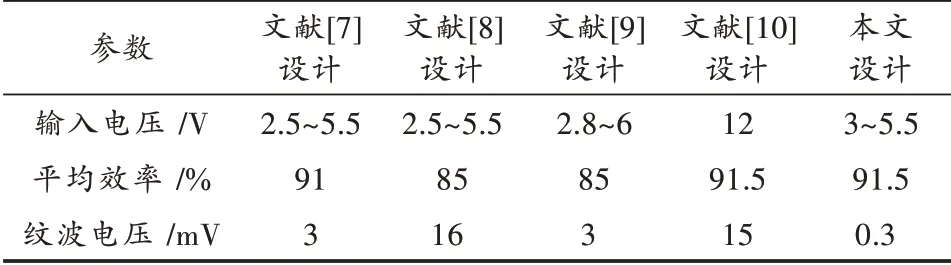

经测试在输入电压为5 V,电感为2 μH 的条件下,输出电压为1.8 V,负载电流为2 A。经过1.1 ms 左右,VOUT达到稳定,输出纹波大小仅为0.3 mV。图7 为芯片显微照片,面积约为1.5 mm×0.8 mm,其中,误差放大器面积约为0.045 mm2。表1 是对样品的部分测试结果。表2 是与前人工作比较的结果。

图7 芯片显微照片

4 结 论

本文采用华润上华0.18 μm CMOS 工艺设计一款电流模控制的同步高效低纹波输出的降压型DC-DC 电源芯片。该芯片通过采用电流控制技术和死区时间可调缓冲器,加快了响应速度和提高了转换效率,应用电容倍增技术缩小了芯片模块面积。通过仿真与测试结果表明,芯片输入电压在3.3~5 V 的范围内,芯片响应速度快,平均转换效率为91.5%,峰值功率最高可达95.2%,输出纹波大小仅为0.3 mV,达到了预期目标。

表1 部分参数测试结果

表2 与前人工作比较的结果