基于千兆以太网的弹载数据采集系统设计

2020-12-16张少芳李献军王月春杨立云

张少芳,李献军,王月春,杨立云

(1.石家庄邮电职业技术学院, 石家庄 050021;2.河北科技大学信息科学与工程学院, 石家庄 050018)

随着军工领域创新科研能力的不断提升,导弹的杀伤力与作战范围不断提升,对新型导弹的测试手段提出更高的要求。弹载数据采集系统也伴随着导弹的发展越来越智能化、复杂化。系统在导弹飞行过程中所需记录的数据种类和容量越来越多,对导弹的飞行姿态等性能参数评价更加准确。弹载数据记录仪的主要作用是对各类参数的采集与存储,在试验结束后能够完整的回收,然后通过上位机对采集的数据进行提取,通过试验结果判断是否满足设计指标要求[1-4]。因存储容量的不断增加,如何将大容量数据更高效的传输到上位机是系统设计的关键。现阶段的记录仪与PC机的通信接口主要有USB、CAN总线、PCI总线和以太网通信等。USB是较为常用的一种串行总线,其中USB2.0的数据传输速率可以达到480 Mbit/s,其主要的缺点是传输距离较短,限制设备间的连接位置;

CAN总线主要用在车载设备间的通信,抗干扰能力强,数据传输准确率高,但传输速率较低,不能接入因特网;PCI总线具有较高的传输速率,可达266 MByte/s,但PCI设备在上电状态下不能随意插拔[5]。以太网通信在局域网中最为常见,根据传输速率可分为百兆、千兆和万兆以太网,其突出特点是数据传输速率快,可大大缩短大容量数据的传输时间[6]。

本文选用千兆以太网通信接口,以FPGA为主控芯片,设计实现对弹上16路模拟信号和8路数字信号采集存储的弹载多通道数据记录仪。针对导弹飞行试验结束后需对数据快速回传的要求,重点开展了以太网MAC层实现和CRC差错校验研究。

1 系统整体控制逻辑设计

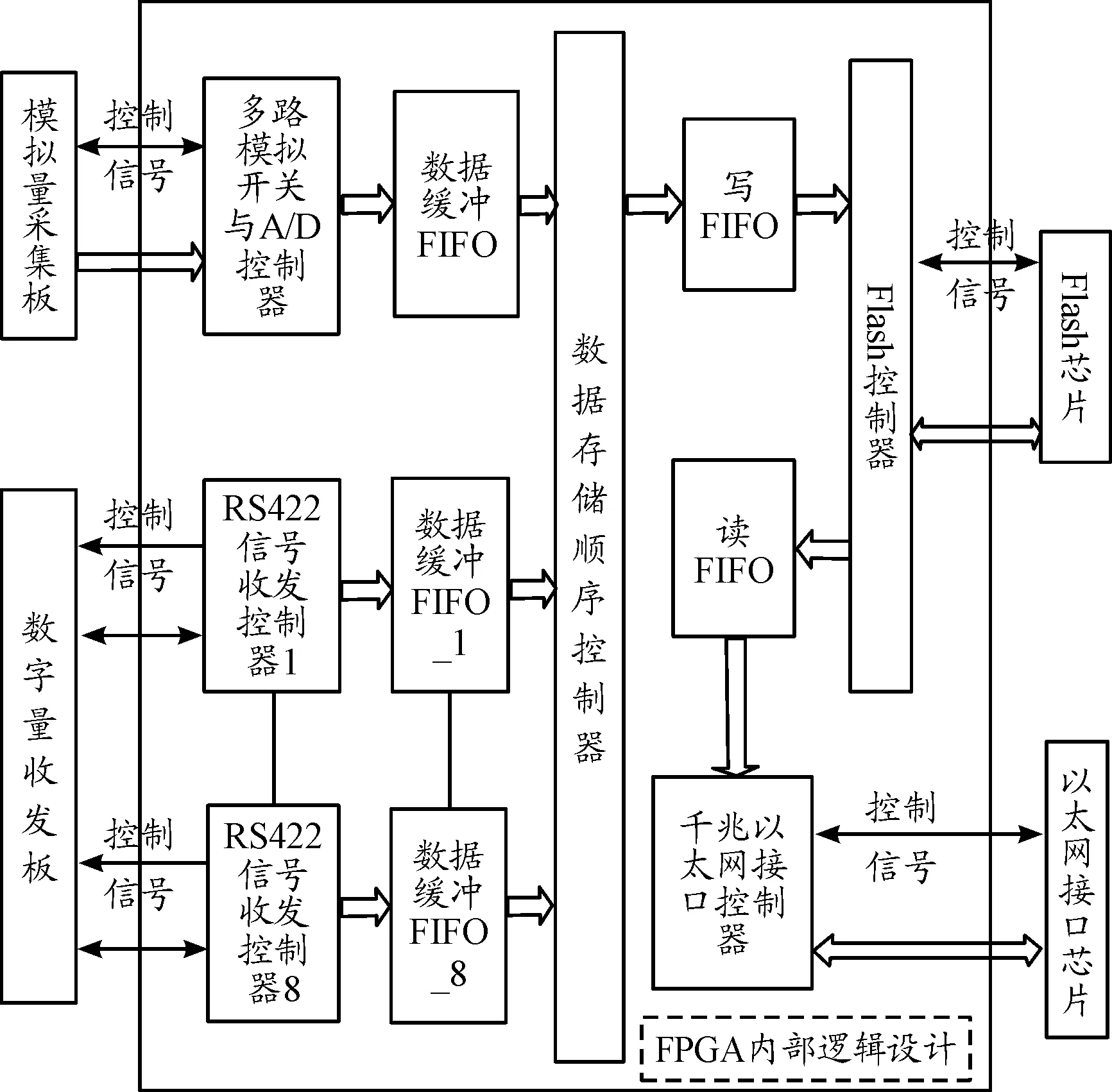

系统主要完成对弹上各类型传感器模拟信号、数字接口信号的采集存储,在飞行结束后通过以太网接口对数据进行回读并分析。根据系统工作流程,FPGA中需要完成的控制逻辑如图1所示。

本系统利用千兆以太网实现数据传输时主要涉及到TCP/IP模型中的传输层、网络层和数据链路层,其中,以太网MAC层的数据处理和传输层、网络层的相关协议通过FPGA编程实现,此外,采用物理层芯片实现PHY层的功能。在PHY芯片选型时,要充分考虑封装、功耗和外部接口等因素,本系统选用了Realtek的RTL8211EG,该芯片已得到广泛应用,各方面计数较为成熟,外部硬件电路配置简单,降低了开发难度,并且支持RGMII、GMII、MII等物理接口,可实现物理层与上层数据间的通信,符合IEEE802.3标准[7-8]。

图1 FPGA整体控制逻辑框图

2 以太网通信关键技术

2.1 MAC层控制

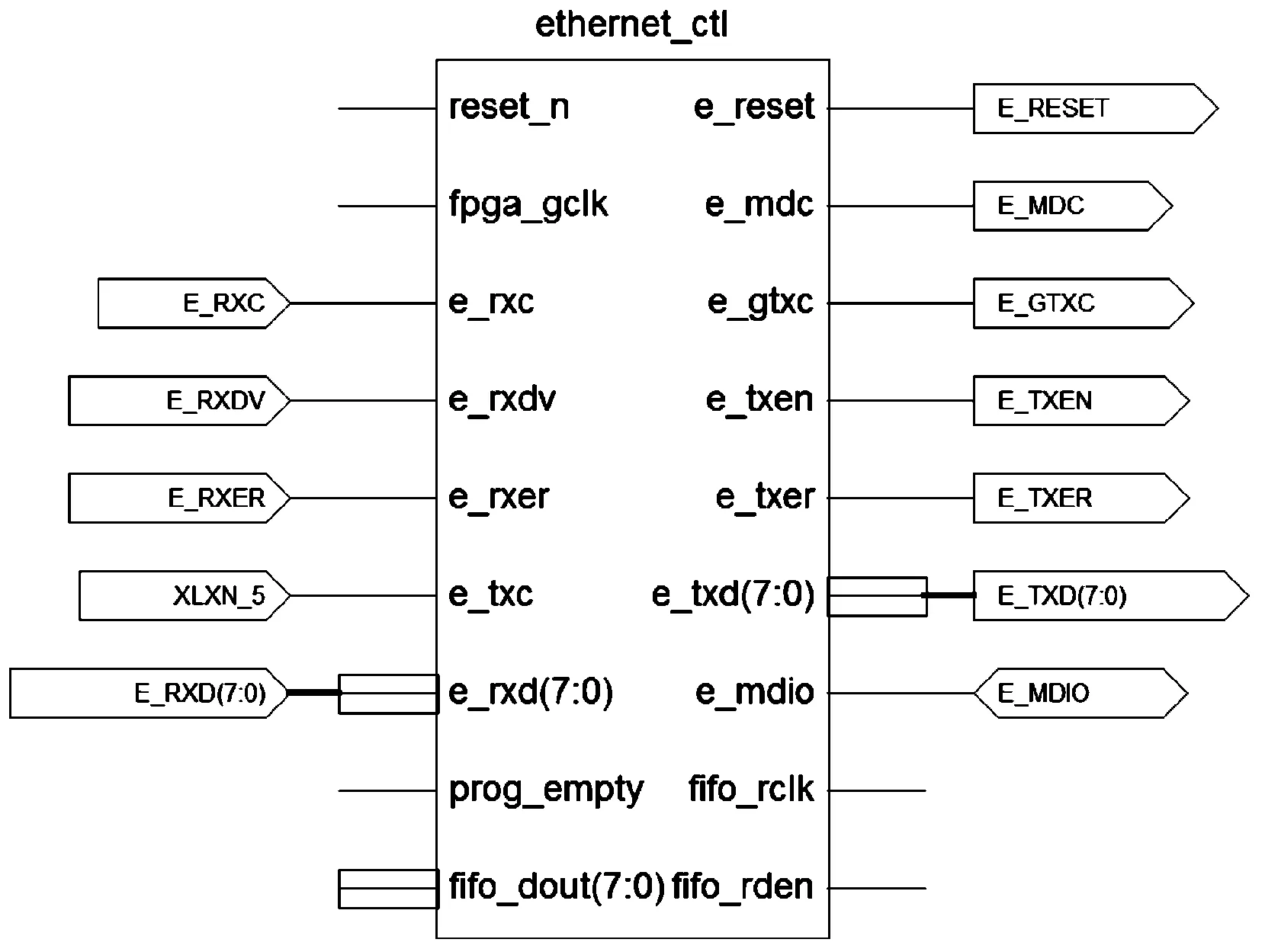

本系统的MAC层传输协议在FPGA中编程实现,代码由UDP 发送模块、UDP接收模块和CRC校验模块3部分组成,FPGA控制逻辑原理如图2所示。

图2 千兆以太网接口控制逻辑原理简图

NAND Flash中存储的采集数据通过以太网传输时,涉及跨时钟域的数据传输问题,在FPGA中例化一个异步FIFO。先将NAND Flash中的数据写入FIFO,设置非满即写,而在以太网读取FIFO中的数据时,设置读取标志,满 1 000 字节就可以启动一次以太网传输。本系统使用GMII接口实现FPGA与RTL8211EG间的通信,然后RTL8211EG与PC机之间使用网线连接,在数据封装时,重要的是把数据包中的握手信号设置正确,例如通信双方的MAC地址、UDP地址和IP地址。板卡上电后,PC机会自动识别外部设备,应保证物理连接的正确性。

2.2 CRC校验算法

CRC校验算法的实现是FPGA编程中的难点。CRC校验算法能够避免大容量数据在传输过程中出现误码现象,提高数据的可靠性。CRC校验算的实现过程中,需要用到模2除法运算,如果用硬件电路实现,需要占用较大的硬件资源,在FPGA中通过硬件描述语言实现,节约硬件资源,提高运行速率[9-10]。本系统选择CRC-32的生成多项式,通过改进实现算法,由之前的串行校验方式,1个时钟校验1位数据,升级到现在1个时钟校验8为数据的并行算法。该算法的实现提高了校验效率,进一步提高了数据传输的吞吐率。

CRC-32算法生成多项式为:

g(x)=x32+x26+x23+x22+x16+x12+

x11+x10+x8+x7+x5+x4+x2+x1+x0

通过移位寄存器和异或门实现模2除法,在FPGA中编码实现当前状态与下一状态的运算关系。在实现过程中使用组合逻辑,保持输出结果的实时性。则串行CRC-32算法的余数项为:

crc_next[31∶27]= crc_current[30∶26];

crc_next[26]= crc_current[25]⊕crc_current[31]⊕din;

…

crc_next[1]= crc_current[0]⊕crc_current[31]⊕din;

crc_next[0]= crc_current[31]⊕din。

由此可以看出,并行算法实际上就是,1个时钟内完成8次串行算法,理论上校验速率提高8倍。

数据输入din[7∶0],移位寄存器的初始值为crc_init[31∶0],与之对应的CRC-32校验值为crc_8,通过由低位到高位的迭代运算,可按照如下公式计算得到校验值。逻辑代码如下:

…

对于FPGA中CRC-32算法的逻辑实现是否正确,可通过ISE14.7中的在线逻辑分析仪来验证,输入待校验的数据00、FF、00、00,校验码为8FD73BF9,如图3所示。通过CRC的在线计算工具,计算得到该组数据的校验码为8FD73BF9,基本验证了该部分代码的正确性,经过对不同数据量校验码的多次验证,该部分模块较为稳定。本系统中采用的CRC-32校验算法比串行算法处理效率更高,例如,在10 MHz的时钟下对1 KB数据进行校验,所需时间为:1 000÷(10 MHz)=100 μs,而串行算法所需时间为:

(32+10 008)(10 MHz)=803.2 μs

表明该并行算法的效率比串行算法有了显著提高,而且运算的准确度较高,进一步提高了弹载数据采集系统的数据回读速率。

图3 CRC-32校验功能仿真图

3 系统功能测试

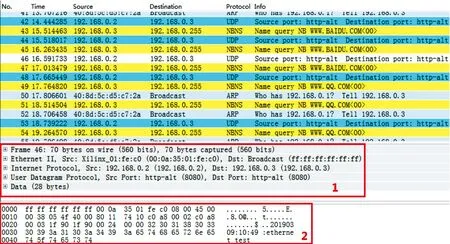

系统硬件与软件完成后,可借助网络调试助手和网络抓包工具Wireshark在实验室环境下,对系统进行完整的功能测试与验证。首先,将PC机的MAC地址作为板卡发送端的目的MAC地址,并且两者的IP地址需要保持一致,此处为192.168.0.3;然后将数据“012340123456789AB”作为有效数据按照以太网协议封装发送;最后,发送的数据将在网络调试助手中显示。如图4中方框1所示,说明发送与接收的数据一致,发送逻辑功能的正确性得到验证。对与接收模块来说,使用网络调试助手把数据发送给板卡,接收模块的逻辑会按照协议解析处有效的数据,发送“20190309∶10∶49∶ethernet_test”字符串给板卡,接收到的数据可在图4方框2中显示,收发数据保持一致,验证了接收模块也可正常工作。

利用抓包工具Wireshark,可以观察以太网通信协议中各层的数据结构,有助于对传输错误进行分析。关键信息有MAC地址、源MAC地址、IP包头和UDP报文格式等,如图5所示,说明系统设计的逻辑功能正确。此外,在某些应用场合,还可测试数据的传输速率,确定是否满足技术要求。例如,在0.042 5 s的时间内接收到了5 000数据包,按照每包数据1KB的数据量,千兆以太网的实时传输速率为:1 000×5 000×8/0.042 5=941 Mbit/s。与现有弹载数据采集系统相比,本系统已具有较高的数据传输速率,可有效节省数据回读时间,提高系统在靶场的测试效率。

图4 网络调试助手收发数据界面

图5 Wireshark查看系统板发送数据界面

4 结论

1) 本系统实现了基于FPGA的以太网MAC层控制器设计,并验证了其控制逻辑的正确性;

2) 通过仿真分析,系统时钟为10 MHz时,CRC-32校验码的生成速率为0.8 μs/Byte,在保证数据传输准确性的同时,对数据传输速率影响较小;

3) 经过系统功能测试,千兆以太网数据传输速率实际可达941 Mbit/s,且未出现误码现象,提高了弹载数据采集系统应用于靶场测试时的工作效率。