基于BISS-C协议的绝对值编码器数据采集方法研究

2020-12-01周光泽陈光胜

周光泽 陈光胜

摘 要:为精确测量角度位置电机闭环控制,提出基于FPGA的BISS-C协议寄存器配置与数据读取方法。首先研究BISS-C协议组网方式与帧格式,阐述寄存器读写模式与数据读取模式;然后针对正余弦编码器细分芯片IC-NQC,利用FPGA芯片灵活性及并行运行效率高等特点,通过状态机设计寄存器读写电路与数据传输电路,实现对IC-NQC芯片参数配置与数据读取。采用精密摆动电机进行实验验证。实验数据为MA时钟频率5mHz,数据交换周期100kHz,满足精密摆动电机运动控制定位要求。

关键词:BISS-C;FPGA;寄存器配置;数据交换;微特电机

DOI:10. 11907/rjdk. 201165

中图分类号:TP319文献标识码:A 文章编号:1672-7800(2020)010-0179-05

Abstract: In order to meet the accuracy requirements of digital galvanometer motion control system for position measurement, this paper proposes a method for register configuration and data reading of BISS-C protocol based on FPGA,conducts circuit design and experimental verification for this method. First, the BISS-C protocol networking mode and frame format are studied, and its register configuration mode and data read mode are described in detail. Then, for the features of FPGA flexibility and high parallel operation efficiency, the register configuration circuit and data transmission circuit are designed by the state machine. The experimental verification is conducted by galvanometer motor. In the experiment, the MA clock frequency is 5mHZ and the data exchange period is 100kHZ. Its reliability and accuracy meet the positioning requirements of the digital galvanometer motion control system.

Key Words: BISS-C; FPGA; register configuration; data exchange; micro special motor

0 引言

在精密擺动电机运动控制系统中常采用增量式编码器测量电机角度值[1]。相对于传统的方波编码器,正余弦编码器具有分辨率可拓展优点。由于受到码盘加工工艺、电源波动、环境温度变化、读数头的非线性等因素影响,位置检测元件输出的正余弦编码器信号常具有直流电平误差、幅值误差、正交相位误差、谐波分量误差、噪声误差等,直接影响伺服控制系统精度与可靠性[2]。对正余弦编码器输出角位置信号误差进行有效修正与补偿,采用合适的插值方法从正余弦信号中提取高分辨率的位置信息以满足伺服系统高精度控制要求,具有重要的研究与应用价值。

为提高正余弦编码器测量精度,需求解正余弦信号周期内的精确相位获得更高精度,该方法称为细分技术。常用的细分方法有正切直接计算法[3]、闭环跟踪法[4]、CORDIC算法[5]、麦克劳林级数法[6]等。文献[7]提出采用DSP处理器设计CORDIC算法方案,对11位正余弦编码器细分,最终采样电路分辨率达到29位,但在实际工程应用中存在浪费芯片资源和通信效率不高的缺点。因此,为保证高精密电机控制系统采样速率,本文选用IC-Haus正余弦编码器细分芯片IC-NQC对编码器正余弦信号进行细分。基于动态闭环跟踪细分技术的IC-NQC芯片可灵活转换正余弦信号,并通过BISS-C通信协议输出绝对值角度信号,以提高通信效率和细分精度。

BISS(Bidirectional Synchronous Serial)是IC-Haus公司开放的一种数字通信接口协议[8]。BISS通信协议为主机和传感器提供双向通信标准,适用于实时数据采集。相对于ENDAT协议,BISS在组网方式和线补偿方式上具有领先优势。BISS协议最新版本BISS-C协议,与之前的Biss版本完全兼容。BISS协议的解码方式包括软件解码和硬件解码;文献[9]采用DSP芯片作为数据采样主控芯片解码方案,最终数据交换周期可达40[μ]s。相对于串行运算的软件解码,并行运算的硬件解码可提供更高的通信效率。硬件解码可通过FPGA和BISS Master解码芯片实现。BISS Master灵活性较差、成本较高,不利于商用。FPGA芯片因其并行运行,性能强大且拓展性较好,是一种较为理想的通信解码方式。因此,本设计选用XILINX公司的SPARTAN-6系列FPGA芯片用以实现BISS-C通信协议硬件解码。

1 BISS-C通讯协议

1.1 BISS-C组网方式

BISS-C通信协议是一种全双工同步串行通信协议,BISS-C组网方式包括总线(bus)和点对点(point-to-point)两种模式。

总线(bus)模式配置中,所有连接设备首尾相连,每个设备包含多个从接口,主设备接口可在一个数据交换周期内与多个从接口进行通信。如图1所示,每个从机接口包含两个端子(SLI和SLO),SLI线用于接收前端发射信号,SLO线用于发射信号。SLO和SLI以链状形式连接所有主从接口。主控接口通过MA信号线向所有从设备提供时钟信号。第一个从接口(first slave)即第一个数据传输到主机的从接口,其SLO线直接连接到主SL信号线上。主机MO接口连接到最后一个从接口(last slve)SLI信号线上。不同于BISS-B协议连接的从接口只有8个,BISS-C协议从机没有数量限制,体现了BISS-C通信协议的优越性。

点对点(point-to-point)模式中,主控接口(master)只连接一个带有若干从接口(slave)的从机。通过差分信号,主机向传感器提供时钟脉冲MA,从接口通过SL信号线同步将数据回传给主机。在点对点模式中,BISS-C通信协议只有两根差分信号线,与SSI协议和BISS-B协议完全匹配。本实验采用点对点配置方式,主机为FPGA,从机为IC-NQC细分器,如图2所示。

1.2 BISS-C帧格式

点对点模式中,BISS-C通信帧时序如图3所示。当空闲时,主接口MA时钟线发送高电平,SLO信号线反馈保持高电平,表明从机准备进行数据通信。通信开始时,主接口发送时钟信号向从接口申请数据通信。时钟信号MA第一个上升沿同步从接口,第二个上升沿发送口,SLO反馈发送低电平,生成“ACK”位。实际上,由于通信线延迟(line-delay),MA时钟信号和SLO信号会产生一定的延迟,所以BISS-C通信协议规定每个数据交换周期开始后都要检测线延迟。ACK保持低电平直到检测完成,SLO发送表示START位的高电平,随后发送CDS(control data slave)标志位。之后的若干位都是数据位,反馈周期信号和角度信号。数据信息发送完成,SLO信号线反馈低电平,表示“TIMEOUT”位,至此一个数据通信周期结束。在TIMEOUT超时这段时间内,MA发送CDM(control data master)位。超时结束,MA和SLO再次置高,准备下一次数据交换。

1.3 寄存器通信与数据读取通信

1.3.1 寄存器读写通信模式

BISS-C协议通过多个MA时钟信号末尾挂载的CDM位组成控制帧,实现寄存器读写通信功能。在寄存器模式之前,CDM位至少发送14个“0”。然后CDM位发送“1”,开启寄存器读写权限。紧随其后, CDM位发送3位从地址接口ID、7位寄存器地址ADR和4位CRC校验码。接下来R(READ)和W(WRITE)字节决定BISS通信帧是写访问(RW=“01”)还是读访问(RW=“10”)。如图4所示,当开始写访问时,RW位后跟着1位起始位S、8位数据字节、4位CRC位和一位終止位P(P=”0”)。如图5所示,开始读访问时,紧随RW位后为1位S和12个“0”bit及1位终止位P,而CDS通信帧反馈8位数据和4位CRC校验码。

1.3.2 数据读取通信

BISS-C协议规定, CDM位发送“0”开始读取数据,CDS位作为CDM位的反向进行校验,其余通信帧时序与点对点通信时序一致。

2 IC-NQC芯片通信接口电路设计

2.1 硬件平台设计

本文基于精密摆动电机运动控制系统位置数据采集模块进行实验。主控芯片采用XILINX公司研发的SPARTAN-6-25芯片,编译环境为ISE14.7,硬件描述语言为VERILOG HDL语言。为增加位置数据采集精度,本实验采用IC-HAUS公司开发的正余弦编码器细分器IC-NQC芯片对振镜电机搭载的传感器正余弦信号进行细分。IC-NQC细分芯片可转换正余弦信号输出增量信号,也可输出绝对值信号。本实验采用读取绝对值信号功能,通信协议为BISS-C。

硬件电路如图6所示。振镜电机正余弦编码器正弦差分信号SIN+、SIN-,余弦差分信号COS+、COS-分别连接在IC-NQC芯片正余弦信号管脚上。IC-NQC芯片SLO与MA管脚经74LCX541MTC线路驱动器处理后传给FPGA芯片,与FPGA 进行数据交换。之后通过ISE14.7编译器搭载的Chipscope数字示波器读取电机角度数据和周期数据。

2.2 寄存器参数

IC-NQC是一个单芯片细分器,具有AD转换功能。应用计数矢量跟随功能,可选择分辨率和迟滞,且兼容SSI和BISS通信协议。前端增益可设置成阶段式以适应所有通用传感器信号,通过BISS-C协议寄存器读写模式配置IC-NQC芯片寄存器值设置所需功能。

IC-NQC具有34个寄存器,启动后芯片RAM内容随机。IC-NQC没有默认配置,错误管脚NERR会输出一个低电平,数据输出SLO、增量信号AB和Z输出一个高电平。为减小器件配置时间,最大的3uS短超时(TIMO=1,TOA=0)临时有效。

通过I/O接口访问IC-NQC时,芯片忽略TIMO、TOA、RPL和TMA寄存器值。IC-NQC芯片执行长超时,通过CDM位评估BISS寄存器通信。在每个信号位(CDM位)通信周期,MA时钟周期至少要持续4个时钟脉冲,即在SLO管脚反馈CDS位后,MA时钟信号线发送CDM信号触发超时(TIMEOUT)。图7为一个典型的寄存器配置最小周期。

寄存器配置步骤如下:①发送14个“CDM=0”bit,初始化IC-NQC芯片;②初始化后,SELSSI、RPL、TMA、TIMO寄存器位需要复位(“CDM=0”),SELSSI地址位ADR为0X02,RPL地址为0X03,TMA和TIMO地址为0X06;③依次从地址0X00到0X0C写入寄存器参数。根据所需,本实验设置信号调理增益2.667倍(GAIN=0X00),二进制分辨率为4 096(SELRES=0X04),通信协议选择BISS-C(ENCDS=0X01),周期计数输出为12位(M2S=0X02),其余未使用寄存器参数配置为“0”。

2.3 FPGA通信接口状态机设计

IC-NQC芯片时序如图8所示。

由图9可以看出,空闲时,MA时钟线和SLO信号线都置高。系统开始工作后,MA线发送时钟脉冲,第2个上升沿时,SLO信号线响应ACK位。随后依次反馈START和CDS位。以此为标志,之后的位数即是传感器旋转周期数据、角度数据、两位ERROR和CRC校验码。若为寄存器配置模式,则可忽略周期与角度数据,直接在CDS后MA发送CDM位。正常读取数据时,依次检测ERROR位和CRC校验码。若正确保存数据后进入超时,则准备读取下一次数据,若不正确则重新进入空闲状态。

根據BISS-C协议特点,将FPGA程序按需要进行模块化,包括IP核ROM(存储寄存器参数)、时钟模块,寄存器配置和数据读取模块、CRC校验模块。

(1)时钟模块需要产生MA时钟脉冲信号。本实验中,FPGA始终为20MHz,通过计数器产生通信中MA线需要10MHz时钟。在完成一轮数据传输后,SLO信号线变成低电平,进入TIMEOUT超时状态。此时若为正常读取模式,MA线上时钟停止。MA线置高(CDM=0, CDM数值和MA时钟脉冲数值反向)。若为寄存器配置模式,MA线依次取ROM核中存储的寄存器数据。

(2)IC-NQC寄存器参数众多,在配置寄存器前需要初始化,在寄存器参数配置时需要写入736个CDM位,本实验采用XILINX公司自带的ROM IP核实现数据存储。首先创建一个后缀为coe的系统文件,输入736个寄存器参数,随后在寄存器配置模块中调用ROM核即可。

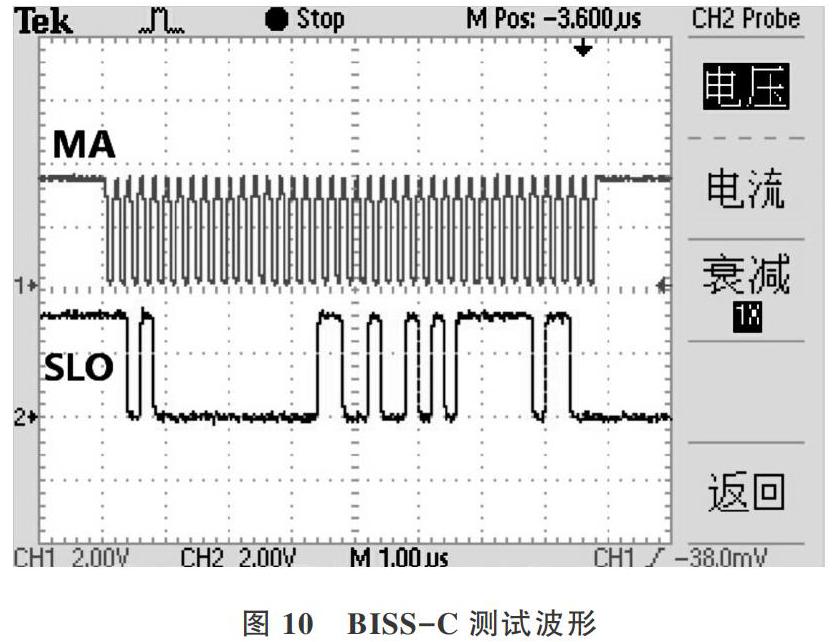

(3)寄存器配置和数据读取模块由一个有限状态机实现。一个BISS通信周期可以传输角度数据,也可以通过“CDM”位设置寄存器参数。因此,前736个通信周期作为寄存器配置,使用计数器记录个数,主机忽略CDS位后的数据位。在CDS信号反馈后,MA线发送CDM数据直接进入超时。寄存器设置完后进入正常数据读取模式接收数据,并调用CRC校验模块对数据进行验证。有限状态机结构如图9所示。

(4)为保证数据传输的可靠性,BISS-C通信协议采用循环冗余校验(CRC)。CRC校验码是数据通信领域常用的一种差错校验码。数据读取模块接收12位周期数据、10位位置数据、2位检测信号和6位CRC校验码共30位数据,其多项式为[x6+x1+x0]。传输完成后,运算CRC模块与校验码100101,如果30位数据与校验码100101模二运算余数为0,则校验通过,数据保存。若余数不是0,则重新进行数据读取。

3 实验测试结果

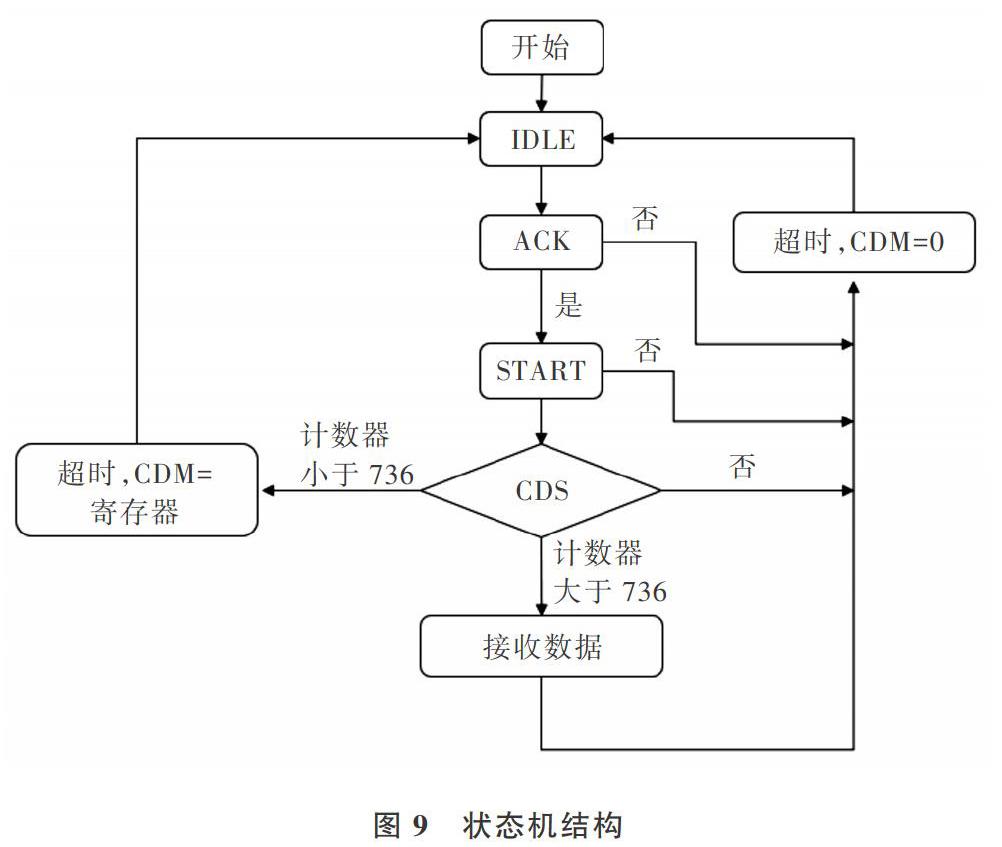

实际传输波形如图10所示,上方通道是MA信号线波形,下方通道是SLO数据信号线波形。从图中可以看出,信号传输波形和BISS-C通信波形是一致的。根据寄存器参数设置,SLO信号线反馈12位周期数据、12位角度数据、2位ERROR、6位CRC校验码。由此可见,上位机可正确接收数据。MA一个时钟脉冲周期为200ns,频率为5mHz;一个数据交换周期为10[μs],数据交换可达到100kHz。

精密摆动电机结构特殊,电机转动有两个极限位置,其夹角为24°。将摆动电机转子摆动到正极限位置,系统上电,角度读数101000110000,周期读数000000000000。随后将电机转动到负极限位置,角度读数为010100111001,周期读数为000010000011。可以看出电机偏转24°,电机内部正余弦编码器经过131个正余弦周期,正余弦编码器分辨率为2 048。IC-NQC细分器设置分辨率为4 096,角度数据测量分辨率达到[223],读取过程中数字无抖动,满足精密电机精度和稳定性要求。

4 结语

根据精密摆动电机运动控制系统实时性和精度要求,本文采用正余弦传感器编码器作为测角元件,使用基于闭环动态跟踪技术的正余弦编码器细分器IC-NQC芯片细分编码器正余弦信号。通过FPGA配置IC_NQC芯片寄存器及读取摆动电机角度数据。本设计中,MA时钟周期达到5mHz,数据交换周期达到100kHz ,采样分辨率为[223],采样数据未发生跳变。

实验结果表明,针对传统的增量式方波编码器分辨率难以提高问题,正余弦编码器可利用闭环跟踪等细分技术提高伺服系统位置信号采样分辨率。BISS-C通信协议不仅具有双向、高速、同步传输特性,还具有线路时分复用优点,寄存器配置和数据通信可在一个通信周期内传输,体现出通信协议的稳定性和便利性。本设计集成了正余弦信号细分技术和基于BISS-C通信协议的位置信号采集方案,可满足精密电机高精度、高速和实时性要求,具实用价值。

参考文献:

[1] 常怡萍,杨蕾. 基于BISS协议的绝对值编码器数据采集[J]. 电子测量计数,2017,40(4): 92-95.

[2] 王列虎,皮佑国. 基于BISS协议的编码器接口技术研究及应用[J]. 机床与液压,2011,39(8):103-105,121.

[3] CHARLES F L. Implementation of a high-speed sinu-soidal encoder interpolation system[D]. Virginia:Virginia Polytechnic Institute and State University,2004.

[4] 吴立,罗欣,沈安文,等. 基于闭环跟踪法的正余弦编码器细分技术[J]. 计算机技术与自动化,2011,30(4):5-8.

[5] 卢少武,唐小琦,马泽龙. CORDIC算法在光栅莫尔条纹细分中的应用[J]. 自动化仪表,2010,9(5): 23-25.

[6] 刘海龙. 麦克劳林级数法求取光电编码器转子位置算法[J]. 传感技术学报,2013,26(5): 616-621.

[7] 裴世聪,魏冬冬,文长明,等. 一种正余弦编码器高精度信号处理系统的设计与仿真[J]. 机械工程师,2017(9):24-27.

[8] 王希远,成荣,朱煜,等. 基于FPGA的BISS-C协议编码器接口技术研究及解码实现[J]. 液晶与显示,2016,31(4):386-391.

[9] 王洪娟,邢柏强,刘岩,等. 基于BISS C 模式编码器数据采集及显示系统设计[J]. 导弹与航天运载技术,2016,348(4):99-101.

[10] 张道勇,黄杨根,张辉. 编码器正余弦信号细分技术应用研究[J]. 机床与液压,2015,43(16):147-149.

[11] 黎家耀,王,晗,姚洪辉,等. 基于 Verilog 的双读数头光栅尺测量控制电路设计[J]. 信息与电脑,2019,18(24):82-85.

[12] 商怀昊,韩基鹏,肖鹏,等. 基于BISS-C协议的编码器的接口技术研究及其在伺服驅动系统中的应用[J]. 工业技术创新,2014,1(2):211-215.

[13] 陈燕,刘守山. 基于CPLD的光电编码器四倍频电路的设计[J]. 国外电子测量技术,2015,34(1):45-48.

[14] 樊勇. 基于绝对编码器的数据采集[J]. 现代电子技术,2011,34(3):107-109.

[15] LING S. DSP solution for high- resolution position with sin/cos-encoders[J]. International Conference on System Science, Engineering Design and Manufacturing Informatization, 2010(2):285-288.

[16] 肖鲲,王莉娜. 基于FPGA 的 BISS 协议光电编码器通信模块设计[J]. 电子测量技术2008,31(7):188-191.

[17] QIN J, YE Y T, LIU J X.A new method of signal processing of photoelectric encoder in visual optical robot with multi-phalanges [C]. International Conference on Computational Problem-solving.2012:251- 254.

[18] 高长清,林辉,张辉. BISS接口的光电编码器数据读出研究[J]. 计算机测量与控制,2009,17(5):957-958.

[19] 彭超越,张家洪,李川. 基于ARM Cortex-A9的烹饪机器人直流电机控制系统[J]. 软件导刊,2018,17(5):31-33.

[20] EKLUND N. CORDIC: elementary function computation using recursive sequences [J]. College Mathematics Journal,1999, 32 (5):330- 333.

[21] 赵长海,万秋华,梁立辉,等. 小型高精度航天级光电编码器[J]. 电子测量与仪器学报,2015,29(8):1224-1230.

[22] 韩竺秦,张丽娜. 两轮平衡机器人控制系统设计与仿真研究[J]. 软件导刊,2019,18(3):86-90.

(责任编辑:杜能钢)