基于忆阻器的计算存储融合体系结构研究进展 *

2020-11-30方旭东吴俊杰

方旭东,吴俊杰

(1.国防大学联合作战学院,北京 100091,2.国防科技大学计算机学院量子信息研究所兼高性能计算国家重点实验室,湖南 长沙 410073)

1 引言

进入21世纪后,人类正加速迈入数字化时代,大数据、云计算、人工智能等的发展方兴未艾,它们离不开海量数据的支撑。根据IDC(International Data Corporation)预测,人类所有的数量容量将从2018年的33 ZB快速上升到2025年的175 ZB,并且这种上升趋势正在加剧[1]。

另一方面,传统的基于CMOS工艺的存储技术已经接近发展的极限,依靠缩小器件尺寸提高存储器容量和密度的方法在可以预见的未来将变得不可行。所以,必须寻找不同于传统CMOS器件存储机理的新型存储介质,来制造速度更快、容量更大、功耗更低、体积更小、寿命更长、可靠性更高的存储器。

一个不容忽视的问题是,当前的计算机普遍采用冯·诺依曼体系结构,其运算和存储分离的特性,使得存储器和处理器多年来发展极不对称,导致了存储墙(Memory Wall)的出现,严重影响计算机性能的持续增长[2]。为了缓解甚至最终解决存储墙问题,必须寻求新的计算使能器件。

忆阻器被发现是除电阻、电容、电感之外的第4种基本电路元件[3,4]。忆阻器具有可作为下一代存储器件的诸多优异特性,包括高密度、低功耗、高耐久度、易于集成、CMOS工艺兼容性等特性,而且与动态随机存取存储器(DRAM)不同,忆阻器具有非易失特性,存储的信息在掉电情况下也不会丢失[5]。

更为重要的是,忆阻器被证明具有融合计算和存储的能力,被认为是一种全新的计算使能器件。2010年,惠普实验室的研究人员实现了基于忆阻器的蕴含状态逻辑(Stateful Logic),并证明这种计算是逻辑完备的[6]。这表明可以通过状态逻辑计算对基于忆阻器的存储结构中的数据进行直接处理,从而实现运算和存储的有机融合。

此外,忆阻器所展现的阻值随通过电量渐变的特性,和神经元细胞之间通过突触传递信号的机制类似,使得忆阻器适合用于模拟神经元细胞,实现神经拟态计算[7-10]。

忆阻器所具备的优异特性,使得它成为一种使能器件,有望成为下一代存储器件。基于忆阻器的计算存储融合结构有望缓解甚至解决存储墙问题,值得对其进行深入的研究。

然而,当前忆阻器尚处于实验室制备阶段,相关研究主要集中在器件机理和制备的层面,结构级研究较少,而面向应用的体系结构级研究则更少。鉴于此,本文按照从原理到结构再到应用的顺序,对该领域相关研究进行综述。首先详细分析了状态逻辑的实现原理以及改进方法,接着梳理了基于忆阻器交叉杆的状态逻辑设计方法,然后概括了基于忆阻器的数据存储结构的设计原理和实现结构,并探讨了面向应用的计算存储融合体系结构技术,最后进行总结和展望。

2 状态逻辑计算

自从忆阻器被发现以来,关于忆阻器的应用研究如火如荼,涉及多个领域[11,12],主要有非易失性存储器[13,14]、状态逻辑计算[6,15 - 18]、神经拟态计算[7 - 10,19 - 22]等。在前2类应用中,忆阻器作为数字器件,主要利用其状态可在高阻态HRS(High Resistive State)和低阻态LRS(Low Resistive State)快速翻转的特性;在第3类应用中,忆阻器作为模拟器件,主要利用忆阻器阻值可根据外界电压激励连续变化的特性,模拟生物神经元细胞突触实现神经拟态学习,以及构建混沌电路[23]。

本文内容限定于忆阻器状态逻辑相关研究,即将忆阻器作为一种数字器件。状态逻辑计算是基于忆阻器的高低阻态切换所实现的计算,计算的输入输出都采用忆阻器的阻值表示[6,16,24 - 27]。

2.1 实现原理

蕴含逻辑(Implication Logic)作为第1种被提出的状态逻辑,具有十分重要的意义[6]。它证明了忆阻器电路可以进行状态逻辑计算,实现计算和存储的融合。蕴含逻辑的电路和真值表如图1[6]所示。

Figure 1 HP implication logic图1 惠普蕴含逻辑

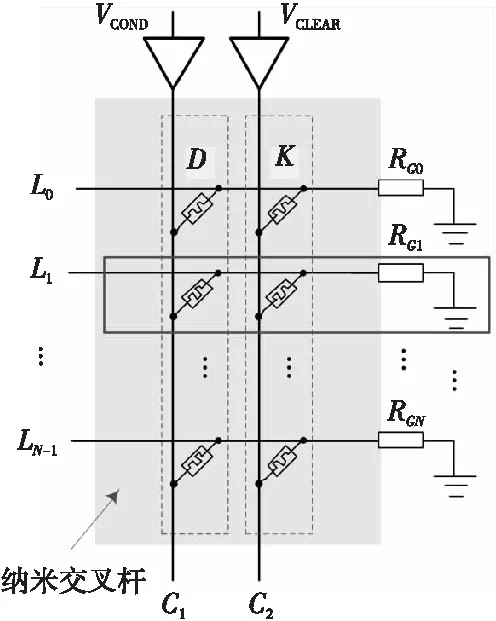

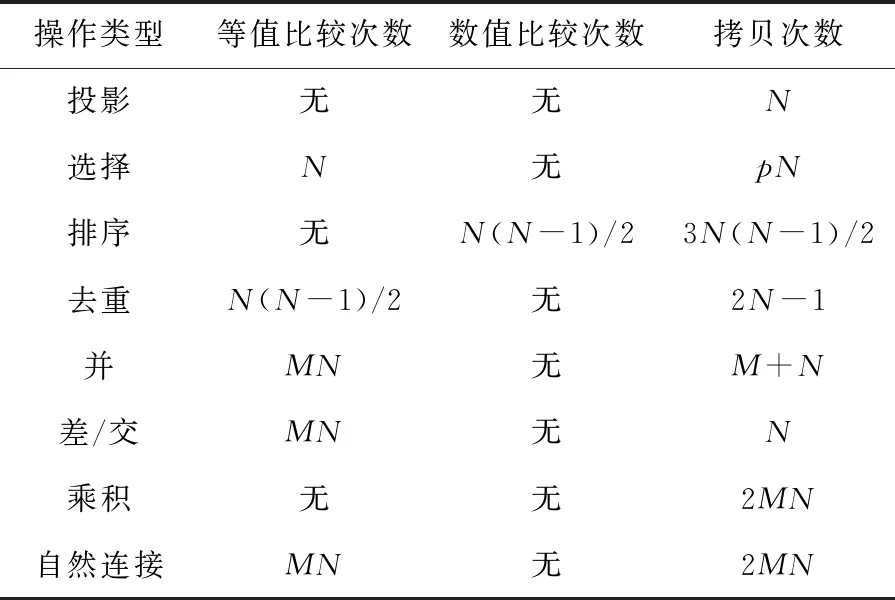

从图1a中可以看出,蕴含电路由2个忆阻器P和Q,一个接地电阻RG,及水平与垂直纳米线构成。水平纳米线与垂直纳米线通过忆阻器相连,并通过负载电阻RG接地。RG阻值介于忆阻器2个阻态的阻值之间,即ROFF>>RG>>RON。这里ROFF表示忆阻器高阻态的阻值,代表逻辑0,RON表示忆阻器低阻态的阻值,代表逻辑1。忆阻器P和Q具有阈值效应,阈值电压的绝对值为VT,即只有当施加在忆阻器上的电压的绝对值大于VT时,忆阻器的阻态才可能变化。若同时对P和Q施加电压脉冲VCOND和VSET,即可完成蕴含操作,结果保存在Q的阻值中。此处,VCOND被称为条件脉冲,VSET被称为置位脉冲,p和q代表忆阻器P和Q的逻辑值。蕴含逻辑的工作原理可根据P的初始状态,分以下2种情况解释:

(1)当P处于高阻态(p=0)时,由于ROFF>>RG,所以RG上的电压几乎为0,于是Q2端的电压VQ≈VSET(>VT)。此时,无论Q处于哪种状态,都将被置为低阻态(q=1)。上述情况对应于图1b中真值表的Case 1和Case 2。

(2)当P处于低阻态(p=1)时,由于RG>>RONO,所以RG上的电压几乎为VCOND,于是Q2端的电压VQ≈VSET-VCOND( 综合上述2种情况,P和Q的状态蕴含被计算出来,结果保持在Q的阻值中。 从图1b的真值表可以看出,如果Q初始时处于高阻态(q=0),蕴含操作等价于对忆阻器P的值进行取反的FALSE操作。而如果单独对一个忆阻器施加一个清零电压脉冲VCLEAR(|VCLEAR|>VT),可以直接将忆阻器的阻值切换到高阻态(逻辑“0”)。 根据数理逻辑的基本原理可知,蕴含与取反运算构成逻辑完备集{IMP,FALSE},所有布尔逻辑运算都可以基于蕴含和取反操作实现。也就是说,基于忆阻器的状态逻辑计算是完备的,可以实现所有的逻辑计算。 由惠普提出的蕴含逻辑,虽然是逻辑完备的,但也存在一定问题,主要表现在2个方面:一是运算效率较低,蕴含逻辑虽然是完备的,但复杂逻辑操作分解为蕴含逻辑需要较多操作步骤,效率较低,需要寻找与非(NAND)或者或非(NOR)等更高效的原子操作;二是运算过程会破坏输入,图1所示的蕴含逻辑中,忆阻器Q参与状态逻辑计算,并保存计算结果,输出结果有可能覆盖输入值,因此运算过程会破坏输入。 3M1R逻辑就是对惠普蕴含逻辑的一种改进[17,28]。3M1R逻辑基本计算结构由通过字线WL(Word Line)和位线BL(Bit Line)相连的3个忆阻器A、B、Y和1个分压电阻RC构成,如图2[17]所示。通过在A和B上施加电压脉冲VR,在Y上施加电压脉冲VDD,3M1R可以1步实现与非(NAND)操作,而IMP逻辑和FALSE逻辑需要分3步才能实现NAND逻辑。3M1R电路结构本质上和惠普蕴含逻辑是一样的,所以它也具备逻辑完备性,它的优点是逻辑操作不会破坏输入状态。 Figure 2 Schematic of the NAND gate in 3M1R图2 3M1R实现NAND的逻辑电路 而MAGIC逻辑采用另一种改进思路[18]。MAGIC在实现或非(NOR)逻辑时,其基本电路单元由2个正向并联的忆阻器和1个反向忆阻器串联构成,如图3[18]所示。和3M1R一样,MAGIC不会破坏输入状态。和IMP、3M1R相比,MAGIC可以较高效地实现所有的逻辑操作,并且采用全忆阻器实现,从而容易实现交叉杆集成。此外,MAGIC运算时只需要1个电压V0就可实现逻辑操作。MAGIC的缺点是脉冲电压V0约束要求很高,实现不同的逻辑运算时的V0值不同,实际实现难度较大。 Figure 3 Schematic of the NOR gate in MAGIC图3 MAGIC实现NOR的逻辑电路 有一类状态逻辑的实现,是通过忆阻器2端不同的输入电压来实现忆阻器状态翻转,从而实现状态逻辑计算的[29,30]。它的状态转化可以根据有限状态机得出,但输入输出量纲不同,使得它们进行大规模交叉杆集成时难度更大。 还有一类状态逻辑通过将多个单极性/双极性忆阻器串联/并联,以对外呈现新的阻值切换特性,从而实现更高效的逻辑计算[15,31,32]。比如,DBM(Dual-Bit-Memristor)器件通过新的制备方法得到,等效于将1个单极性忆阻器和1个多极性忆阻器串联到一起,从而得到更高效的状态逻辑操作效率[32]。然而,这类器件的制备相对复杂,需要在器件复杂度和状态逻辑操作效率之间进行折衷。 所有的状态逻辑实现归根结底是基于忆阻器阻值的条件切换特性,通过时间维度上的分步迭代来实现逻辑功能。状态逻辑的最大优势在于逻辑完备的计算在存储中发生,而且代表输入、输出的物理量都是阻值,可以方便实现级联,甚至可通过流水线实现并行逻辑操作。状态逻辑具有的计算和存储融合能力,使得这种计算结构有可能超越经典的冯·诺依曼体系结构。 第2节中提到状态逻辑计算是单比特的计算,为了充分发挥状态逻辑在存储位置直接进行计算的优势,必须将状态逻辑从单个比特位拓展到多个比特位,或者说并行计算的模式。为了实现并行状态逻辑计算,首先应该在交叉杆中实现基本逻辑的并行操作。更进一步,应该设计出基于更通用的、抽象层次更高的公共操作,为高层操作实现提供基础。 基于忆阻器交叉杆结构,将基本蕴含逻辑操作从一维(单比特)扩展到多维(多比特并行)是非常直观的。图4[33]展示了规模为2×N的交叉杆,它由N条水平纳米线和2条垂直纳米线组成,其中存储了2个N位数据D(d0d1…dN-1)和K(k0k1…kN-1)。垂直纳米线称为字线,水平纳米线称为位线。那么,图4中任意一条位线上的2个忆阻器,以及该位线的接地电阻这三者组成了1个单比特与(AND)逻辑电路。所以,N条位线上一共有N个与逻辑电路。如果在字线C1和C2上分别施加电压脉冲VCOND和VCLEAR,那么N个与操作将并行执行[33]。执行完成后,K中存储的数据是D和K按位与的结果。按同样的方法,可以将基本状态逻辑扩展成为对应的并行逻辑。和单比特状态逻辑相比,并行状态逻辑有望将操作的效率提高N倍,N表示位线长度,即并行度。 Figure 4 Schematic of the parallel AND gate图4 并行与逻辑实现电路 iMemComp进一步给出了动态实现并行状态逻辑操作的方法[34]。iMemComp将交叉杆的每一行都称为一个“处理器”,即由一条字线和多条位线交叉处的忆阻器形成逻辑门电路。这些一位的“处理器”在交叉杆中同时受到电压激励,从而实现并行状态逻辑计算,如图5[34]所示。图5中HRS指高阻态(逻辑0),LRS指低阻态(逻辑1),IN和OUT分别指代输入和输出忆阻器。 Figure 5 Parallel computing schematic in iMemComp based on multiple one-bit processors图5 iMemComp中多个单比特“处理器”并行逻辑计算结构 iMemComp的优点是在每个“处理器”中设置了一些可配置的忆阻器,用来实现可重构计算。所谓可重构计算,是指不改变电路结构的情况下,通过重置操作(RESET)设置忆阻器的阻值,使得相同的电路实现不同的状态逻辑计算。 拷贝操作将交叉杆中的N位数据拷贝到交叉杆的另一个位置,是实现交叉杆中数据迁移,支持状态逻辑重构,进而构建高层体系结构的一个重要操作。 在图4中,如果存储K的忆阻器预先被置位,那么并行与逻辑实现的效果等价于并行复制逻辑,即D被拷贝到存储K的忆阻器中。这样的并行复制逻辑被称为拷贝逻辑[33]。从上述过程可以看出,只需要2个时间步,就可以实现忆阻器交叉杆中2个N位数据之间的拷贝操作。 比较操作是一种较为重要的逻辑操作,其中判断2个N位数值是否相等的等值比较是比较操作的基础,被广泛应用于微处理器、通信系统和控制系统中。比如,在微处理器中,等值比较器用来判断流水线中前后2条指令是否数据相关,从而决定流水线是否需要暂停;在通信系统的路由芯片中,等值比较器用于检测到达的数据包携带的目的地址和路由器地址是否相等,从而决定接收或是转发该数据包;控制系统中,等值比较器用于检测控制变量(时间、温度等)是否达到预设值,从而决定是否触发相应控制动作。 一种基于并行异或(XOR)状态逻辑实现的等值比较结构如图6[35,36]所示。采用该结构,输入的二维像素值首先被转化为一维,并被编码到N位输入忆阻器(Entry Data)。输入忆阻器和交叉杆上的模式忆阻器(Database 1)执行并行异或操作,得到每一位的异或比较结果,形成N位的输出值(Output Data)。N位输出值再通过数字比较器(Digital Comparator)进行转化,最终结果由一个模拟忆阻器的阻值表示。该方法的优点是利用了忆阻器交叉杆执行状态逻辑的并行性。但是,在综合N位输出值得出比较结果时,采用了数值比较器,结果又采用模拟忆阻器表示,导致外围电路庞大,不易集成。 Figure 6 Graphic pixel comparison schematic based on parallel XOR logic gate图6 基于并行异或逻辑实现的图形像素比较操作结构 国防科技大学忆阻器研究团队提出了通用等值比较逻辑[33]。对2个N位数据D(d0d1…dN-1)和K(k0k1…kN-1)进行等值比较,分解为表达式: ∨(dN-1∧kN-1)]∧ (1) 实现表达式(1)的N位等值比较电路由1个忆阻器交叉杆阵列、N+5个CMOS控制开关、1个计算脉冲产生器、1个控制脉冲产生器、N+1个接地电阻5部分组成,如图7[33]所示,其中,N为等值比较电路能比较的数据位数(或者说字长)。 Figure 7 Universal N-bit equivalent comparison logic circuit图7 通用N位等值比较逻辑电路 等值比较过程被分解为2次比较过程,每次比较过程都由“清零—取反—或非—读取”4个操作组成,分别完成式(1)式中2个或非逻辑表达式的计算。如果其中任何1次子比较过程完成后,结果忆阻器的阻值为高阻态(逻辑0),那么可以判定D和K不相等;如果2次比较过程之后,结果忆阻器的阻值都为低阻态(逻辑1),那么可以判定D和K相等。 (1)清零。清零操作所要达到的效果是使得存储中间结果T(t0t1…tN-1)的忆阻器T0T1…TN-1和结果忆阻器MRES被置为高阻态(逻辑0)。 (2)取反。将数据K(k0k1…kN-1)按位求反结果(k0k1…kN-1)命名为K。此时,K被保存到中间结果忆阻器T0T1…TN-1中,得到中间计算结果T(t0t1…tN-1)。 (3)或非。或非操作完成了式(1)的第1个子表达式的运算,运算结果保存在忆阻器MRES中。 (4)读取。如果VOUT的输出接近0,那么结果忆阻器MRES处于最大阻值状态(ROFF),于是式(1)的第1个或非表达式的计算结果为0,所以式(1)的值必为0,故D和K不相等,比较过程结束;如果VOUT的输出接近读脉冲VREAD,那么结果忆阻器MRES接近最小阻值状态(RON),于是式(1)的第1个子表达式的计算结果为1,此时式(1)的值尚无法确定,需要进行第2次比较过程,比较过程类似。 第1次比较过程中的每一步,图7中计算脉冲产生器的输出线W1~W4、控制脉冲产生器的纵向控制脉冲输出线WC1~WC4和横向控制脉冲输出线WL0~WLN上应产生的脉冲如表1[33]所示,其中,计算脉冲包括以下4种脉冲:幅度为VCLEAR的清零脉冲、幅度为VCOND的条件脉冲、幅度为VSET的置位脉冲和幅度为VREAD的读脉冲;而控制脉冲为VSOPEN。 采用通用等值比较逻辑的实现方法进行2个多位数据之间的比较,最少只需4个时间步得出2个数据不相等的比较结果,最多需要8个时间步得出2个数据相等的比较结果。该方法的优点是,比较过程全部采用状态逻辑实现,易于交叉杆集成,而且在最坏情况下,比较次数不会随着比较数据的字长的增大而增加。缺点是比较时间步不是常量。 专用等值比较逻辑是对通用等值比较逻辑的一种改进[33]。通过观察可以发现,采用状态逻辑计算式(1)中的2个或非逻辑表达式时,除了输入不同,计算步骤是相同的。专用等值比较逻辑的电路由2套完全相同的电路组成,每一套都和通用等值比较逻辑的电路(如图7所示)完全一致。待比较数据D(d0d1…dN-1)和K(k0k1…kN-1)以及它们的按位互补值D(d0d1…dN-1)和K(k0k1…kN-1),被分别存储在图8a和图8b中,因此等值比较的比较过程中不再需要进行清零和求反操作。 专用等值比较逻辑在保留通用等值比较逻辑优点的基础上,采用空间换时间的方式,增加了逻辑电路,但缩短了实现等值比较所需的时间步。采 Figure 8 Dedicated equivalent comparison logic circuit图8 专用等值比较逻辑电路 用专用等值比较逻辑实现方法,进行2个多位数据之间的比较,最少只需3个时间步就可以得出2个数据不相等的比较结果,最多只需4个时间步就可以得出2个数据相等的等值比较结果。相比通用的等值比较逻辑实现,最好情况和最坏情况下比较的效率都有大幅改进。 为了充分利用状态逻辑计算和存储融合的优势,以及基于忆阻器交叉杆的存储器具有的高密度、存储非易失的优点,必须设计适当的数据存储结构。本节介绍“数据HOME自治”的概念,以及基于“数据HOME自治结构”的忆阻存储器结构[33,37 - 39]。 数据HOME自治定义:数据可在其存放位置进行不受外界干扰的自我管理,实现预定的操作和服务的数据处理机制[33]。 Table 1 Voltage pulse sequence of the first comparison process in the Universal N-bit equivalent comparison logic 这里,“数据HOME”指存放数据的宿主。计算机中,“数据HOME”即是存储器芯片。“自治”指存储系统能够不受外界干扰,自我管理实现预定的操作和服务。 图9[33]从静态角度阐述了“数据HOME自治”原理。传统计算结构下,运算与存储分离,与数据存储相关的上层软件(文件系统、数据库等)只能通过处理器配合存储器完成各种数据操作,如图9a所示。而如果可以实现运算和存储的融合,以前依赖软件在处理器上运行才能完成的部分功能被固化到存储器中,如图9b所示。存储器依靠自身的运算能力完成特定的数据操作,比如数据查询、访问控制、纠检错和加解密等。 Figure 9 Static interpretation of the “Data Home Autonomy” principle图9 “数据Home自治”原理静态解释 图10[33]从动态角度对比了2种结构下数据处理的过程。冯·诺依曼体系结构下,数据存储和数据处理在空间上分离,导致了存储墙问题,如图10a所示。而采用运算存储融合结构,对数据的部分处理在存储器中完成,如图10b所示。 Figure 10 Dynamic interpretation of the “Data Home Autonomy” principle图10 “数据HOME自治”原理动态解释 “数据HOME自治”使得:(1)通过减少数据的读出写入,降低了数据被非法访问的风险;(2)由于部分数据处理在存储器中完成,极大缓解了存储墙问题的压力;(3)存储器中容易以更高的并行度实现更细粒度的数据处理,比如在位级(bit)或字级(word)完成一些数据操作(例如数据比较等),提高了数据处理的效率。 数据HOME自治结构定义:把采用数据HOME自治原理实现的存储结构称为“数据HOME自治结构”,或者称为“数据HOME自治体”[33]。 “数据HOME自治”的原理用于指导实现“数据HOME自治结构”时,要求:(1)底层器件必须具备融合计算和存储的能力,或者说逻辑区域和存储区域的轮换能力。这就要求数据区和存储区工艺兼容,并且结构等价。(2)可以实现计算存储的融合,在数据所在位置进行计算。 传统CMOS工艺中,处理器和存储器两者目标不同,导致制作工艺和封装工艺都不同,所以传统CMOS器件不满足这2个要求,而忆阻器则完全不同。对于基于忆阻器交叉杆的存储结构而言,数据区即是逻辑区,逻辑区即是数据区,两者都基于交叉杆结构,功能和特性上完全等价。状态逻辑则能实现计算存储的融合。 一种可能的基于忆阻器的“数据HOME自治”结构如图11[33,37,38]所示。从图11中可以看出,该结构由数据区、逻辑区和配置电路3个部分组成。其中,数据区用于存储数据;逻辑区进行逻辑运算,用于对区域内的数据进行处理;配置电路配合逻辑区完成运算并控制数据区和逻辑区的轮换。 Figure 11 Memristor-based “DATA HOME Autonomy” structure 图11 基于忆阻器的“数据 Home 自治”结构 基于忆阻器的“数据HOME自治”结构所具备的这种融合计算和存储的能力,使得它只需接收特定的操作命令,就可启动自治结构内部的数据处理过程,并视情况输出处理结果。处理过程中无需CPU干预,计算在数据所在位置进行,除内部的数据传输之外,基本不存在存储层次间的数据传输过程(输出处理结果除外),从而大大节省了数据开销。所以,基于忆阻器的“数据HOME自治”结构有望极大提高特定计算的效率,有效缓解传统计算架构中的存储墙问题。 根据“数据HOME自治”原理和基于忆阻器的“数据HOME自治”结构,图12展示了一种忆阻存储器结构[33,37 - 39]。忆阻存储器可由多个Bank构成,而每个Bank又由多个忆阻Tile和多个功能部件构成。图12中的忆阻存储器由4个忆阻Bank 构成,其中Bank 0中包含4个忆阻Tile和多种功能部件。 Figure 12 Memristive memory architecture图12 忆阻存储器结构 忆阻Tile是指忆阻存储器中用于数据存储和逻辑运算的忆阻器交叉杆区域,是忆阻存储器中数据的驻地,也是对数据进行状态逻辑操作的基本单位。一种可能的忆阻Tile结构如图13[33]所示。 Figure 13 Memristive Tile structure图13 忆阻Tile结构 操作控制模块负责控制计算脉冲产生器和控制脉冲产生器。在忆阻存储器上进行的操作不管多么复杂,最终都是通过Tile上的状态逻辑操作实现的。操作控制模块能够产生公共基本操作所需的计算脉冲序列和控制脉冲序列的功能模块,可以根据不同需求对忆阻器Tile进行配置和重构。 图12中的忆阻存储器结构和图13中的忆阻Tile结构设计基本涵盖了近期关于支持状态逻辑计算的存储结构设计[17,30,40-49],这些状态逻辑电路设计一般都包含忆阻器交叉杆结构设计、外围电路以及脉冲序列产生方法3部分。该设计的优势是以“数据HOME”结构为理论指导,设计了功能模块完整的、具有自主运算能力的存储结构。缺点是受制于器件制备能力,并没有制作出实际的忆阻存储器。 体系结构研究最终是为了面向应用,提高应用的执行效率。然而,并不是所有应用都可通过采用基于忆阻器的“数据HOME自治”结构带来性能加速。一般来说,实施“数据HOME自治”对应用的数据存储特性和处理特性都有要求。 “数据HOME自治”结构要求应用所处理的数据必须是结构化的。忆阻存储结构是基于交叉杆实现的。交叉杆结构非常规整,适合存储结构规整、类型统一的结构化数据,而不适合存储非结构化数据。 “数据HOME自治”结构要求应用所进行的数据处理任务必须是简单的。状态逻辑是一种用时间换空间的操作,如果对数据的操作过于复杂,转化成状态逻辑操作序列可能过长,从而导致实现效率低下。而某些操作的复杂度可能超出了状态逻辑可以接受的范围,必须由CPU来完成。如果应用对数据的操作包含大量简单同质化操作,则适合采用状态逻辑实现。 应当按照这2个要求去寻找适合“数据HOME自治”结构实现的应用。然而即使找到了适合的应用,面向应用进行自上而下全流程体系结构设计的工作并不多见。国防科技大学忆阻器团队开展了面向关系数据库存储体系结构[33]、存储加密体系结构技术[37]、图像处理体系结构[38,50]、自治容错体系结构技术[39]4个方向的体系结构级研究。下面以基于忆阻器的关系数据库存储体系设计为例,阐述相关设计思路。 关系数据库作为目前最重要的数据处理模型和工具,在当前乃至未来相当长的一段时间内仍将广泛使用。关系数据库的存储特性和操作特性非常适合采用“数据HOME自治”结构实现,并且忆阻存储器将有效提高关系数据库的性能[33]。 在设计存储结构时,他们采用了将二位数据表映射到物理存储(交叉杆)中的实现方式,如图14[33]所示。这种数据存储设计的优点是直观,并且支持记录的随机寻址。 Figure 14 A data table and its possible mapping to the memristor crossbar图14 数据表及其在忆阻器交叉杆上可能的映射方式 所有数据库的数据操作归类为单元组一元操作、全关系一元操作和全关系二元操作。其中,单元组一元操作包括扫描操作、选择操作和投影操作;全关系一元操作包括去重操作、排序操作和分组操作;全关系二元操作包括并/交/差操作、乘积操作和连接操作。他们通过分析这些操作的底层实现机理,将这些操作完全通过比较和拷贝2种操作实现,并设计了在忆阻存储器中高效实现这些操作的方法。 值得一提的是,设计忆阻存储器中关系数据库查询操作的实现方法,基于如下严格的假设: (1)假设忆阻存储器上可以实现元组拷贝操作和比较操作; (2)假设关系数据已存储在忆阻存储器Tile中; (3)只关心查询操作的实现过程,不考虑对查询结果的处理; (4)待查询的关系和结果关系的所有元组都可容纳在一个基本Tile或者扩展Tile内; (5)进行操作的记录之间都是按位对齐的,并且进行的比较操作都是对元组之间的关键字进行比较。 Table 2 The worst case complexity analysis of the query operation in the memristive memory 为了对基于忆阻存储器的关系查询操作进行分析和评价,设计了忆阻存储器的性能模型。该模型对忆阻存储器中进行关系数据库单元组一元操作、全关系一元操作和全关系二元操作等查询操作的时间开销进行分析。若用N和M分别代表关系R和关系S中的元组数目,那么这些操作在最坏情况下的计算复杂度如表2所示。通过HSPICE对这些单元组一元操作、全关系一元操作和全关系二元操作进行模拟测评,并和基于磁盘的关系查询操作进行对比发现,面向关系数据库的存储体系结构以及忆阻存储器可以有效地加速关系数据库的基本查询操作[33]。 随着CMOS器件逼近物理尺寸极限,业界一直在寻求新型使能器件或者技术,以延续摩尔定律。其中,基于忆阻器的状态逻辑就是一种极有发展前景的使能技术。状态逻辑可以实现真正意义上计算和存储的融合,有望开创全新的计算架构。 为了研究基于忆阻器的计算存储融合体系结构,本文按照从原理到结构再到应用的顺序展开论述。首先阐述了惠普实验室提出的蕴含状态逻辑的实现原理,针对其存在的缺点,详细介绍了2种状态逻辑改进方法。接着探讨将状态逻辑从单比特位操作扩展为多比特位并行操作的方法,阐述拷贝操作和比较操作的实现方法。然后介绍了数据HOME自治原理,概括基于忆阻器的数据存储结构的设计原理和实现结构。最后以关系数据库存储体系结构设计为例,探讨了面向应用的计算存储融合体系结构技术。 然而,当前基于忆阻器状态逻辑的面向应用的体系结构还处于理论设计阶段。原因是多方面的:(1)因为对于忆阻器的器件级机理的研究一直在深入,制备忆阻器材料的选择尚无定论,研究人员还在寻求均一性更好、切换效应更明显、器件状态偏移更小的忆阻器;(2)忆阻器交叉杆内在的写串扰、寄生电阻(电容)、潜通路等问题,严重影响着交叉杆规模的扩展;(3)和CMOS计算相比,状态逻辑计算采用时间换空间的方法获取优势,但对于复杂逻辑操作,需要迭代执行的时间步骤,以及由此带来的外围电路的开销,很可能得不偿失;(4)设计状态逻辑时,缺少自动化设计工具支持。这些因素限制了忆阻器从实验室走向实用。 以上提到的4个方面研究应该并重,在可见的将来,基于忆阻器的状态逻辑计算应该提高执行稳定性和效率,充分利用交叉杆的并行性,开发更高效的原子操作,如多位数据的大小比较等,并找准应用领域,设计面向应用的高层体系结构,成为特定应用的高效加速部件。同时,应和CMOS电路结合设计,发挥各自的优点。2.2 状态逻辑优化研究

2.3 状态逻辑分类

3 基于忆阻器交叉杆的状态逻辑设计

3.1 基本逻辑并行实现

3.2 拷贝操作

3.3 比较操作

4 基于忆阻器的数据存储结构

4.1 数据HOME自治原理

4.2 基于忆阻器的数据HOME自治结构

4.3 忆阻存储器结构设计

5 面向应用研究

5.1 “数据HOME自治”结构对应用的要求

5.2 关系数据库存储体系结构技术

6 结束语