ETC中FM0编码的一种实现方式

——基于FPG A的FM 0编码仿真技术研究

2020-11-13高晔

高 晔

(山西晋中高速公路管理有限公司,山西 晋中 030800)

ETC(electronic toll collection),即不停车收费。ETC系统是采用专用短程无线通信(dedicated short range communication,DSRC)技术来完成整个收费过程,该技术是一种短距离无线传输技术,支持点对点、点对多点的通信,保障车载单元OBU(on-board unit)与路侧单元RSU(rate-sensor unit)之间的通信[1]。

现代化通信技术不断发展变化,数字基带通信由于其功耗小、成本低廉等方面的优势,受到了广泛应用。当信息的原始信号形式不符合信道的频率特性时,必须对原始信号进行变换,以适应传输信道的要求。信道编码技术的研究实现,能够有效地解决这一问题,提高数据抗干扰能力,从而将数据进行准确的传输,保证了人与人之间的正常通信,促进社会经济的发展。目前有多种形式的编码方式,例如非归零码、曼彻斯特码、差分曼彻斯特码、FM0码等,每种编码方式都有自己的特点,而FM0码以其便于位同步提取、频谱宽度较窄、实现电路简单而在数字通信中得到广泛的应用。

2007年5 月实施的ETC中国国家标准[2]GB/T20851—2007以及2007年10月国家交通部颁布的《收费公路联网收费技术要求》,规定我国ETC系统的无线数据通信采用FM0编码[3]。

本文设计了ETC电子标签的FM0编码。

1 FM0编码的实现

FM0(bi-phase space coding)编码的全称为双相间隔码编码,工作原理是在一个比特的持续时间窗口内采用电平变化来表示逻辑。如果电平从持续时间窗口的起始处翻转,则表示逻辑“1”。如果电平除了在持续时间窗口的起始处翻转,还在持续时间窗口中间翻转则表示逻辑“0”[4]。ETC系统中规定OBU与RSU的上行链路数据速率为512 kbit/s,RSU与OBU的下行链路数据速率为256 kbit/s。

ETC电子标签的FM0编码通过使用VERILOG语言在QuartusⅡ编译环境里实现,硬件选择的是CYCLONE系列的现场可编程逻辑门阵列(field programmable gate array ,FPGA)[5],为了实现速率为512 kbit/s上行链路数据,本设计选择的晶振频率为1.024 MHz,定义了一个位宽为1比特的变量time_cnt1,该变量在每个时钟的上升沿加1,相当于该变量一个时钟周期为0,一个时钟周期为1,在0和1之间来回变换,这样可以认为该变量为1的时刻就是1.024 MHz晶振频率的一半即512 kHz的速率,在该时刻且在时钟信号的上升沿对原始数字信号进行翻转,就实现了对逻辑“1”的FM0编码。如果原始数字信号为逻辑“0”,则除了上述time_cnt1为1的时刻的操作外,还需要在该时刻跟随的下个time_cnt1为0的时刻再次对信号进行翻转,从而实现了对逻辑“0”的FM0编码[6]。

由于原始数据是字节的形式,需要对其进行变形,变为比特形式,也就是并行转串行,为实现这种变化,定义了一个位宽为1比特的变量bit_temp1和位宽为3比特的变量bit_cnt,同时也定义了位宽为1比特的变量start,start_temp1,start_temp2和start_temp3,当start的状态为“0”时,代表没有新的原始数据到来,不需要进行FM0编码。当start的状态从“0”跳变为“1”时代表字节形式的原始信号同步到来,需要进行FM0编码。start_temp1是start延迟一个周期之后的状态,start_temp2是start_temp1延迟一个周期之后的状态,start_temp3是start_temp2延迟一个周期之后的状态。bit_cnt会在time_cnt1为1的时刻且在时钟信号的上升沿加1,这样相当于实现每两个时钟周期变化一次,从0逐步累积到7,bit_cnt的每次变化,就从原始的字节数据code中取出对应的比特位赋给bit_temp1,这样bit_temp1就成为了串行的原始信号,对bit_temp1进行FM0编码后就完成了整个编码过程。

定义一组位宽为1比特的变量code_end1,code_end2和code_end3,这3个变量用来指示对某个字节形式的原始信号进行完FM0编码后,停止继续编码。code_end2是code_end1延迟一个周期之后的状态,code_end3是code_end2延迟一个周期之后的状态,相当于code_end3是code_end1延迟两个周期之后的状态,对code_end1延迟两个周期是为了对原始信号的最后一个比特进行编码,2个周期后最后一个比特编码完成,利用code_end3的状态来停止FM0编码。具体程序[7]如下:

2 结果仿真

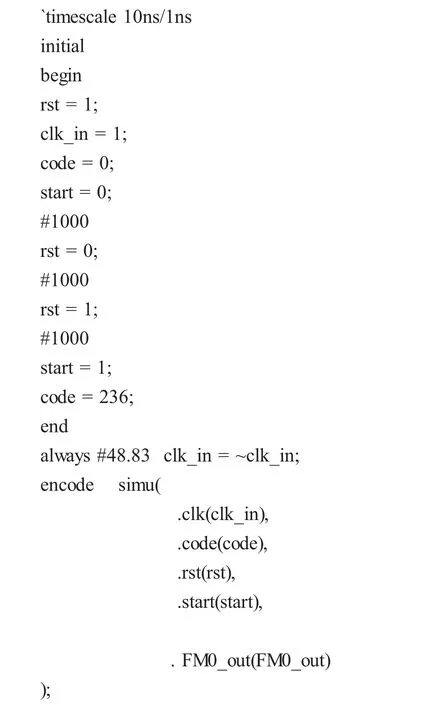

设置QuartusⅡ软件,使其在设计文件编译综合后产生反应布局布线结果的门级网表文件(该文件格式类型为.VO)和标准延时文件(该文件格式类型为.SDO),针对本文设计的FM0编码实现方式,编写了testbench测试文件,测试文件运行在modelsim环境中,测试文件中设定时间单位为10 ns,时间精度为1 ns,输入时钟周期为48.83×10×2=976.6 ns(频率1.024 MHz),复位信号rst在测试程序开始运行10 000 ns后有一个负跳变,低电平持续时间为10 000 ns,该复位信号将设计文件中的相关变量进行复位,使这些变量处于要求的初始状态。字节形式的原始信号code初始化为0x00,变量start的初始状态为“0”,在程序开始运行30 000 ns后start的初始状态跳变为“1”时,同时字节形式的原始信号code同步到来新的数据,变为0xEC,开始进行FM0编码,具体代码如下:

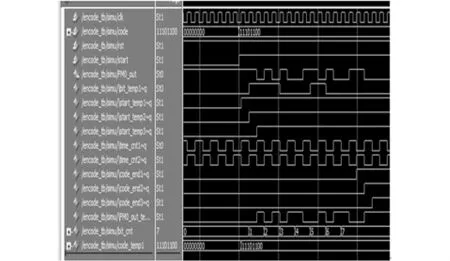

关联QuartusⅡ编译后生产的门级网表文件encode.vo和标准延时文件encode_v.sdo文件后进行modelsim后仿真,运行仿真程序后便得到如图1所示的仿真结果。

图1 FM0编码的modelsim仿真结果

由图1的仿真结果显示,本设计很好地实现了FM0编码,达到了ETC系统中规定的OBU与RSU之间上行链路512 kbit/s的数据速率。同时也可以看到将输入时钟周期改为48.83×5×2=488.3 ns(频率512 kHz)或者保持原输入时钟周期不变,对原输入时钟周期利用锁相环或VERILOG语言进行2分频,得到频率为512 kHz的时钟周期,就可以实现ETC系统中规定的RSU与OBU之间下行链路256 kbit/s的数据速率。

3 结语

在FM0编码设计中,关键的问题就在于对于接收到的字节形式的原始信号进行变换,变为比特形式的串行数据,然后再进行编码。本文给出了采用VERILOG语言实现FM0编码的一种具体实现方法,设计灵活巧妙且方便移植,能够大大缩短开发时间,设计选择的是CYCLONE系列的FPGA,但是对于其他系列或厂家的复杂可编程逻辑器件(complex programmable logic device,CPLD)或FPGA,本设计依然有效,甚至对于内嵌了可编程逻辑门阵列的其他类型处理器,例如:数字信号处理器(digital signal processor,DSP)、ARM(advanced RISC machine)等 ,也仍然可以正常地完成编码工作,对ETC系统中车载单元OBU与路侧单元RSU实现FM0编码具有现实的借鉴意义。