基于IBIS模型的多路脉冲信号源ADS仿真

2020-11-03周文渊呼义翔罗维熙张信军尹佳辉

周文渊, 呼义翔, 罗维熙, 张信军, 尹佳辉

(西北核技术研究院 强脉冲辐射环境模拟及效应国家重点实验室,西安 710024)

0 引言

随着近年来脉冲功率技术的迅速发展,脉冲功率装置展现出功率高、装置大、多台并联运行的特点[1],例如圣地亚国家实验室的Saturn X-ray accelerator使用了70台示波器进行数据测量[2],HERMES III使用了65台示波器进行数据测量[3]。对多通道数据进行分析时,要求所有数据的开始记录时刻相同,所以需要多通道同步脉冲信号源进行触发,触发信号应具备快前沿和低抖动特点。随着集成电路设计和制造技术的飞速发展,超高速比较器、高速总线工作频率以 GHz 为单位不断提高,故采用有源器件搭建多路脉冲信号源成为可能。

本文设计了一种基于高速比较器的80通道触发系统,器件间采用LVPECL/PECL差分信号进行连接,最终输出快前沿的CMOS电平脉冲信号。由于器件间采用高速差分线连接,信号可能存在反射、串扰和地弹等问题,这就对PCB信号完整性设计提出了新的挑战[4]。在电路设计时利用ADS软件和输入输出缓冲器模型(input/output buffer information specification, IBIS)对整个系统进行模拟仿真,可提前发现系统中信号反射、串扰等问题,并估算系统的抖动、延时和脉冲上升沿参数。IBIS 模型是由 Intel 公司开发,并首先用于PCB板级和系统级的数字信号完整性分析的模型。模型通过“绘制”管脚的V/I和V/T曲线方式描述了器件引脚的行为特性,器件内部保持“黑盒”特性,有利于保护知识产权,因而得到了半导体厂商的欢迎和支持。此外,IBIS 模型的仿真速度快,收敛好,非常适合系统级仿真,所以自诞生以来,IBIS模型仿真得以迅速的发展。1999年,IBIS模型被认定为美国工业标准(EIA/ANS I 656 -A)[5-6]。

1 系统结构及原理

1.1 模型简介

IBIS是用来描述IC器件的输入、输出行为特征和PCB上电路系统的相互作用的模型,其核心思想是将所有器件的I/O描述为Buffer的模型。它不是从元件的结构出发进行定义,而是从元件的行为出发进行定义,描述了器件在特定负载、特定封装下的输入/输出行为,对芯片内部电路延时、逻辑、抖动、功耗不进行描述。图1为标准输入输出IO缓冲器模型[7]。

图1 缓冲器模型

在IBIS模型中,器件封装引入的寄生参数由pkg表示,全局寄生参数均值包括寄生电阻R_pkg,寄生电感L_pkg,寄生电容C_pkg,全局参数对器件的所有管脚均适用。对同一类型的管脚,IBIS使用Model来进行描述,Model名称可以由用户自己定义,但Model_type必须使用IBIS3.2中规定的模型[8-9]。所有的IBIS模型可大致归结为两类:输入缓冲器模型和输出缓冲器模型。图1(a)为输入缓冲器模型,Power_Clamp和Gnd_Clamp是必须包含的参数,分别代表了正负钳位二极管电平,而C_comp参数是管脚硅电容值,影响器件的Ramp参数。图1(b)为输出缓冲器模型,除了Power_Clamp,Gnd_Clamp以外,还有Pullup和Pulldown参数,即器件的上拉/下拉电平,其C_comp影响器件的Rising Waveform和Falling Waceform参数。

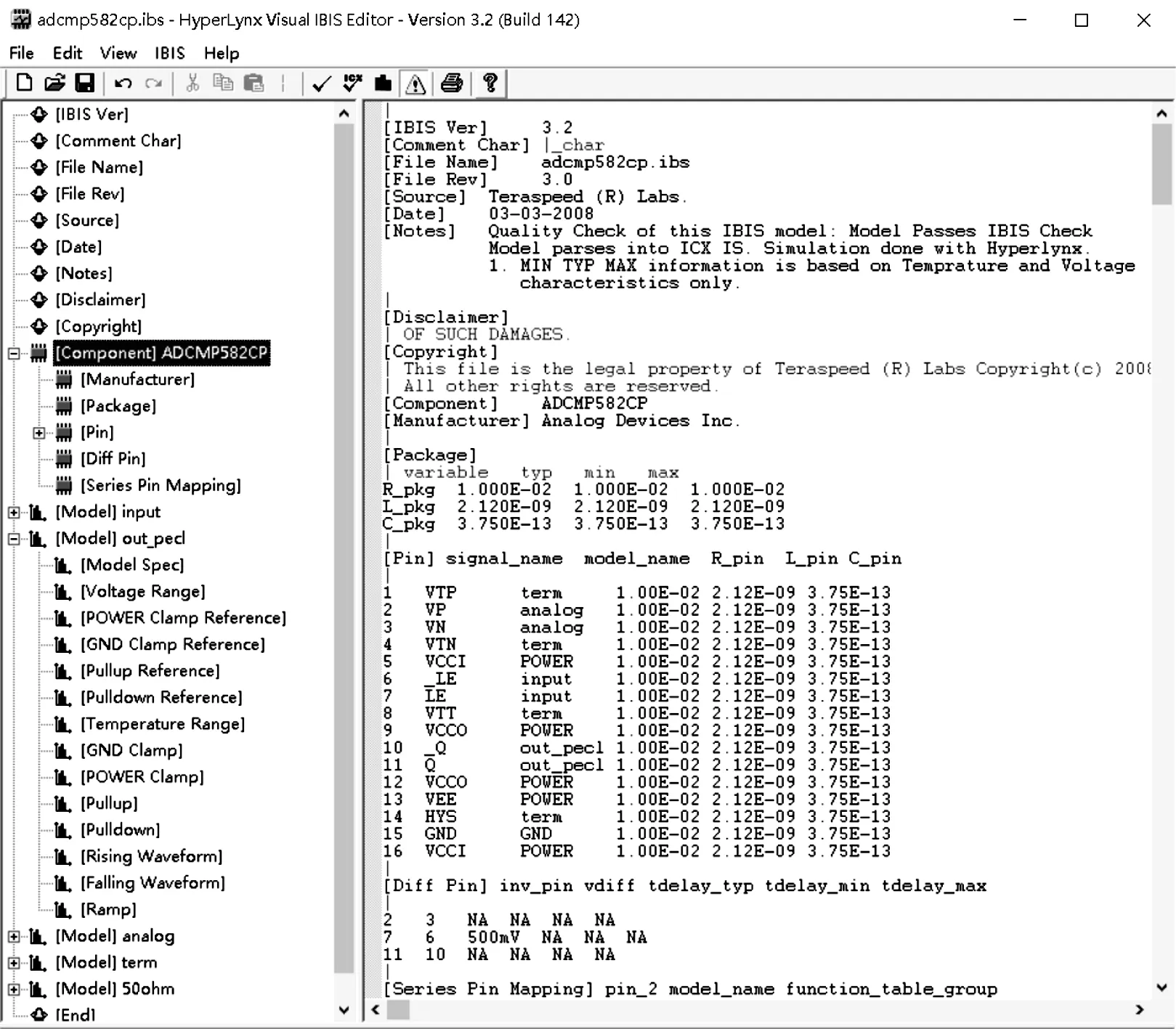

1.2 语法结构简介

虽然IBIS已经发展到V7版本,但3.2版本仍然使用最为广泛。图2是使用Visual IBIS Editor软件打开一个IBIS文件的界面。该文件描述的是高速比较器ADCMP582CP的输入输出特征。“|”符号用来进行注释,“[]”内的为关键字,可看出,该文件IBIS版本号为3.2,文件版本号为3.0,器件名称为ADCMP582CP,制造商为Analog Devices Inc公司。接着文件在[Package]字段描述了封装引入的寄生电阻/电感/电容均值,并在[Pin]字段中对器件所有引脚进行描述,包括所属模型和每个管脚的RLC寄生参数等。引脚按信号特征被分成term,analog,POWER,input,out_pecl,GND模型,并在后续字段中,分别对这些模型进行描述。

IBIS文件在[Diff Pin]字段中定义了引脚差分对,从图2(a)中可以看出,管脚2、3是一组差分信号线,[Pin]字段中可以看到,管脚2、3为模拟差分输入脚。同样,管脚6、7为输入锁存使能脚,管脚10、11为差分输出脚。在[Series Pin Mapping]中定义了ADCMP582CP两个差分输入脚的50 Ω匹配电阻,即脚1、2之间3、4之间内置50 Ω匹配电阻。

图2 管脚定义

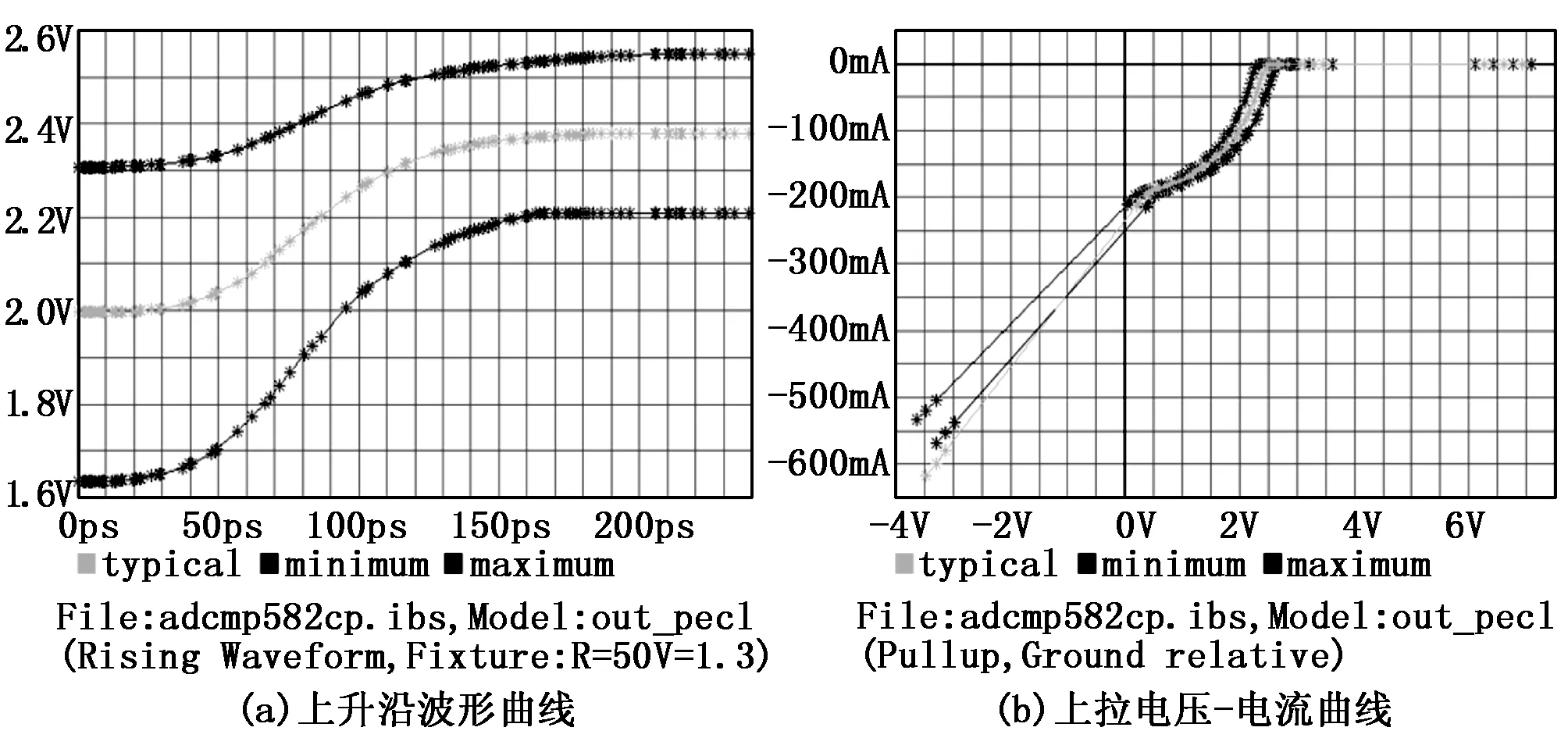

这里以out_pecl引脚为例,说明各参数意义。ADCMP582CP的差分输出管脚定义如图3所示。out_pecl字段首先定义了管脚类型为Output_ECL,然后定义了参考电压为1.3 V,输出阻抗为50 Ω,输出电压均值为2.2 V,管脚寄生电容为0pF。输出电压范围为0~3.3 V,上拉电平为3.3 V(3.135~3.465 V)。在进行了初略表述后,使用6个数据表分别描述了Gnd_Clamp、Power_Clamp、Pullup、Pulldown、Rising Waveform、Falling Waveform参数。其中,Gnd_Clamp、Power_Clamp在-3.3~6.6V时,电流均为0,可能是因为模型测试或制作时,并未获取该参数。Pullup表中,列举了上拉电平从-Vcc到2×Vcc情况下,输出电流由1.77 μA增加到-533 mA,其中负号代表电流流出器件,正号代表流入器件。虽然该电压范围超出了厂家在手册中规定的绝对最大额定值,但是这个范围覆盖了信号传输过程中可能发生的欠压、过冲和反射情况,因此,IBIS规定了驱动器建模的电压范围为-Vcc~2×Vcc。

图3 out_pecl定义

图4为使用Visual IBIS Editor图形窗口查看PECL输出管脚的部分V/T和V/I数据。图4(a)为信号上升波形V/T曲线,可以看出,IBIS文件中,对芯片typcial/maximum/ minimum速度下输出特性分别进行了描述。在低速时,器件输出摆幅最大,Vpp≈750 mV,高速时,输出电压摆幅最小,Vpp≈250 mV,典型值Vpp≈380 mV。图4(b)为Pullup管脚的V/I曲线。Pullup曲线是输出管脚与地(或VCC)之间的电压与电流关系图,电流流入器件为正值,流出器件为负值,从图中可以看出,当输出信号为正,外部接地时,输出电流约为230 mA。

图4 out_pecl管脚V/T曲线及V/I曲线

1.3 ADS仿真及对IBIS的支持

ADS(Advanced Design System)是由安捷伦(Agilent)公司开发的EDA系统仿真软件,广泛应用于射频微波模拟与仿真领域[10]。ADS提供了原理图仿真、电路板模拟仿真的功能,并支持AC/DC/瞬态分析,提供了图形化的数据分析界面。操作人员只需拖动器件模块,编辑器件参数,选择求解方法即可进行原理图模拟仿真。

在ADS中,提供了Integrity - IBIS模块,支持IBIS规范中定义的17种IO模型,并提供了一个通用器件模型,在用户装载.ibs文件后,可根据用户选择不同的管脚,自动转换为指定的模型。要注意的是,一个IBIS模型只能表述一种管脚,而同一个器件有输入输出等多种类型的管脚,所以需要根据仿真需要,指定一个或多个模型来描述一个器件。器件工作在不同的频率下时,其管脚V/I曲线也不相同,所以在IBIS文件中,对器件的管脚采用了三组数据进行描述,分别是全速、低速和中等速度,对应了ADS的IBIS模型的max/min/typ参数,所以在装载.ibs文件时,需要指定器件工作状态。

2 仿真实验与分析

2.1 系统构成

通过多路脉冲信号源去触发多台示波器系统,需要重点关注多个输出信号之间的时间延迟和幅值。单次输出信号间的延迟主要由固定延迟和输出抖动构成,其中,固定延迟可以通过标定获得,并可以在示波器软件中设定延迟参数进行校准。而通道间抖动无法通过标定等技术手段进行规避,所以成为系统重点关注的参数之一。另外,快的脉冲前沿可降低示波器外触发抖动,一定的电压幅值可降低干扰带来的误触发。所以,通道间抖动、脉冲前沿时间和幅值是本文中关注的3个技术参数。

脉冲信号源逻辑框架如图5所示,使用超高速比较器+两级时钟扇出buffer+比较器来输出CMOS电平,实现脉冲信号的整形、分配和输出。

图5 脉冲信号源构架

高速比较器采用ADI公司的超快型电压比较器ADCMP582CP。该芯片采用ADI公司的专有硅锗(SiGe)双极性工艺制造,内置小摆幅PECL输出驱动器,可工作在10Gbps条件下。该芯片传播延迟180 ps,最小脉冲宽度为100 ps,确定性抖动(Deterministic Jitter, DJ)为10 ps,随机抖动(Random Jitter, RJ)为200 fs,输入具有50 Ω片内端接电阻,输出电平Vpp为400 mV,偏置电压为VCCO-2 V=1.3 V,3.3 V电压供电。

第一级时钟扇出器采用ADCLK944,该芯片是一款超快型时钟扇出缓冲器,具有100 Ω片内匹配电阻,差分输入,支持直流耦合LVPECL,具有4个全摆幅的发射极耦合逻辑(ECL)输出驱动器,将 VCC 偏置到正电源,VEE 偏置到地时,输出LVPECL(正ECL),最高工作频率7 GHz,RJ=50 fs,3.3 V供电。

第二级扇出器ADCLK950也采用硅-锗(SiGe)双极性工艺制造,内置10个ECL输出驱动器,最高工作频率4.8 GHz,RJ=75 fs,VCC=3.3 V,VEE=0 V。当使用ADCLK944+ADCLK950 两级扇出时,可得到40路扇出信号。

在信号末端使用LTC6957-3产生脉冲信号。LT6957是低相位噪声、双输出逻辑电平转换器,该芯片可输出2路3.3 V同相位CMOS信号,300 MHz工作时,抖动为146 fs,两个输出脚间延迟≈5 ps(典型值)。使用以上器件构成的电路总共产生80路脉冲信号。

2.2 高速比较器输出信号仿真

由于高速比较器输出信号直接进入信号扇出IC,二者之间距离较短,控制好布线阻抗后,串扰和反射影响较小。但由于ADCMP582CP输出PECL电平,信号摆幅Vpp=400 mV,而后端ADCLK944输入差分信号最小值也为400 mV,需要评估二者直连的可行性。图6(a)为使用ADS对ADCMP582CP与ADCLK944连接模拟图。二者使用3.3 V供电,PECL差分线通过50欧姆电阻上拉到1.3 V。输出信号经过差分微带线进入ADCLK944,微带线采用ADS自带的LineCalc工具进行计算,采用松耦合方式,耦合系数-30 dB,基板材料采用 Rogers5880,介质基片相对介电常数为2.2,相对磁导率为1,厚度0.508 mm,金属导电层厚度为 0.03 mm,介质损耗正切角为 9e-4,线宽1.5 mm,线间距2.1 mm,线长3 cm。虽然手册中ADCLK944在输入端有内置匹配电阻,但在实际仿真时发现若无外加匹配电阻,波形反射严重,说明IBIS模型中并未包含该匹配电阻,所以在差分线末端使用100欧姆电阻进行匹配。图6(b)为输出PECL线上的差分电压,可见使用以上设置,可获得摆幅460 mV的差模信号,信号前沿231 ps,满足ADCLK944输入信号要求。

图6 输入比较器与第一级buffer仿真

2.3 信号扇出仿真

多路脉冲信号源的关键指标之一是脉冲上升时间。快的前沿可降低示波器外触发系统的抖动,以获得准确的触发零时。另外,连接比较器、两级时钟扇出器及CMOS信号输出器之间的差分线参数会影响信号传递的完整性,需要通过仿真的方法进行评估。图7(a)为两级LVPECL信号扇出及脉冲输出原理图。输出匹配电阻参数设置与前述相同,考虑到最终通道数较多,芯片之间有一定距离进行摆放,所以比较器和第一级信号扇出器之间微带线长度为10 cm,一二级信号扇出器之间微带线长度为15 cm。信号源输出线缆长度100 cm,负载电阻50 Ω。ADCLK944、ADCLK950和LT6957-3均为3.3 V供电,VEE=0 V,差分信号通过50 Ω上拉到1.3 V。由于ADI公司提供的IBIS模型中,只有管脚输入/输出的参数,在ADS中只能定义为一个输入模块或输出模块。所以当IC既有输入又有输出时,需要使用一个输入模型和一个输出模型,前一个模块的DigO脚和后一个模块的触发脚连接一起来描述一个IC器件对信号响应。

图7(b)是在前级比较器输出正脉冲方波情况下,在第二级buffer和LT6957-3前端的输入信号,测量得到两个信号前沿(10%~90%)时间分别为238 ps和200 ps,Vpp分别为1.30 V、1.26 V,信号干净无杂波,说明两级信号扇出器件输出参数匹配较好。图7(c)为最终脉冲信号波形图,可以看出,在不接负载时,LT6957-3输出方波信号前沿为200 ps,幅值3.3 V,当在传输线末端外接负载(50 Ω,16 pF)模拟示波器外触发端口时,得到脉冲前沿为997 ps,幅值1.97 V。实际使用时,示波器外触发端口电容小于16 pF,触发脉冲前沿将小于997 ps。

图7 信号扇出级输出脉冲仿真图

2.4 输出信号抖动分析

由于IBIS模型只能用于器件间信号完整性模拟,并无器件内部信号延迟和抖动参数,而该参数是衡量多通道脉冲信号源性能的关键指标之一。厂商给出的器件手册中,给出了每个器件的延迟和抖动典型值。其中,器件的抖动与输出信号上升时间密切相关。图8为器件的抖动与信号前沿电压摆率关系图,可以看出,当器件输入信号上升沿变快时,其抖动也相应减少。前文中,ADCLK944输入信号前沿约为231 ps(10%~90%),幅值约为360 mV(10~90%),电压摆率=0.36/0.231=1.6 V/ns,在图8(a)中对应的抖动约为117 fs。ADCLK950输入信号前沿为238 ps(10%~90%),幅值为1.04 V(10%~90%),电压摆率=1.04 V/0.238 ns=4.4 V/ns,在图8(b)中对应抖动为87 fs。由器件对应的数据手册可知,ADCMP582CP随机抖动为200 fs,LT6957-3工作在300 MHz情况下时,器件增加的抖动为146 fs。所以信号经过多路脉冲信号源后增加的随机抖动约等于4个器件抖动的加和,约为550 fs。

根据抖动的双狄拉克模型[11],随机抖动采用高斯分布模型,输出抖动<所有抖动之和≈11 ps,所以脉冲信号源输出通道抖动值为11 ps。表1列举了4个器件引入的抖动和延迟,从表中可以看出,器件引入的延迟约为1.15 ns。触发源内电缆长度为28 cm,延迟约1.4 ns。所以脉冲信号源的总延迟为2.55 ns,信号前沿<1 ns(50 Ω,16 pf),理论上整体指标优于DG645的8通道输出时间指标(前沿上升时间3 ns,抖动25 ps)[12],当然实际参数还与制造工艺、环境温度、电磁干扰等因素有关,有待样机测试验证。

图8 器件抖动与信号上升速度关系图

输入器件前沿斜率/(V/ns)随机抖动/fs RMS确定性抖动/ps RMS延迟/psADCMP582CP-20010180ADCLK9441.6117-35ADCLK9504.487-45LTC6957-34.92146890*

*未包含两个输出通道间延迟5 ps rms

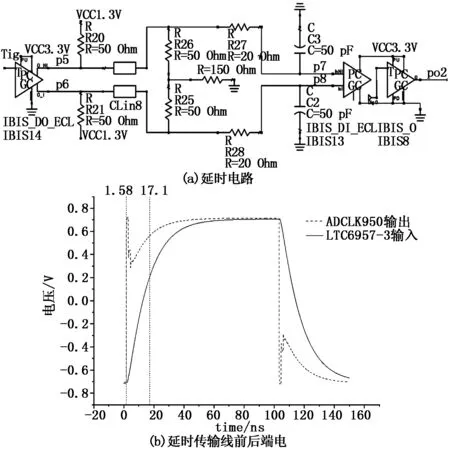

2.5 输出信号延时调节电路模拟

由于PCB生产工艺的影响,器件间微带线的阻抗匹配与理论计算有所差异,且随工作温度、电源供电差异、工作环境等因素的影响,每个器件的参数也会有所差异,最终造成所有通道输出延迟不一致,所以需要在LT6957-3前设置可调的延时电路,便于对每个通道进行校准。虽然ADI公司提供的数字延时IC具有延时调整方便,精度高的特点,但售价较高,不适用大量通道使用。RC延时电路是一种简洁有效的延时方法,在LTC6957-3前端增加一级RC延时,可用于调节通道输出延时。但增加的电阻串联在LVPECL差分线上,对该级信号可能存在反射影响,需要进行模拟分析。为了降低传输线上信号的反射变化,所以采用电阻阻值不变,调节电容的方法来调节延时。图9为增加延时电路后的原理图和仿真结果。图9(a)中,在差分信号上串入20 Ω电阻,对地并联500 pF可调电容,图9(b)为ADCLK950输出Vpp和延时后Vpp波形,可以看出,增加的20 Ω电阻在传输线上引起了反射,在ADCLK950输出端出现了尖峰信号,但经过RC延时滤波后,在LTC6957-3的输入端,信号无毛刺、尖峰等影响;增加了RC延时电路后,输出Vpp在0.2 V(LTC6957-3翻转阈值下限)处延迟了15.5 ns。由于电容也存在温漂等因素影响,所以应选择电容最大容值所产生的延时可满足调节范围即可。

图9 差分信号延时电路及波形

3 结束语

本文基于IBIS模型,采用ADS软件模拟了高速比较器+两级信号扇出buffer+比较器产生80路脉冲信号,初步获得了脉冲信号源幅值、抖动和延迟等参数,并结合实际,设计了RC延迟电路,结果表明:1)使用本方案可获得80路触发信号,理论信号延迟时间<2.6 ns,抖动<11 ps,幅值1.97 V,前沿997 ps(负载50 Ω),满足示波器外触发信号要求;2)IBIS模型能较好模拟器件输入输出特征,结合ADS信号仿真环境,可完成系统输入输出过程的仿真,为硬件设计和参数估算提供参考依据。