一种模拟单粒子瞬态产生和测量方法

2020-11-03何怡刚周健波张钟韬

何怡刚,赵 明,周健波,张钟韬

(合肥工业大学 电气与自动化工程学院,合肥 230009)

0 引言

随着集成电路工艺进入深亚微米时代,特征尺寸的减少以及时钟频率的提高都使得空间环境器件的单粒子瞬态脉冲(SET,single event transient)效应变得越来越严重,甚至成为系统产生软错误的主要来源[1-2]。为了评估集成电路的单粒子瞬态效应,目前主要的方法是辐射实验测量方法、模型分析计算方法、仿真软件模拟方法和基于硬件的模拟方法[3],辐射实验测试方法就是在地面模拟真实的单粒子效应,但是实验成本高,每批次的实验数据少。模型分析计算方法和仿真软件模拟方法不能完全模拟出单粒子效应对集成电路的影响,同时计算速度较慢,所以相比于前三种方法,基于硬件的模拟方法一般是利用FPGA进行硬件加速,在大规模电路应用中,具有速度快、成本低的优点,缺点是精度较低。文献[3-4]使用FPGA在基于量化组合逻辑门延迟思想和扫描测试的方法,去评估数字电路软错误敏感性,但是忽略了FPGA中瞬态脉冲在电路传播过程中可能会发生脉冲压缩效应或者脉冲展宽效应[5]。根据相关实验数据表明单粒子瞬态效应造成器件的瞬态脉冲宽度在150 ps~2 ns之间[6]。为了提高基于硬件模拟方法的精度,可以从模拟单粒子瞬态脉冲的产生以及在FPGA中的传输特性方面进行研究。

在FPGA内部模拟单粒子瞬态脉冲的产生,现在普遍使用三种方法:辐射试验、激光试验和电注入试验[7],前两种方法虽然贴近单粒子瞬态效应产生瞬态脉冲的实际环境,但是其只能观测到瞬态脉冲在电路中产生的结果,无法很精确地确定瞬态脉冲注入时间和位置,而且其有很高的成本,相反电注入试验方法用注入的脉冲来模拟真实粒子的撞击,其成本较低,并且对于要注入时间和地点都能实现良好的控制,能准确地确定注入时间及位置,最适合本文的模拟瞬态脉冲的产生和分析。

针对瞬态脉冲宽度在皮秒级别,本文充分利用FPGA中丰富的原语资源,提出了一种基于IDELAY2延迟元件的电脉冲注入和测量方法,在不改变系统布局布线的情况下,可以实现连续产生宽度增量为78ps的瞬态脉冲,宽度基本覆盖深亚微米下瞬态脉冲宽度范围,同时利用IDELAY2延迟元件在FPGA内部设计瞬态脉冲宽度测量电路,研究8种不同的门电路逻辑链对脉冲宽度的影响,结果显示了门类型、输入脉冲类型和输入脉冲宽度对传播脉冲宽度的影响。

1 SET注入和测量技术

瞬态脉冲的电注入方法就是在电路的指定节点注入瞬态脉冲,注入脉冲的方法分为外部电注入和内部电注入,采用外部电注入的方法就是在FPGA外部产生瞬态脉冲,通过FPGA的输入输出引脚(I/O Element)结构进入FPGA,但是脉冲在通过IOE结构时会有滤波的现象,所以本文采用内部电注入的方法,避免造成输入脉冲宽度的变化。当组合逻辑电路中发生SET时,产生的瞬态脉冲有两种类型,即正脉冲(010)和负脉冲(101),本文将分别对它们进行讨论。

1.1 SET脉冲产生单元

本文的SET脉冲产生单元是在FPGA中的IDELAY2延迟元件原语的基础上实现的。IDELAY2延迟元件是具有抽头分辨率的31抽头环绕式延迟原语,可以将其应用于组合输入路径或者已定义的输入路径或者两者都有,也可以直接从FPGA逻辑中对其进行访问,它是Xilinx 的FPGA底层延迟单元,可以在单个输入引脚的基础上延迟输入信号,抽头延迟分辨率可以通过使用IDELAYCTRL原语作为参考时钟连续校准,如式(1)所示:

Tapdelay=1/(32*2*Fref)

(1)

式(1)中,Fref是参考时钟频率,Tapdelay是抽头延迟分辨率,抽头值和抽头延迟分辨率的乘积就是相对于抽头值为0时的总延迟时间。本文中选择的参考时钟频率为200 MHz,由于抽头分辨率是通过IDELAYCTRL进行校准的,所以抽头分辨率为78 ps,如果IDELAY2原语被实例化,则IDELAYCTRL模块也必须被实例化,IDELAYCTRL模块连续校准单个延迟抽头IDELAY2区域,以减少工艺、电压和温度变化的影响,所以即使环境变化,抽头延迟单元的抽头分辨率也会非常精确和稳定。

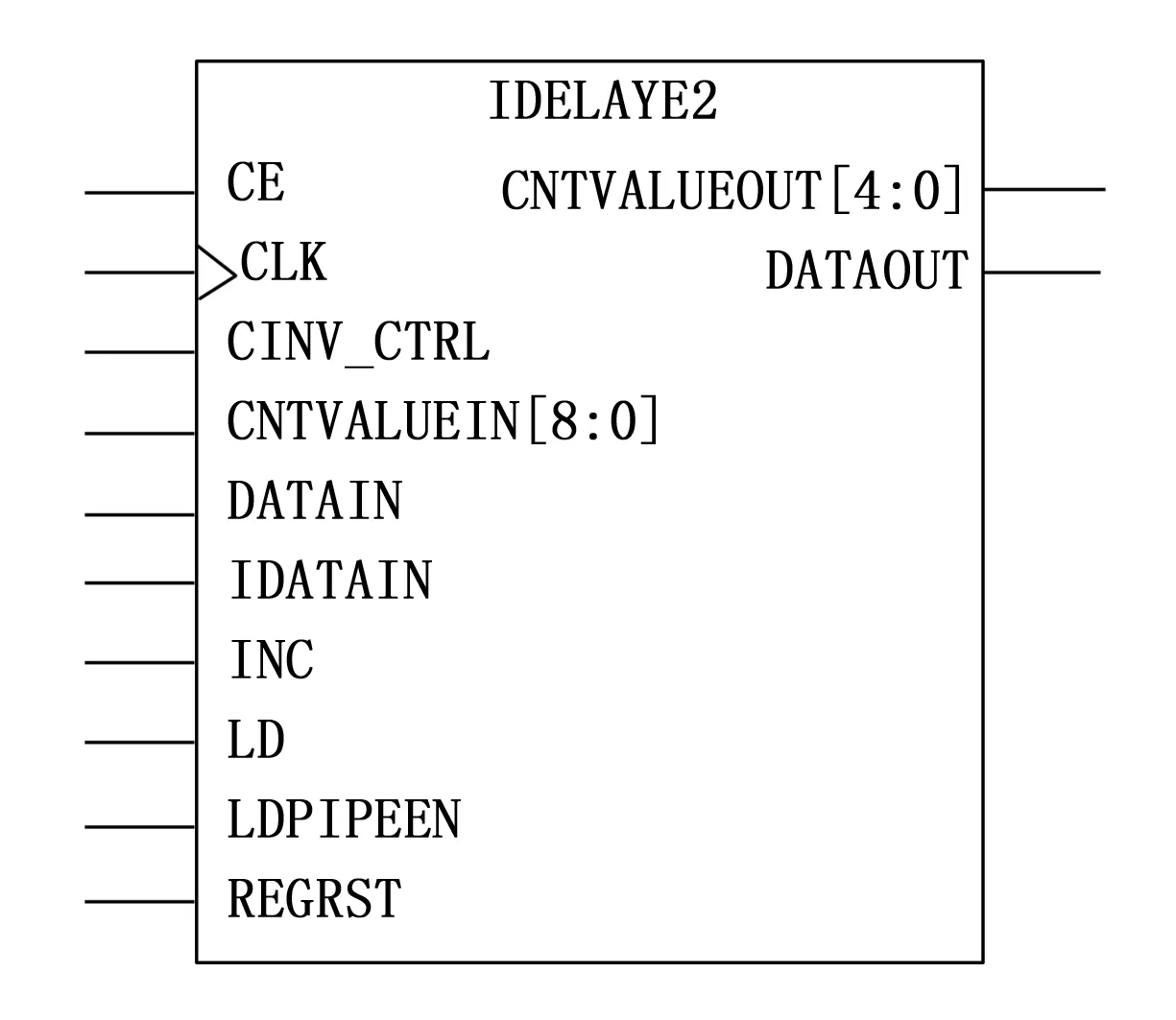

IDELAY2延迟元件抽头延迟线属性包括FIXED,VARIABLE, VAR_LOAD和VAR_LOAD_PIPE四种属性,本文选择“VARIABLE”属性,在此属性下,可以在IDELAY2延迟元件的可用端口,如图1所示,在CLK时钟信号的上升沿,采样CE和INC的值,动态增加或者减少IDELAY2延迟元件的延迟抽头值。

图1 IDELAY2延迟元件

为了评估抽头延迟单元IDELAY2的精度和稳定性,设计了环形振荡器和IDELAY2延迟元件组成的验证电路,如图2所示,整个电路由三个反相器、IDELAY2延迟元件和一个与门电路组成,在静态下,任何一个反相器的输入和输出都不可能稳定在高电平或低电平,只能在高低电平之间变化。假设一个反相器的延迟时间为t1,一个门电路的延迟时间为t2,IDELAY2延迟元件的延迟时间为t3,则总的延迟时间为3*t1+t2+t3,整个延迟电路的振荡周期为2*(3*t1+t2+t3),因为IDELAY2延迟元件的延迟时间取决于抽头值,所以通过增加抽头值,研究其导致的振荡周期增加量。具体的做法就是在IDELAY2的抽头值为0时,使能信号置位为高电平,在图2中的测量信号点处,测量一定数量上升沿所需的时间,这个数值可以通过USB-UAR芯片传输到PC端的串口通信软件上得到,进而计算出单个振荡周期值。在抽头值每次增加一时,IDELAY2延迟单元的延迟时间增加量为Δt3,与之前抽头值的振荡周期相比,将得到新的振荡周期增加量为2*Δt3,抽头值最大可以达到31,就可以计算31个新的振荡周期增加量。在抽头值每增加一时,也就是IDELAY2延迟元件的延迟时间增加78 ps,整个振荡周期理论的增加量是156 ps,如图3所示,得到的是IDELAY2延迟元件造成的周期增加量,结果表明了IDELAY2延迟元件的精度和可靠性。

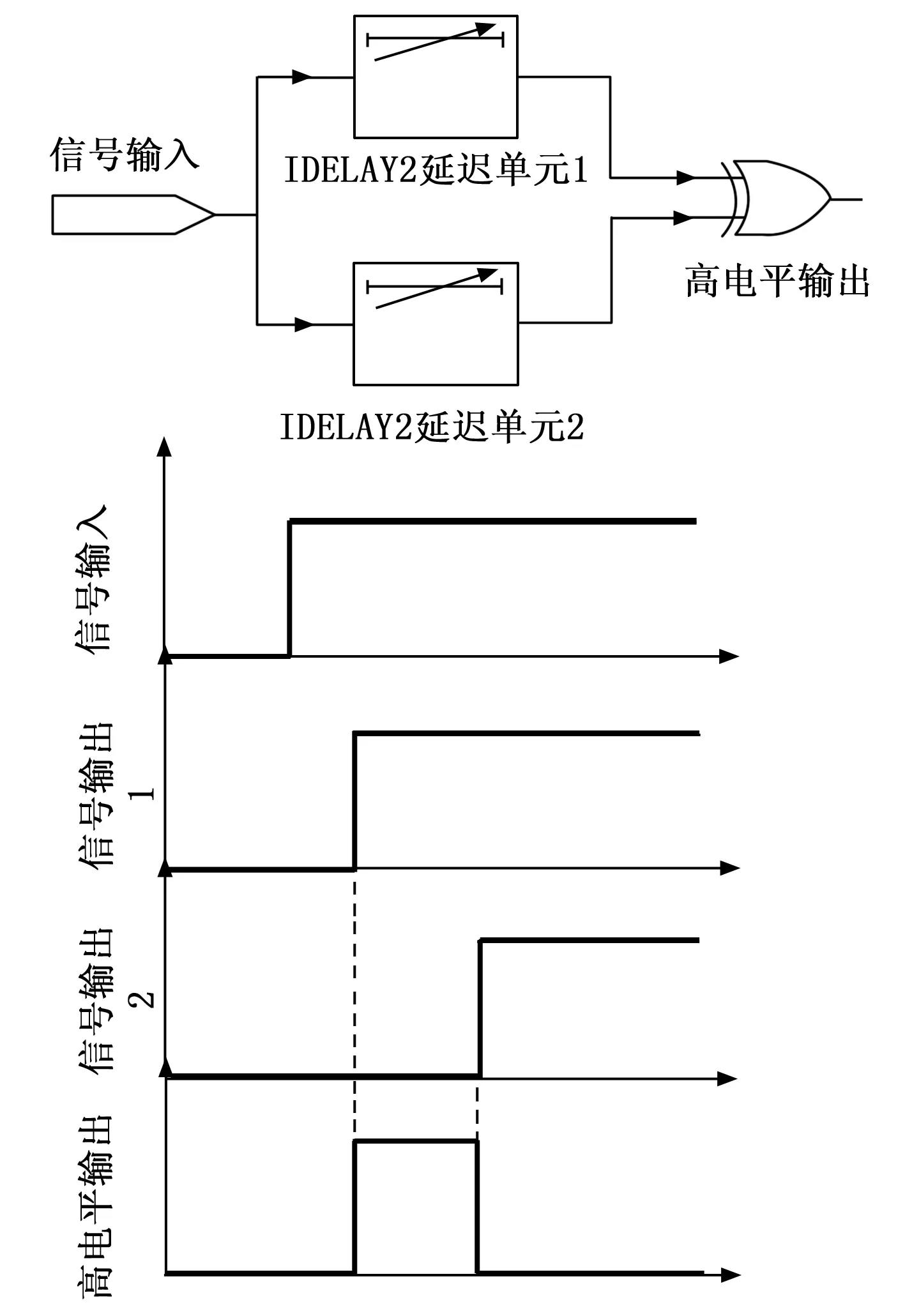

SET脉冲产生单元电路由两个IDELAY2延迟元件和一个门电路组成,如图4所示。当有一个上升沿信号输入时,信号会通过两个IDELAY2延迟元件,通过设置两个IDELAY2延迟元件不同的抽头值,延迟不同的时间,延迟后的信号通过XOR异或门产生一个正脉冲(0-1-0),产生脉冲的宽度取决于两个IDELAY2延迟元件抽头值的差。同样为了得到一个负脉冲(1-0-1),可以将延迟后的信号通过XNOR异或非门,产生负脉冲的宽度也取决于两个IDELAY2延迟元件抽头值的差。在需要改变抽头值时,只需要改变CE和INC的值,就可以在不改变系统布局布线的情况下,通过SET脉冲产生单元电路连续调教脉冲宽度,并且脉冲宽度的单次调节步长是78 ps。瞬态脉冲产生单元电路产生的瞬态脉冲可以作为信号传播模块的输入信号,也可以用瞬态脉冲测量模块直接对瞬态脉冲进行测量,不需要进行放大或转化为其他形式。

图2 IDELAY2延迟验证电路

图3 IDELAY2延迟单元周期增加量

图4 SET正脉冲(0-1-0)产生电路

1.2 信号传播单元

为了表征SET脉冲传播过程中脉冲宽度的变化,根据典型电路的情况,将and、or、xor、buf、nor、nand和inv分别单独组成相同长度的门电路逻辑链,在链的开始处注入产生的SET脉冲,并在链尾得到遍历完逻辑链的脉冲。为了将脉冲传播不受逻辑屏蔽的影响,到达脉冲测量装置前,所有逻辑门的其他输入均设置为未屏蔽状态,将and和nand第二个输入设置为1,or和nor第二个输入设置为0,对于xor,将分别考虑第二个输入为0和1两种情况。通过手动放置和布线,确保了信号传播单元不同逻辑链有相同的布局和布线,可以得到更准确的结果,排除其他因素的影响。

1.3 SET脉冲测量单元

对于逻辑链链尾SET脉冲宽度的测量,文献[8]选择使用示波器,但是由于SET脉冲经过IOE(I/O Element)输出时,可能会发生脉冲失真,进而影响所测SET脉冲宽度的准确性,因此本文选择在FPGA内部测量脉冲宽度,如图5所示。

图5 SET正脉冲(0-1-0)测量电路

SET脉冲测量电路也是在IDELAY2延迟元件原语的基础上实现的,它包括两个IDELAY2延迟元件和一个与门电路组成,其中IDELAY2延迟元件的抽头延迟线属性是“VARIABLE”,逻辑链链尾脉冲通过设置两个抽头值不同的IDELAY2延迟单元,在两个抽头值差不断增加时,对于正脉冲(0-1-0),两个IDELAY2延迟元件的输出“与”门结果中刚好没有检测到高电平,则说明两个脉冲的相位相差了脉冲宽度的长度。对于负脉冲(1-0-1),两个IDELAY2延迟元件的输出“或”门结果中刚好没有检测到低电平,则说明两个脉冲的相位相差了脉冲宽度的长度。

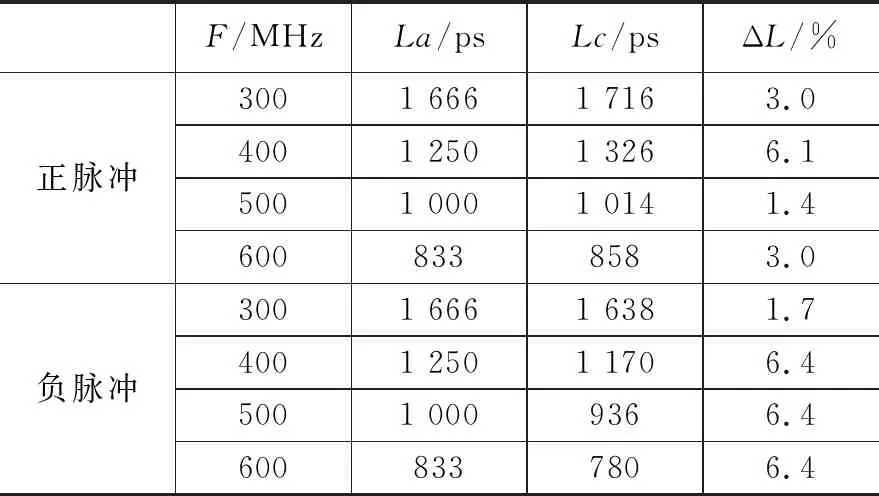

为了验证SET脉冲测量单元的准确性,本文使用SET脉冲测量单元去测量占空比为50%的不同周期信号的正脉冲宽度和负脉冲宽度,表1为测量结果,其中F为信号频率,La表示正脉冲和负脉冲的实际宽度,Lc表示用SET脉冲测量单元得到的脉冲宽度,|ΔL|表示测量值与理论值的误差率,计算公式如式(2):

ΔL= |La-Lc|/La (2)

从表1中可以看出,对于脉冲的宽度测量值和宽度实际值之间误差ΔL均小于7%,同时在对正脉冲和负脉冲的分别测量误差中,发现SET脉冲测量单元对正脉冲的测量误差低于负脉冲的测量误差。

2 实验结果

为了研究SET瞬态脉冲在FPGA逻辑门中的传播特性,使用Xlinx的 Vivado软件分别实现50个and,or,xor,buf,nor,nand,inv相连的门电路逻辑链,考虑到FPGA中不存在门的概念,因此将查找表(LUT)配置成所需要功能的门,将SET脉冲进入不同门电路逻辑链中。为了研究SET瞬态脉冲通过门电路逻辑链传播时的脉冲变化,在逻辑链的输入处注入不同宽度的正脉冲(0-1-0)或负脉冲(1-0-1),并在逻辑链的输出处测量SET瞬态脉冲宽度,而传播引起的脉冲失真(PIPD)等于在链输出处测量脉冲宽度和输入处测量脉冲宽度的差值,当PIPD值为正时,说明脉冲展宽,反之则说明脉冲压缩。

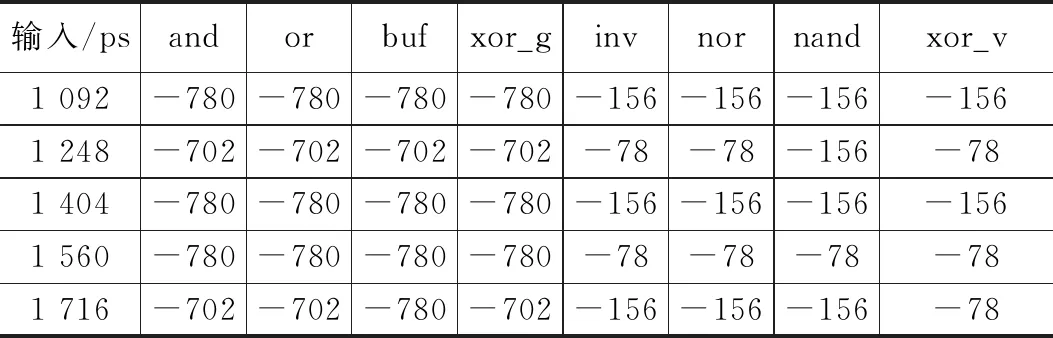

2.1 正脉冲(0-1-0)的传播特性

根据是否是产生相反逻辑的门,可以将8个逻辑链分为反向逻辑链和非反向逻辑链,随着输入脉冲宽度的增加,结果如表2所示。在输入SET瞬态脉冲是正脉冲(0-1-0)的情况下,脉冲传播到非反向逻辑链(例如and,or,buf,xor_g)时,脉冲的宽度增量PIPD为正且脉冲宽度有明显增加。而在SET瞬态脉冲传播到反向逻辑链(例如inv,nor,nand,xor_v)时,脉冲的宽度增量PIPD相对于非反向逻辑链宽度增量PIPD,脉冲宽度变化较小,说明正脉冲经过非反向逻辑链时,脉冲展宽能力较强。随着逻辑链初始输入脉冲宽度的增加,无论传播到反向逻辑链还是非反向逻辑链,脉冲宽度的增量PIPD几乎保持不变,说明正脉冲宽度的增量PIPD与初始输入脉冲宽度无关。

表2 正脉冲宽度增量(PIPD)

2.2 负脉冲(1-0-1)的传播特性

在逻辑链的输入是负脉冲(1-0-1)的情况下,随着脉冲宽度的增加,结果如表3所示,SET瞬态脉冲传播到逻辑链链尾时,脉冲宽度增量PIPD为负数,说明瞬态脉冲宽度在变小。在经过非反向逻辑链(例如and,or,buf,xor_g)时,脉冲宽度的减少量比经过反向逻辑链(例如inv,nor,nand,xor_v)时脉冲宽度减少量有明显的增加,说明负脉冲经过非反向逻辑链时,脉冲压缩能力较强。但是随初始输入SET负脉冲宽度的增加,脉冲宽度增量PIPD基本保持不变,说明负脉冲的脉冲宽度增量PIPD和初始输入负脉冲宽度无关。

表3 负脉冲宽度增量(PIPD)

从表2和表3中可以看出,在输入是正脉冲时,脉冲会发生展宽,而输入是负脉冲时,脉冲会发生压缩,但是无论输入是正脉冲还是负脉冲,在同一类型输入脉冲下,反向逻辑链中的4个门电路的PIPD的值没有显著的差别,非反向逻辑链中的4个门电路的PIPD的值没有明显差别,说明脉冲宽度的增加或减少与输入脉冲类型和是否是产生相反逻辑的门有关。

3 结束语

本文提出了一种基于IDELAY2延迟元件原语的单粒子瞬态脉冲产生和测量方法,在不改变系统布局布线的情况下,可以连续产生宽度增量为78 ps的瞬态脉冲,同时可以在FPGA内部测量瞬态脉冲的宽度并且测量的宽度误差在7%以下,有效地解决了脉冲经过IOB的滤波现象。在瞬态脉冲传播过程中,瞬态脉冲类型和门电路逻辑链类型对脉冲宽度传播都有影响,初始输入脉冲宽度对脉冲宽度传播没有影响。本文研究了瞬态脉冲在SRAM型FPGA中的传播特性,在以后研究中会用来提高运用FPGA等硬件方法模拟集成电路软错误的可靠性。