伪随机测试激励信号设计

2020-10-20孙永建秦鹏唐景华

孙永建 秦鹏 唐景华

摘要:模数混合电路的内建自测试(BIST)研究是近些年比较有挑战的,其中如何以较小的硬件开销获得模拟激励信号以及数据响应分析比较关键。本文将以伪随机信号作为研究对象,对BIST结构的激励模块进行设计伪随机信号,并在QuartusⅡ里进行仿真验证,为后续混合信号BIST结构设计打下基础。

关键词:BIST;测试激励;LFSR

中图分类号:TN407文献标识码:A文章编号:1672-9129(2020)07-0076-02

Abstract: The study of modular hybrid circuit built-in self-testing (BIST) is challenging in recent years, among which how to obtain analog excitation signal and data response analysis with less hardware cost is key. This article will take the pseudo random signal as the research object, the incentive of BIST structure module design pseudo random signal, and Quartus Ⅱ simulation verification, lay the foundation for subsequent mixed-signal BIST structure design.

Key words: BIST; Test incentives; LFSR

1引言

内建自测试(BIST)是由测试电路自身生成测试激励信号,作用于电路本身并根据响应来进行测试的方法[1],是一種很重要的测试方法。若测试结构中的测试激励为零均值的高斯随机信号时,不仅能简化求取各阶累积量谱的计算[2],而且高斯随机信号在性质上接近白噪声,其带宽和幅度都可以控制,可以保证对被测电路的持续激励,所以采用高斯随机信号作为某混合信号BIST结构中的激励信号。但是设计服从高斯分布的随机信号比较复杂而且在设计中是无法得到完全服从高斯分布的激励信号。

2激励模块设计

2.1 激励结构。伪随机信号在现实应用中通常采用线性移位寄存器序列(M序列)来产生,具有十分接近白噪声的性质,因此又称伪随机信号为伪高斯信号。激励生成的结构如图1所示,包含控制信号、线性反馈移位寄存器(LFSR)[3]和DAC三部分组成。当BIST控制器使能有效时,激励内部的控制器则产生LFSR使能信号,使得LFSR开始移位输出,并同时给DAC控制时钟信号,DAC输出的模拟信号就是伪随机信号。

2.2 LFSR设计。如果n元布尔函数 f(x1,x2,…,xn)可以表示成n个变元x1,x2,x3,…,xn的线性奇次函数:f(x1,x2,…,xn)=cnxn+cn-1xn-1+…c1x1f(x1,x2,…,xn)=cnxn+cn-1xn-1+…c1x1其中ci=0或1,则以f(x1,x2,…,xn)为反馈函数的移位寄存器就叫做线性反馈移位寄存器(LFSR)[4]。图2为n级线性反馈移位寄存器的一般结构形式。

其中A1,A2,…,An是寄存器串联成的移位寄存器;hi是反馈控制,hi∈0,1。为0不存在,为1则存在反馈控制,线性反馈移位寄存器的特征多项式为:

h(x)=xn+h1xn-1+h2xn-2+…+hn-1x+1(1)

产生线性反馈移位寄存器序列的n级移位寄存器,其特征多项式必须是n次本原多项式,也就是说特征多项式与输出序列的周期有密切的关系。要设计LFSR,并使之输出序列具有最大的周期性,必须要找到本原多项式[5]。

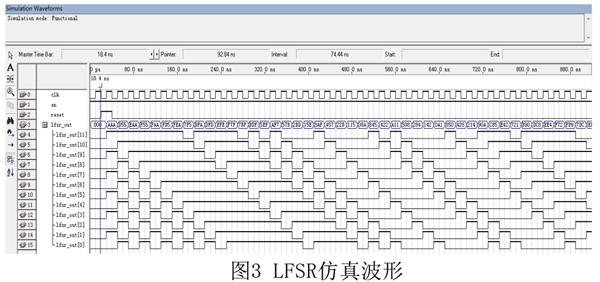

以12Bit的TI芯片DAC902芯片(转换速度最高达到165M)为例,最少需要12bit位移位寄存器。选取LFSR本原多项式为: x12+x6+x4+x+1,设计线性反馈移位寄存器取其并行输出作为DAC的编码,在QuartusII环境下用Verilog HDL硬件描述语言设计,输出的序列仿真如图3所示。

该序列发生器的输出信号是一个数字随机信号,在设计中,通过D/A转换器得到模拟信号。若被测电路是数字输入,不需要再加D/A转换器,可根据实际需要直接将数字信号接到被测电路。

2.3 控制设计仿真

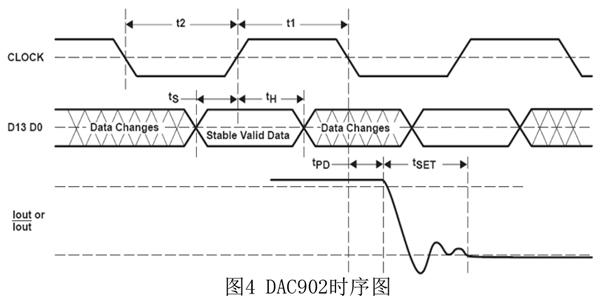

由图1可知,激励模块不仅要设计LFSR产生随机序列,还要产生控制时钟来控制DAC工作,DAC902控制时序图如图4所示。

DAC控制起来比较容易,使能LFSR后,产生M序列并行输出到DAC数据端,然后控制器输出DAC控制时钟,上升沿时数据有效,DAC转换输出信号。用硬件描述语言对激励模块数字部分进行设计,功能仿真如图5所示。

从图5中可以看出,在复位信号无效(即高电平)时,在系统时钟的驱动下,模块的输入使能置位有效时,LFSR并行有数据输出到DAC,并同时输出DAC控制时钟,来驱动DAC工作。

3结论

本文对BIST结构的测试激励进行设计,通过仿真结果可知,能够实现ADC的控制信号和数据,产生伪随机测试激励信号,为后续混合信号BIST测试结构设计打下基础。

参考文献:

[1]陈佳楠,马永涛,李松等. 多目标优化的多存储器内建自测试[J].电子测量与仪器学报.2020,01(34):193-198.

[2]孙永建,加等.混合BIST对象建模及结构分析[J].国外电子测量技术2010.05(29):21-23.

[3]刘伟,雷加.基于伪随机测试的模数混合信号内建自测试法[J].计算机工程与应用.2008,44(33).

[4]肖国镇,梁传甲,王育民.伪随机序列及其应用[M].国防工业出版社.1985.3

[5]王荣阳,刘福浩,李向阳 紫外光通信误码率测试系统设计[J].半导体光电.2012.05:707-710

[6]杨舟,王红,杨士元.混合信号SOC联合测试方案[J].清华大学学报(自然科学版),2011.5(S1):1381-1387

[7]安宝森等.BIST电路在嵌入式非易失性存储器可靠性测试中的应用[J].电子设计工程.2019,06(11):33-36

[8]谈恩民,贾亚平.用于数模混合电路中ADC测试的IP核设计[J].北京: 微电子学, 2016.12(6):849-851

作者简介:孙永建(1986—),男,研究方向:混合信号电路测试研究、嵌入式系统开发。