基于授权机制的抗扫描旁路攻击方法研究①

2020-10-19卢新元陈华军

卢新元 陈华军 许 超 王 剑*

(*计算机体系结构国家重点实验室(中国科学院计算技术研究所) 北京 100190)(**中国科学院计算技术研究所 北京 100190)(***中国科学院大学 北京 100049)(****龙芯中科技术有限公司 北京 100190)

0 引 言

伴随着现代通信以及网络技术的快速发展,信息安全问题变得尤为重要,通过加密算法加密传输或存储数据成为保证信息安全的重要手段。加密方式通常分为软件加密和硬件加密2种,通常软件加密的方式加密效率较低,因此基于硬件加密的芯片设计成为近些年信息安全领域研究和应用的热点。为有效地检测加密芯片的可靠性,可测试性设计必不可少。扫描设计作为广泛应用的可测性设计方法之一,能够有效提高电路的可控制性和可观测性,保证测试覆盖率。扫描设计能够有效地提高加密芯片可测试能力,但也降低了其安全性。有研究表明,采用数据加密标准(data encryption standard,DES)或改进加密标准(advanced encryption standard,AES)且带有扫描设计的加密芯片都可以被扫描旁路攻击方式[1]获取加密信息。

为保护密码芯片免于扫描旁路攻击,文献[2]提出了基于模式切换复位的保护策略,但在文献[3,4]中该策略被证明对只基于测试模式的攻击方法无效。文献[5]提出了基于线性反馈移位寄存器(linear feedback shift register, LFSR)结构的内建自测试方法,可以有效保障密码芯片的安全,但该方案不利于故障诊断。文献[6]提出了将保存密钥信息的触发器不放在扫描链上的部分扫描设计方法,能有效地防止密钥信息泄露,但会降低加密电路部分的可测试性。文献[7]提出了增加镜像密钥寄存器的方法,测试模式下可以用镜像密钥寄存器将密钥同加密模块隔离,但该方法需要在模式切换时进行系统复位,无法支持在线测试。文献[8]中的安全扫描测试结构为保证测试模式下密钥被屏蔽,只能有一拍捕获时钟,虽然可以支持在线测试,但无法支持延迟故障测试。文献[9]中提出了可以支持延迟故障测试的结构设计,但由于测试模式下密钥会被屏蔽,依然存在测试模式下密钥故障无法检测的问题。

不同于上述屏蔽密钥的方法,文献[10-16]提出了另一种保障密码芯片安全的方法,即混淆观测数据。文献[10]通过动态打乱子扫描链顺序的方法实现观测数据混淆,但已被证明可以用签名攻击破解。文献[11,12]提出了在扫描链中添加反相器或异或门的方法,但也被证明可以通过复位攻击等方法破解。文献[13]选择通过添加LFSR结构动态改变异或门在扫描链上的位置,该方法可以抵抗现有的扫描旁路攻击方法,但会带来较大的面积开销。文献[14]提出扫描数据加解密的方法,未授权的使用者移出的扫描数据将会被加密,但该方法会增加测试时间。文献[15]提出了静态混淆观测数据的方法,通过添加控制器和一组移位寄存器(shift register,SR)对扫描链上部分触发器的扫描使能进行控制,只有当SR中移入正确的测试密钥才能保证被控制的扫描触发器进行正确的移位操作,但该方法可以用测试模式下签名攻击破解。文献[16]提出了动态混淆观测数据的方法,动态改变被选择的扫描触发器,很大程度上增加了攻击的难度,但也无法证明这种动态混淆观测数据的方法是不可逆的。

针对以上方法存在的问题,本文提出一种基于授权机制的抗扫描旁路攻击方法,使用者需要在功能模式下输入预设的功能指令序列进行安全测试权限认证,在获取安全测试授权后,才能在安全测试模式下进行扫描测试。该方法不需要添加用来保存测试密钥的触发器,因此只需要很少量的面积开销,并且不会带来额外的测试时间开销。本文所提出的基于授权机制的抗扫描旁路攻击方法既能够保证无法被现有攻击方法所破解,又可以检测到密钥故障,在保证安全性的同时,不会损失故障覆盖率。

1 背景介绍

1.1 扫描测试原理

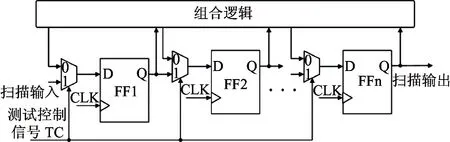

基于扫描链的扫描测试是可测试性设计中的一种关键测试方法,能够为芯片提供良好的可控制性和可观测性。扫描链结构如图1所示,通过在普通触发器前增加一个选择器的方式,将其串联成一条由多个触发器组成的长链。选择器的2个输入,分别来自于扫描输入(scan in,SI)和功能逻辑,并由测试控制(test control,TC)信号控制选择器选择数据输入来源。在测试模式下,首先将TC置1,此时芯片处于移位模式,多拍时钟后将扫描输入值移入链上触发器中。然后将TC置0,芯片从移位模式切换到捕获模式,经过一拍或多拍时钟将功能逻辑值捕获到触发器中。最后再次将TC置1,将链上触发器中的值移出观测[17]。功能模式下,TC值保持为0,扫描链上触发器的数据输入来源于功能逻辑。

图1 扫描链结构图

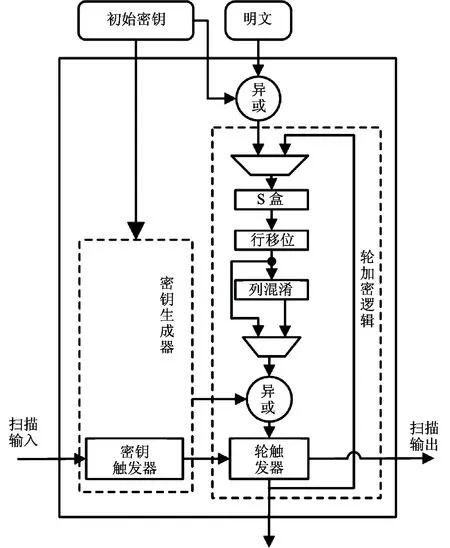

1.2 AES加密结构

相比于DES加密算法,AES加密算法因安全性较高、迭代对称而被广泛应用。以AES加密芯片为例,其加密模块结构如图2所示。加密过程中,首先将初始密钥和明文数据送入加密结构中进行第一次的异或操作,再将异或结果送入轮加密逻辑中。轮加密逻辑是AES加密结构的核心部件,轮加密逻辑中主要包括3个顺序完成的操作,分别是S盒、行移位和列混合。列混合完成的数据会同密钥生成器中产生的密钥再进行一次异或操作,并将结果存放在轮触发器中,这个过程称之为一次完整的轮加密操作。之后轮加密逻辑会多次重复上述的轮操作,直至最终加密完成。每一轮的数据都来源于上一轮操作中轮触发器保存的值,每一次轮加密操作中的密钥都由密钥生成器重新产生,并保存在密钥触发器中。根据密钥的长度不同,轮加密的次数也会不同,一般128位的密钥设计需要10次的轮加密操作,能够抵抗已知所有的数学攻击方法。

图2 具有扫描链的AES加密模块结构

在AES加密芯片的可测试性设计中为了满足覆盖率的需求,通常需要将存放加密中间状态值的密钥触发器和轮触发器放在扫描链中,本文将密钥触发器和轮触发器统称为加密相关触发器。在功能模式下,芯片可以进行正常的加密操作,加密的中间状态值保存在加密相关触发器中。当由功能模式切换到测试模式后,可以通过扫描链将加密相关触发器的值移出观测。攻击者利用该特性,在功能模式下输入一些特殊的明文,然后在第一次的轮操作完成后切换到测试模式下,将加密相关触发器的中间状态值移出观测,这样攻击者可以很容易获取密钥。

2 基于授权机制的安全扫描设计

2.1 模式切换机制

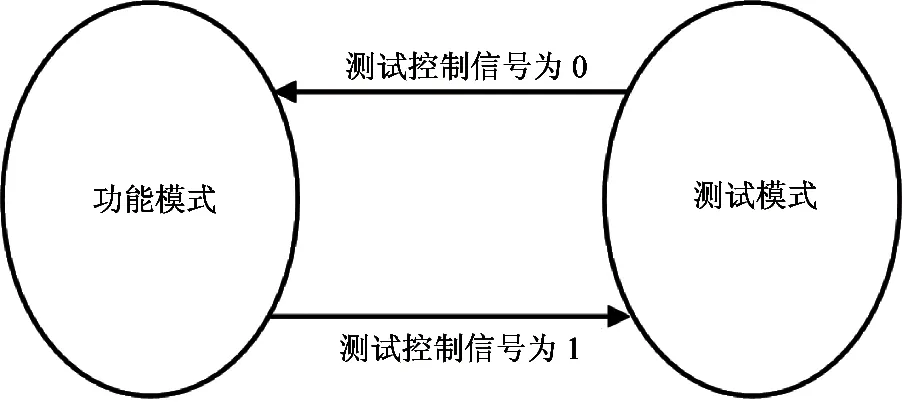

传统的无安全设计的芯片模式切换关系如图3(a)所示。

当系统复位完成后,由测试控制信号TC控制芯片的模式切换。TC为0时,芯片进入功能模式,可以进行正常的加密运算,但无法进行扫描链移位操作。TC为1时,芯片由功能模式切换到测试模式,扫描链可以进行正常的移位和捕获操作,攻击者可通过扫描链将加密相关触发器值直接移出观测,此时芯片处于一种容易被攻击的状态,无法保障密码芯片的安全。

本文提出的改进方法如图3(b)所示,将测试模式分为安全测试模式和非安全测试模式,并增加了一个模式切换信号Trigger。当TC由0跳变到1时,芯片由功能模式切换到测试模式,此时如果Trigger信号为1,则进入安全测试模式;如果Trigger信号为0,则进入非安全测试模式。当TC信号由1跳变为0时,芯片由测试模式回归到正常的功能模式。

(a)无安全设计的模式切换

非安全测试模式下,密钥以及加密相关触发器值被屏蔽,测试者只能对其他触发器所在的扫描链进行正常的扫描测试。安全测试模式下,密钥不被屏蔽,加密相关触发器置在扫描链上可以进行正常扫描测试。

2.2 安全扫描设计的结构实现

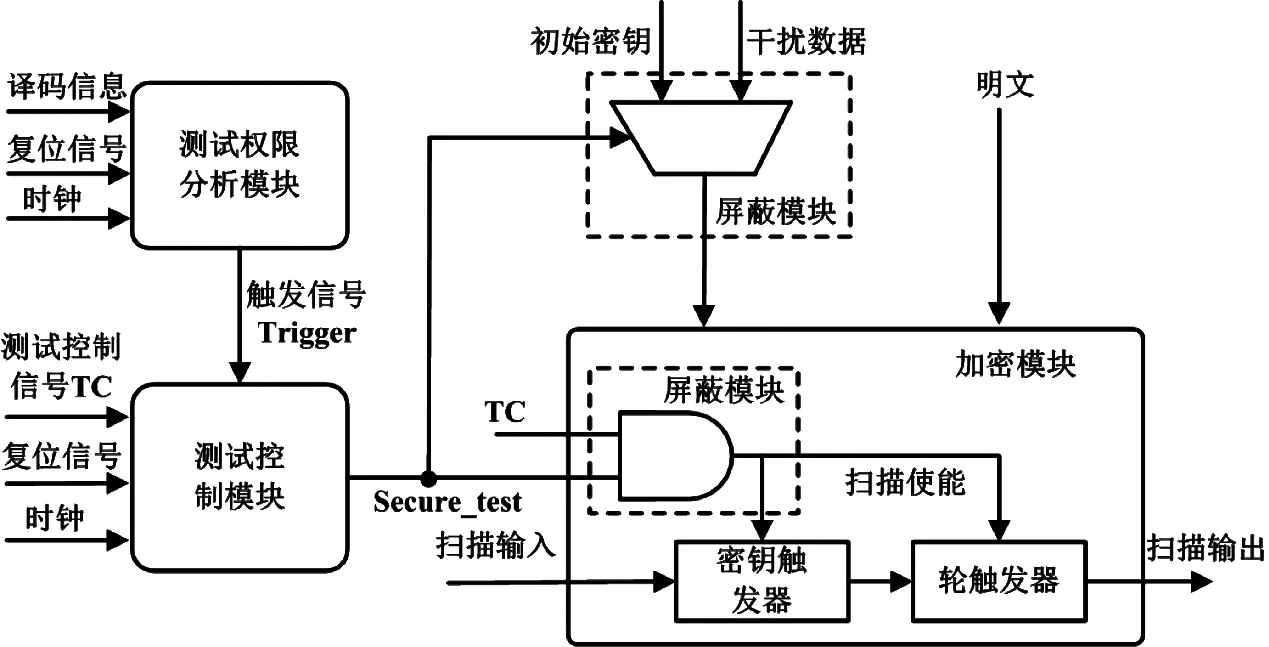

本文的安全扫描结构设计主要包括测试权限分析模块、测试控制模块以及屏蔽模块,如图4所示。

图4 安全扫描设计结构图

测试权限分析模块负责在功能模式下对测试权限进行认证,并产生Trigger信号送入测试控制模块中。测试控制模块接收测试控制信号TC以及来自于测试权限分析模块的Trigger信号,控制和实现模式切换,并产生安全测试信号Secure_test送入屏蔽模块中。最终屏蔽模块根据Secure_test的值决定是否对密钥和加密相关触发器进行屏蔽。

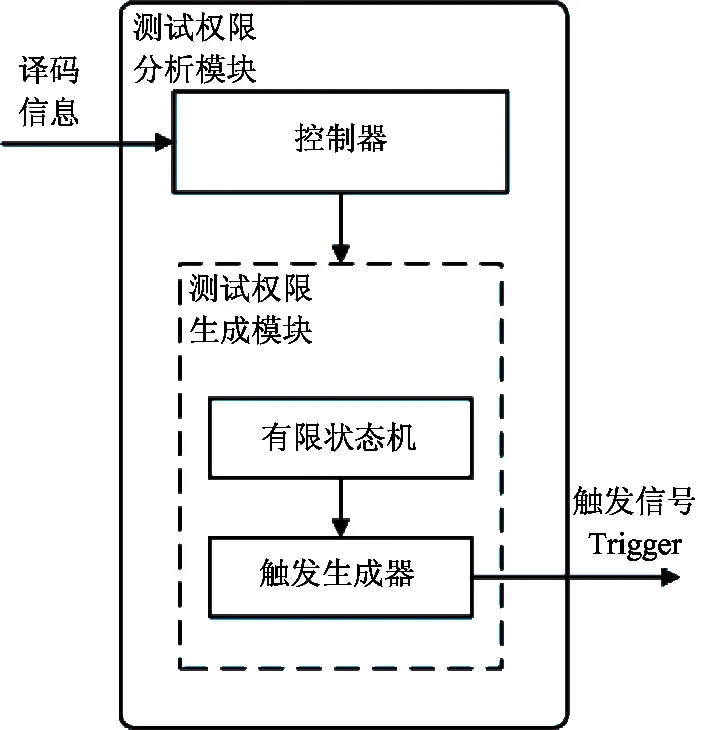

2.2.1 测试权限分析模块

测试权限分析模块主要包括控制器以及测试权限生成模块,其结构如图5所示。控制器接收并处理来自于中央处理器(central processing unit,CPU)[18]的译码信息,该译码信息为使用者输入正确的功能指令序列后CPU译码产生特定的信息,随后发出控制信号并送入测试权限生成模块中。测试权限生成模块包括一个有限状态机和一个信号生成器,由控制信号驱动有限状态机工作,当有限状态机到达特定的状态后,触发生成器负责将触发信号Trigger置1,并送入测试控制模块中。每次对系统进行复位后,触发信号Trigger会重新置0。

图5 测试权限分析模块

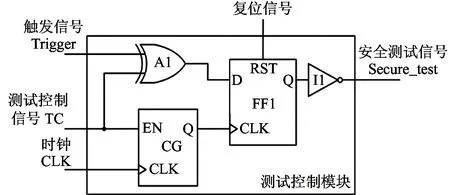

2.2.2 测试控制模块

测试控制模块在整个过程中起着核心枢纽作用,负责接收Trigger信号完成模式切换,并产生Secure_test信号实现对屏蔽模块的控制。测试控制模块由1个触发器FF1、1个时钟门控CG、1个异或门A1以及1个反相器I1组成,其结构如图6所示。触发器FF1为异步触发器,由复位信号reset进行复位。触发器的时钟端连接时钟门控CG的输出,CG的使能端EN连接测试控制信号TC。TC和触发信号Trigger连接异或门A1的两输入端,A1的输出端同触发器FF1的D端连接。触发器FF1的Q端与反相器I1输入相连,反相器输出安全测试信号Secure_test。该测试控制模块如何完成模式切换以及控制屏蔽模块将在下文3.1和3.2节中进行详细说明。

图6 测试控制模块

2.2.3 屏蔽模块

屏蔽模块包括2个部分:密钥屏蔽模块和加密相关触发器屏蔽模块,其结构如图4中虚线框内所示。密钥屏蔽模块中主要由二选一多路选择器构成。干扰数据(干扰数据位宽和密钥位宽一致)和密钥作为选择器的2个输入,安全测试信号Secure_test作为选择器的选择信号。当攻击者无法获取安全测试权限时,干扰数据会被送入加密模块中,密钥被屏蔽。

加密相关触发器屏蔽模块主要由一个与门构成,与门的其中一个输入端同安全测试信号Secure_test相连,另一个输入端则连接测试控制信号TC,并将输出结果作为加密相关触发器的扫描使能信号。该模块可以根据Secure_test的值,选择是否对加密相关触发器扫描链移出值进行屏蔽,因此当使用者没有通过测试权限分析模块的测试权限认证时,无法根据扫描链的观测值恢复密钥。

3 安全扫描设计操作流程

通过实现基于授权机制的安全扫描设计,得到安全扫描操作流程图如图7所示。

图7 安全扫描操作流程图

3.1 功能模式操作

芯片完成上电操作进入工作模式后,将TC信号置为0,芯片会进入正常的功能模式。根据图6中测试控制模块结构可知,此时测试控制模块中时钟门控CG使能EN无效,时钟无法通过CG,触发器FF1不能完成时钟沿触发而发生跳变,因此触发器Q端输出值保持复位后的值0,经过反相器I1取反后,Secure_test值为1,测试控制模块输出安全测试信号。当屏蔽模块接收到为1的Secure_test信号后,密钥屏蔽模块选择将密钥输出并送入到加密模块中。加密相关触发器屏蔽模块输出的扫描使能信号保持不变,加密相关触发器的输入来自于功能逻辑,加密模块可以进行正常的加密运算,并输出密文。注意到当TC为0时,Secure_test的值不受触发信号Trigger影响,因此无论是否在功能模式下对安全测试权限认证,功能操作都不受影响。

3.2 测试模式操作

芯片上电后,如果不预先进入功能模式下通过测试权限认证,而将TC直接置为1,则芯片会进入非安全测试模式。或者当芯片在功能模式下,使用者没有进行测试权限认证或认证未通过,则安全测试权限分析模块输出Trigger信号为0。此时,将TC信号由0置1,芯片同样会切换到非安全测试模式。非安全测试模式下,TC为1,Trigger为0,测试控制模块内异或门A1输出为1,并送到触发器FF1的D端。由于TC为1,则时钟信号可以通过CG传递到触发器FF1上,当时钟上升沿到来时,触发器FF1捕获到值1,并由Q端输出。经过反相器I1后,测试控制模块输出安全测试信号Secure_test值为0。当屏蔽模块接收到为0的Secure_test信号,密钥屏蔽模块会将干扰数据作为密钥送入加密模块中。加密相关触发器屏蔽模块输出的扫描使能信号为0,加密相关触发器无法进行正确的移位操作。因此,攻击者无法通过扫描移出值恢复密钥。

若想进入安全测试模式,需要在功能模式下进行测试权限认证。使用者输入正确的功能指令序列到CPU中,安全测试权限分析模块接收到译码信息后,将触发信号Trigger置为1。此时,将TC信号由0置1,芯片切换到安全测试模式。安全测试模式下,TC为1,Trigger也为1,异或门A1输出0并送到触发器FF1的D端。由时钟上升沿触发,触发器捕获0值并由Q端送入反相器I1中,最终测试控制模块输出值为1的Secure_test信号。密钥屏蔽模块选择密钥直接送入加密模块中。加密相关触发器屏蔽模块中输出的扫描使能信号与TC保持一致。在扫描测试过程中,需要由移位模式切换到捕获模式,TC信号由1置为0,此时Secure_test值会保持不变。因此,安全测试模式下可以支持正常的扫描测试过程,密钥和加密模块中的故障均可以被检测到。

4 实验结果及分析

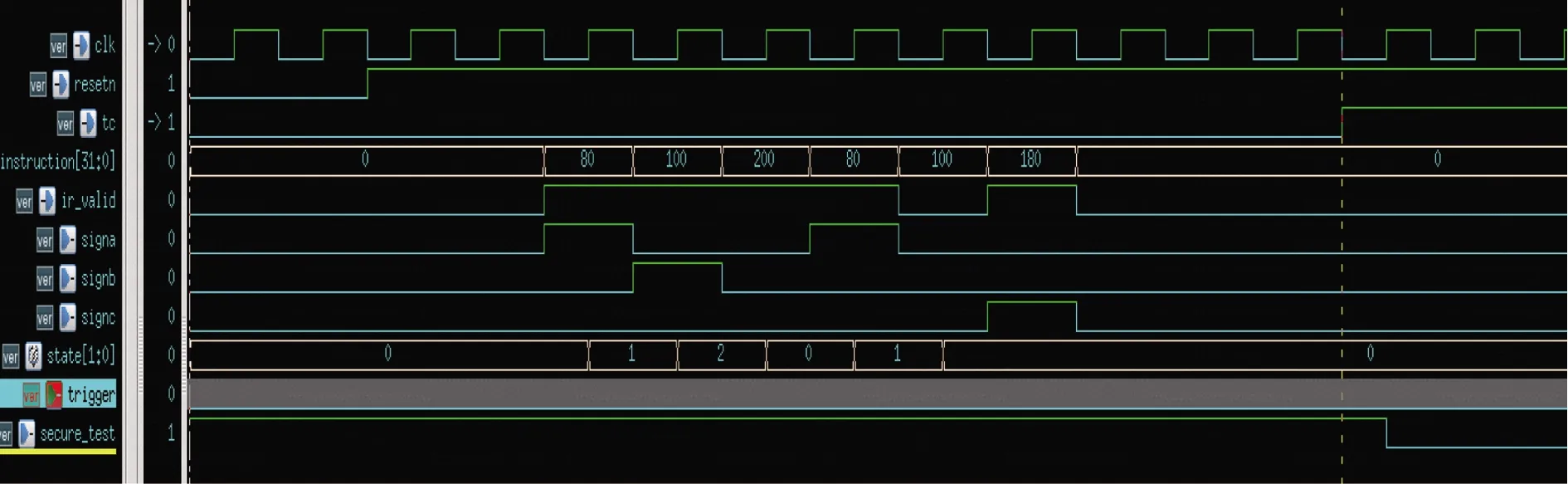

本文选取密钥位宽为128位的AES电路[19]以及龙芯某款CPU核作为实验对象进行仿真认证。实验选取的仿真工具为VCS,综合工具为设计编译器(design compiler,DC)。上述的电子设计自动化(electronics design automation,EDA)工具都在Linux环境下运行,服务器的CPU主频为2.2 GHz,内存容量为64 GB。实验选择连续3条位宽为32位的移位指令作为正确的指令序列,输入正确的指令序列后,仿真结果如图8所示。图中虚线处为TC信号跳变的时刻,跳变前电路处于功能模式,跳变后切换到测试模式。功能模式下,CPU根据指令valid信号接收并处理连续3条有效的移位指令,控制译码信号signa、signb以及signc的值连续发生跳变。信号state的值对应测试权限分析模块中状态机的不同状态,其中“0”代表初始状态,“1”代表接收到第1条正确的指令,“2”代表接收到前2条连续正确的指令,“3”代表接收到完整的指令序列。当状态机达到状态“3”后,在下一拍时钟的上升沿Trigger信号跳变为1,电路由功能模式切换到安全测试模式,Secure_test信号保持为1不变。

图8 输入正确功能指令序列的仿真结果

若输入错误的功能指令序列后,其仿真结果如图9所示。指令序列中错误或无效的指令会导致译码信号signb和signc无法正确跳变。当状态机处于状态“1”或状态“2”时,接收到不正确的指令后均会重新跳转到初始状态“0”,信号Trigger保持为0,电路由功能模式只能切换到非安全测试模式,Secure_test信号由1跳变为0。

图9 输入错误功能指令序列的仿真结果

4.1 安全性分析

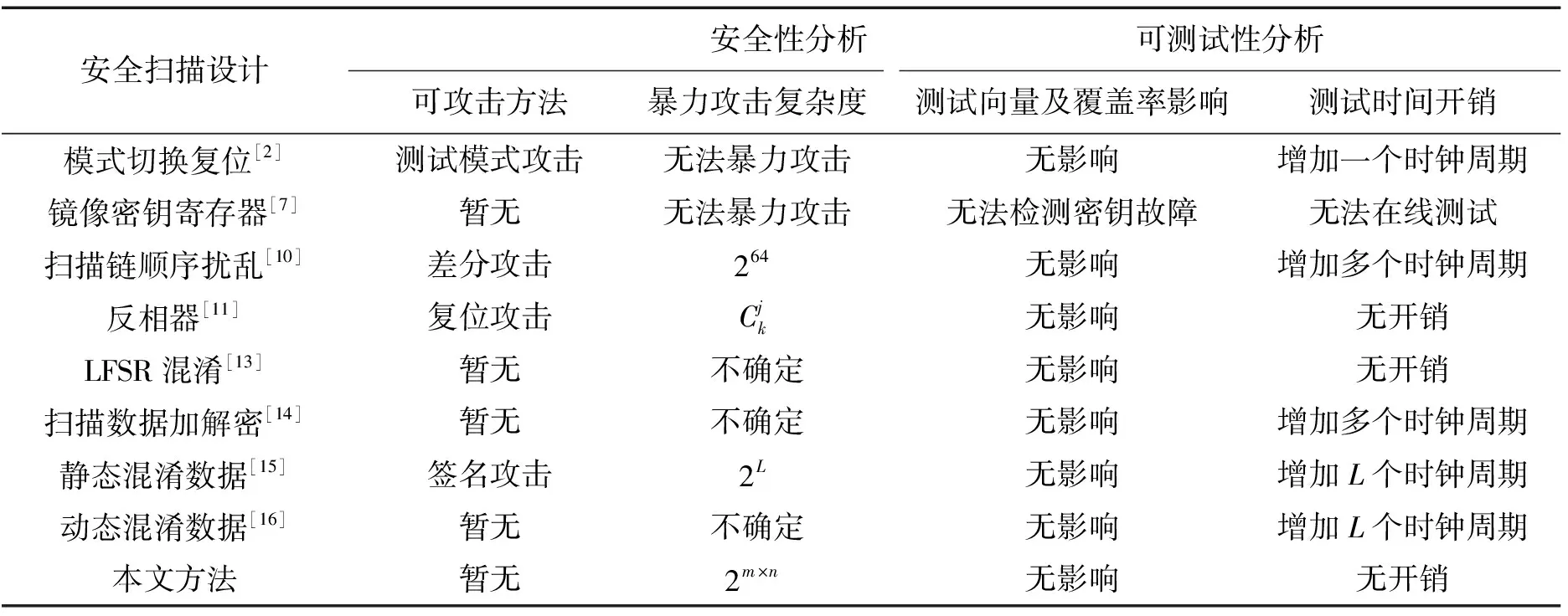

通常攻击者无法得知在进行密钥获取前,需要进入安全测试模式或如何进入安全测试模式。极端情况下,即便攻击者知道需要在功能模式下输入指令序列来触发安全测试权限分析模块生成Trigger信号,攻击者输入一段完全正确的功能指令序列的可能性也几乎为0。当安全测试权限分析模块没有将触发信号Trigger信号置为1时,攻击者永远只能由功能模式切换到非安全测试模式。此时,密钥以及加密相关触发器都被屏蔽,攻击者无法根据扫描链移出观测值恢复密钥,因此所有的已知攻击方式都无效。本文所提出的方法同引言中提到的几种经典安全扫描测试方法相比,安全性分析结果如表1所示。其中k和j分别表示添加反相器[9]方法中扫描触发器以及反相器的个数,L表示静态混淆数据[12]方法中新增移位触发器的个数,m表示功能指令序列中指令的个数,n表示指令的位宽。

表1 不同安全扫描设计的安全性和可测试性对比

4.2 可测试性分析

当测试工程师可以进入安全测试模式下进行扫描测试时,密钥的值不会被屏蔽,加密相关触发器所在扫描链也可以进行正常移位和捕获操作,密钥以及加密模块的故障均可以被检测到,因此同未进行安全扫描设计的初始芯片相比,并没有故障覆盖率的损失。

由移位模式切换捕获状态时,一拍或者多拍的捕获时钟都不会影响测试控制模块输出的Secure_test值,因此该安全扫描设计方法既支持固定性故障测试,又支持延迟故障测试,而且由于不需要修改扫描链的结构,传统的扫描链设计以及自动测试向量生成流程完全适用,生成的测试向量也不需要进行调整。本文采用的安全扫描设计同其他经典的方法相比,可测试性分析结果如表1所示。除添加反相器[9]和LFSR混淆[13]的方法,其他安全扫描设计都需要增加额外的测试时钟周期,但本文所提出的方法无需额外的测试时间开销。

4.3 面积开销分析

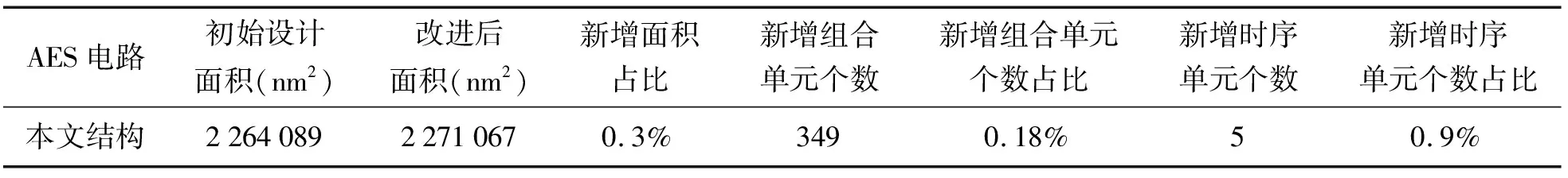

本文实验使用DC工具基于130 nm工艺进行综合和DFT设计,生成最终的网表。面积开销、组合单元以及时序单元个数统计如表2所示。其中初始设计是指未进行安全设计的DFT后的电路。

表2 面积开销统计

实验结果表明,新增的安全扫描结构面积仅约为初始设计面积的0.3%。同初始设计相比,组合单元和时序单元个数分别增加了333个和5个,占比仅为0.18%和0.9%。

5 结 论

本文提出的基于授权机制的抗扫描旁路攻击方法,在功能模式下通过功能指令序列完成安全测试授权,并根据授权认证结果选择进入非安全测试模式或安全测试模式。非安全测试模式下,密钥被屏蔽,同时加密相关触发器所在扫描链的移出观测值被混淆,因此攻击者无法恢复密钥,保证了密钥的安全性。安全测试模式下,密钥不被屏蔽,密钥从存储器读出到送入加密模块的路径上故障都可以被扫描测试检测到。同时加密模块中的触发器以及组合逻辑故障也均可以被检测到,保证了加密相关模块的故障覆盖率。另外,通过功能指令序列触发的安全测试权限认证方式,安全性高且不失灵活性。一方面,攻击者在不知道正确功能指令序列的前提下,几乎不可能通过安全测试权限认证。另一方面,设计者可以根据芯片的安全等级,改变指令序列中功能指令的种类以及个数。本方法结构实现简单,并且几乎没有面积开销,可以适用于任何带有扫描设计的密码芯片中。