基于FPGA 的m 序列发生器设计与实验

2020-09-29陈长江李卓林

翁 玲,陈长江,徐 行,李卓林,彭 睿

(河北工业大学 电气工程学院,天津 300130)

m 序列是最长线性反馈移位寄存器序列的简称,是由带线性反馈的移位寄存器产生的[1]。移位寄存器设定初始状态后,在时钟触发下,每次移位后各级寄存器会发生变化,其中任何一级寄存器的输出,随着时钟节拍的推移都会产生一个序列,该序列称为移位寄存器序列。m 序列可广泛应用于密码学、导航、通信、地质勘探等多个领域[2]。

学生在学习数字电子技术、数字逻辑电路、EDA等课程时经常会遇到带反馈的移位寄存器与硬件描述语言难以理解的问题。如何设计带反馈的移位寄存器、m 序列、Modelsim 仿真和实际应用结合在一起的综合实验是相关课程的重要内容。

文献[3]采用555 定时器、D 触发器、逻辑门、变换电路产生m 序列,不需复杂的编程和程序下载,但硬件电路较为复杂。文献[4]介绍了2 种m 序列的实现算法,并且都能产生性能良好的m 序列,但是其中一种实现起来过程比较繁琐,另一种必须利用配套的编程软件和芯片,限制比较多,不利于推广使用。文献[5]对m 序列进行了详细的软件仿真介绍,但是缺乏硬件方面的研究。文献[6]所设计的高速伪随机序列发生器结构简单、成本低,能够生成m 序列、伯努利序列等多种选择,但是无法生成任意频率的序列。文献[7]采用C 语言编程来产生m 序列,这种算法实现速度相对来说较慢,并且会浪费很多时钟周期。

本文利用FPGA(现场可编门阵列)生成m 序列,并利用生成的m 序列经过IGBT 驱动,与光耦隔离电路、电源电路等组成扩频编码探地发射仪。将m 序列生成、Modelsim 仿真和具体应用结合起来,可加强学生对线性移位寄存器、FPGA 数字逻辑电路设计的充分理解,培养学生运用综合知识的能力。

1 m 序列发生器产生原理

反馈移位寄存器,特别是线性反馈移位寄存器,是实现伪随机序列的基本器件。当反馈函数为线性函数时,相应的反馈移位寄存器被称为线性反馈移位寄存器[8]。n 阶线性带反馈移位寄存器组成图如图1 所示。

图1 n 阶线性带反馈移位寄存器组成图

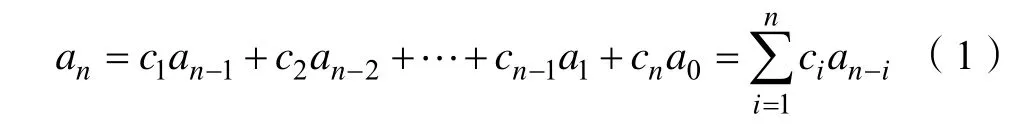

图1 中ci表示反馈线的2 种可能连接方式,ci=1表示连线接通,第n-i 级输出加入反馈中;ci=0 表示连线断开,第n-i 级输出未参加反馈。因此,一般形式的线性反馈逻辑表达式为

将等式左边的an移至右边,并将 an(c0= 1)代入上式,则上式可以写成:

其中x 的幂次表示元素的相应位置。该式为线性反馈移位寄存器的特征多项式,特征多项式与输出序列的周期有密切关系。当F(x)满足下列3 个条件时,就一定能产生m 序列:

(1)F(x)是不可约的,即不能再分解多项式;

(2)F(x)可整除xp+1 ,p 为周期,p= 2n+1;

(3)F(x)除不尽xq+1 ,q < p。

满足上述条件的多项式称为本原多项式,这样产生m 序列的充要条件就变成了如何寻找本原多项式。表1 中列出了部分m 序列的反馈系数。

根据表1 中的八进制反馈系数,可以确定m 序列发生器的结构。以7 级m 序列反馈系数Ci=(211)8为例,首先将八进制的系数转化为二进制的系数即Ci=(10001001)2,由此可以得到各级反馈系数分别为:C0=1,C1=0,C2=0,C3=0,C4=1,C5=0,C6=0,C7=1,由此就很容易地构造出相应的m 序列发生器[9]。根据反馈系数,其他级数的m序列的构造原理与上述方法相同。

表1 部分m 序列的反馈系数表

2 m 序列发生器的FPGA 设计

2.1 m 序列发生器的设计

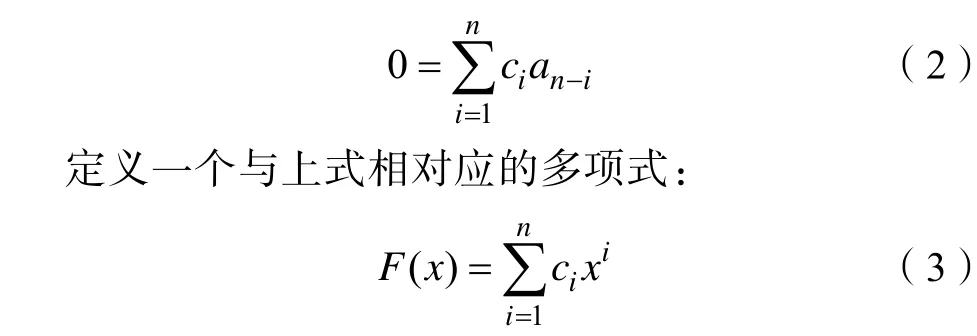

FPGA 作为一种可编程逻辑芯片,其结构和开发方式都跟传统的MCU 和DSP 有一定区别。MCU 和DSP 的设计主要是进行软件程序的设计,用户使用C语言完成各种算法和控制的实现,各种功能在CPU 的控制下按照顺序依次执行。而FPGA 的设计,实质是电路设计,是在一个可现场编程的通用逻辑器件里去搭建各种具有一定功能的逻辑电路[10],各个逻辑电路间是各自独立的,能够并行执行。同时,各个功能的电路之间又通过一定的控制和握手信号相互协调。本次设计中使用的是Intel Cyclone IV E FPGA 芯片,使用硬件描述语言 VHDL 和电子设计自动化工具Quartus II,设计和实现了上述方案中提出的m 序列发生器,即通过外设配置移位寄存器的初始值的方式来改变产生的m 序列[11]。所设计系统的主要硬件框图如图2 所示。

图2 m 序列发生器主要硬件框图

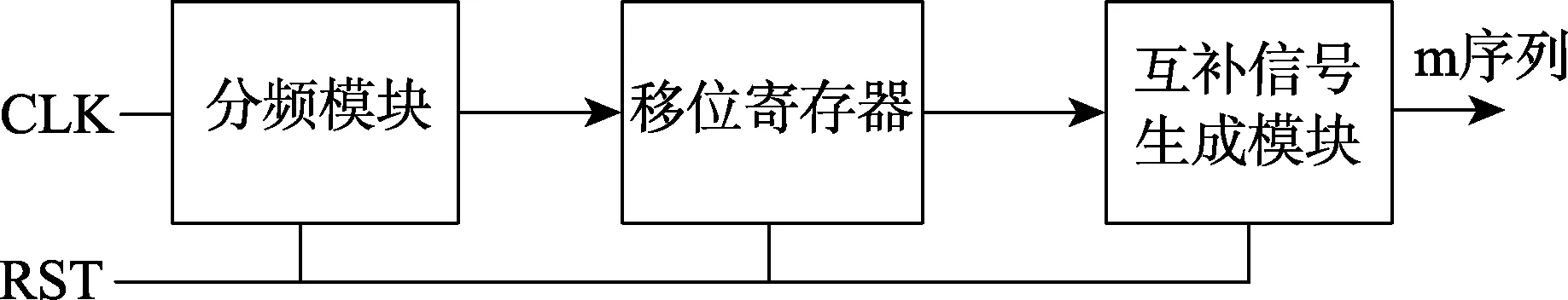

输入时钟频率需要进行分别设置。这里使用了计数器分频的模式,在一般情况下,偶分频属于普遍的分频用法,程序简单易懂,但是如果系统时钟固定,就不能得到任意想要的频率。因此引入了奇分频的分频方法,奇分频相较于偶分频,程序设计更为复杂,考虑的变量也相应增加。具体设计流程如图3 所示。

经过系统的软件分频后,会获得所需要的时钟频率,其频率值由计数值的大小来决定[12]。本设计采用了1 000 分频,经过分频后的时钟信号驱动线性移位寄存器。移位寄存器经过反馈后就会生成所需的m 序列。FPGA 中生成的移位寄存器结构图如图4 所示。根据需要调节反馈的位置,从而得到不同周期的m 序列。最后将生成的单路m 序列设置为互补信号生成模块的输入端,进而得到4 路互补信号。

图3 时钟调整模块工作流程图

图4 m 序列发生器结构图

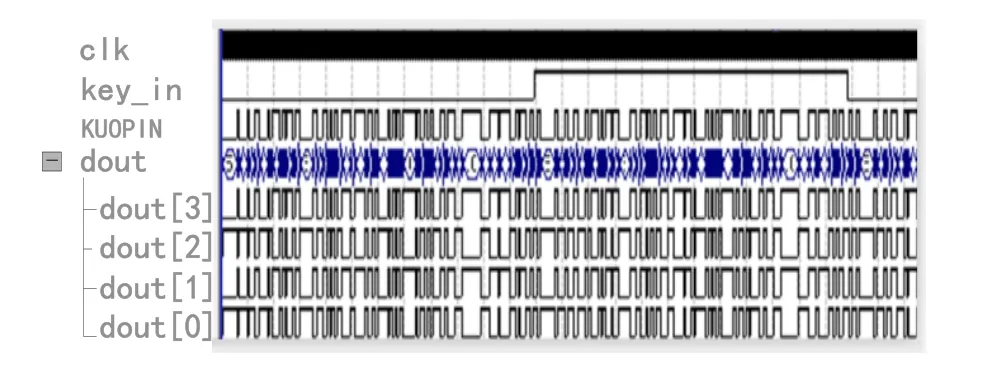

2.2 Modelsim 仿真

Mentor 公司的ModelSim 是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境以及完善的高性能的验证功能[13]。使用ModelSim 对上述设计中的m 序列发生器进行仿真结果如图5 所示。图5 中KUOPIN 信号为单路m 序列,dout 信号为4 路互补的m 序列。可以看出m 序列为一系列占空比不等的方波构成。

图5 m 序列仿真波形图

3 利用m 序列发生器实现探地发射仪

基于m 序列发生器设计了一套基于扩频编码的探底发射仪,结构原理如图6 所示。基本原理:利用FPGA 产生m 序列发生器,以此m 序列为基础,通过IGBT 逆变使m 序列增幅。增幅后的m 序列穿透能力大大增加,能够确保在大范围之内收到地质信息,减少野外环境带来的干扰,达到实际应用时的功率等级。在实际探测中,利用m 序列的相关特性还可以滤除掉大部分的由电力设施带来的干扰信号[14]。

图6 探地发射仪结构原理图

探底发射仪主要包括FPGA 信号发生电路、光耦隔离电路、IGBT 逆变桥和驱动电路、电源电路等。光耦隔离电路将高压信号与FPGA 信号进行光隔离以保护FPGA 芯片,防止芯片被信号电平转换期间产生的冲激损坏。IGBT 驱动电路则是直接驱动IGBT 逆变桥的驱动板,能够将输入信号转化为可靠的驱动电平,并且能够再次进行电隔离。电源电路以LM5118 为基础的开关电源,使得供电系统能够在野外环境中更可靠工作。

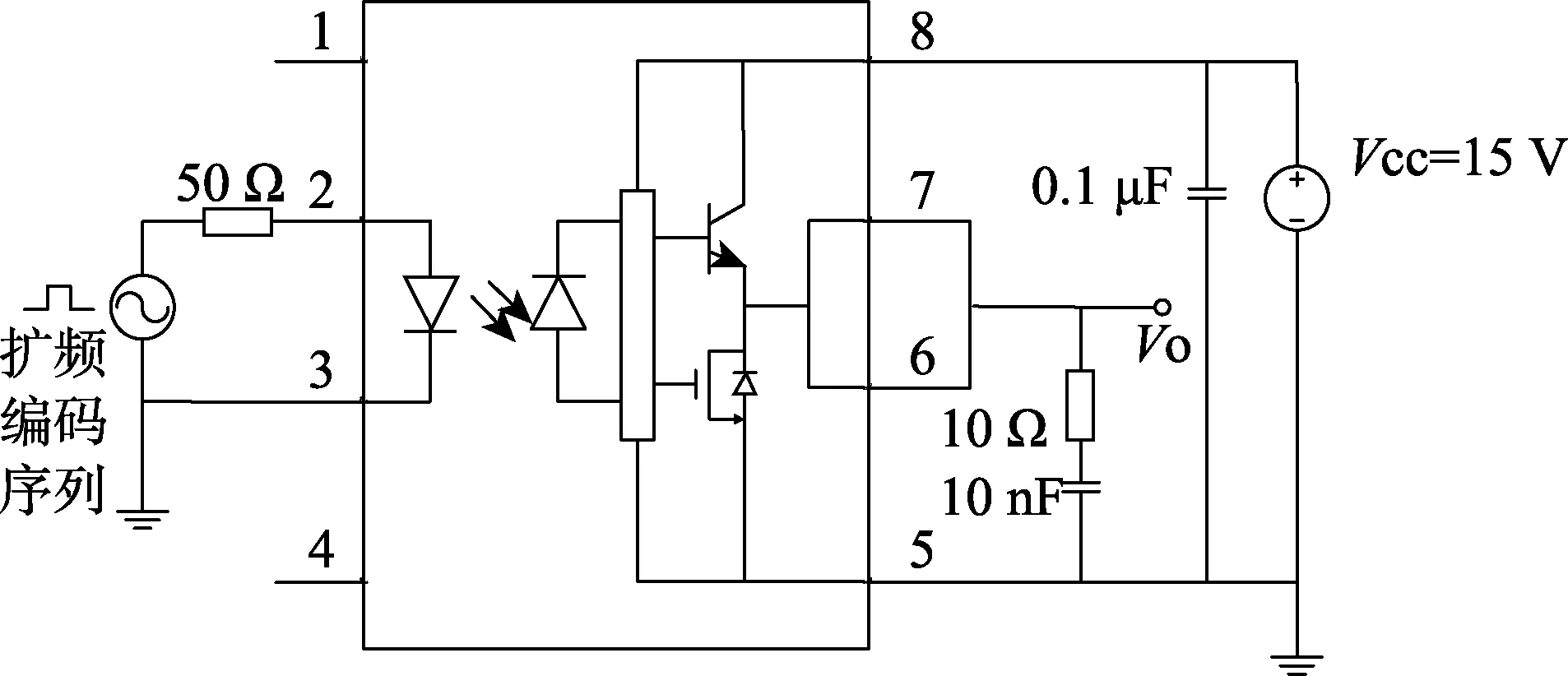

3.1 光耦隔离电路设计

由于FPGA 输出的信号幅值为3.3 V,而且如果和驱动板直接相连可能会导致FPGA 在IGBT 转换期间被冲激电流击穿烧毁,所以引入了光耦隔离电路对低幅值信号与IGBT 驱动板输入信号进行光隔离,其电路原理如图7 所示。

图7 光耦隔离驱动电路原理图

在图7 中,引脚“4”与“1”为空置引脚,“2”引脚为信号输入端,“3”引脚为信号地端。“8”与“5”引脚为输出的供电端,引脚“6”“7”短接后,作为信号输出端。可以看出输入与输出没有共地,这样也减少了输出端对输入端的直接影响,非常有利于对FPGA 核心芯片的保护。

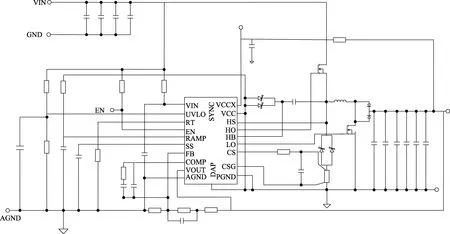

3.2 IGBT 驱动电路与电源模块设计

IGBT 驱动电路是驱动IGBT 的直接单元,它的电气参数直接影响着输入模块的安全性和输出信号的正确性[15]。本文采用了技术较为成熟的4 路隔离式驱动板,其原理框图如图8 所示。

图8 中为n 单元驱动板,每路最高输出6 A 电流,可驱动300 A/1 700 V 以下的IGBT,其中n=2,4,6,7。该驱动板的每一路都有相应的保护电路,保护报警电路与其他部分进行了电隔离。其中每2 个单元自带一个独立的DC/DC 辅助电源,使得单元隔离度更强。IGBT 驱动板的输入信号可以支持多种电平幅值,且各路输出的使能控制端具有统一性。该驱动板的电源端采用了极性保护措施。

图8 隔离式驱动板原理框图

开关电源电路以电源芯片LM5118 为基础,并结合相应的外围电路开发而成,外围电路如图9 所示。LM5118 高压开关稳压器具有使用最少外部元件实现高效降压或降压-升压稳压器所需的所有功能。

图9 LM5118 外围电路图

基于m 序列发生器设计的基于扩频编码的探底发射仪,包含了利用FPGA 产出m 序列电路、光耦隔离电路、IGBT 驱动电路等部分,具有一定的代表性。

4 结语

将m 序列计算、FPGA 生成移位寄存器、Modsim仿真,以及m 序列在探地发射仪的应用结合在一起,该实验可作为数字逻辑电路、EDA、模拟电路、电力电子等相关课程的综合实验案例。在数字逻辑电路和EDA 的课上使用该实验,既可让学生更加深入了解m序列的构成原理以及构成方法,又能使学生们掌握线性移位寄存器与m 序列生成之间的关系,以及m 序列在实际工程中的应用,使得学生对数字电路设计与仿真有一个较为全面的了解。该案例中包含了IGBT驱动电路、隔离电路、电源电路等内容,也可用在模拟电子技术、电力电子技术等课程的实验设计中。

该综合实验不仅提高了学生的学习兴趣,还培养了学生的综合知识运用能力。m 序列与实际工程的结合使学生对科研有更好的理解,引导其成为创新性人才。