基于FPGA的OOK可见光通信系统仿真与实现

2020-09-21王许浦孙晓红薛琦

王许浦 孙晓红 薛琦

摘 要: 根据OOK(开关键控)的原理,基于FPGA开发板用Verilog HDL语言实现OOK调制、解调和同步模块,并通过逻辑分析仪进行仿真。配合驱动电路、光电探测电路和放大电路等实现了整套可见光通信系统的设计,最后通过搭建实验平台进行测试,测试结果表明,收发电路通信距离达到12 cm,系统传输速率达到3.125 Mb/s。

关键词: 可见光通信; FPGA; OOK; 驱动电路; 光电探测器; 位同步

中图分类号: TN929.1?34 文献标识码: A 文章编号: 1004?373X(2020)17?0025?04

Abstract: According to the principle of OOK (on?off keying), the modules of modulation, demodulation and synchronization are realized by using Verilog HDL language and FPGA board, and simulated by logic analyzer. The whole set of visible light communication system is designed with driving circuit, photoelectric detection circuit and amplification circuit. The experiment platform was built to test the system. The test result shows that the communication distance of the transceiving circuit can reach 12 cm, and the transmission rate can reach 3.125 Mb/s.

Keywords: visible light communication; FPGA; OOK; drive circuit; photo detector; bit synchronization

0 引 言

可见光通信技术可以解决传统无线通信存在频谱资源紧缺、信息不安全以及电磁干扰等问题,同时,它在高速通信的同时又具备节能照明的特点而被广泛关注和研究[1?3]。目前研究可见光通信的很多,但是基于FPGA的可见光通信系统研究还并不多,由于FPGA具备运行速度快、管脚多和设计灵活等优点,因此,将可见光通信技术与FPGA相结合可以大大提高系统的性能[4?5]。本文基于FPGA开发板,运用Verilog HDL语言并结合电路设计搭建起一套可见光通信系统并进行验证。

1 可见光通信系统整体设计

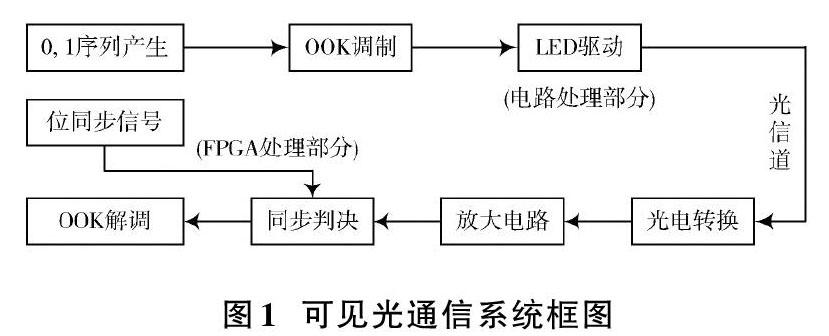

本系统发射端采用Alter公司Cyclone系列芯片,型号为EP4CE15F23C8的FPGA开发板对信号进行数字处理及时序控制,接收端采用Alter公司Cyclone系列芯片,型号为EP4CE30F23C8的FPGA开发板对接收的信号进行处理。重点在于OOK(On?Off Keying)的调制解调、同步等算法与Verilog HDL语言实现,以及发送电路设计和接收电路中互阻放大电路、同相积分器等电路的设计。其中,系统发射端的信号为FPGA产生的0,1周期符号序列,通过OOK调制到白光LED驱动电路中;系统接收端包括光电转换模块、放大电路模块和FPGA解调模块等,如图1所示。

2 基于OOK的可见光通信系统发射端的设计

2.1 基于Verilog的OOK调制

OOK是二进制振幅键控(2ASK)的一个特例。振幅键控是利用载波的幅度变化来传递数字信息,其频率和初始相位保持不变。载波可以是正弦波,也可以是方波,本文传输码元用的是方波。对于2ASK,当发送码元1时,载波振幅取[A1];当发送码元为0时,码元振幅取[A2]。根据载波的幅值区分碼元信息,可表示为:

OOK调制即将2ASK中一个振幅取0,另一个非0。OOK调制后波形示意图如图2所示。

基于上述原理,OOK调制本质上为载波信号与输入信源相乘。因此在设计的过程中,需要解决以下问题:信源如何产生,载波如何产生,合适参数的设置。

调制信号是通过FPGA内部自带的时钟信号的上升沿进行触发来产生的,所用的FPGA开发板内部的时钟频率为50 MHz,程序中定义了一个寄存器将调制信号的频率降低到光电转换器识别范围内。程序中设置00100111为一个周期信号。

载波信号是方波,用“0”和“1”的高低电平来表示,所以它直接和调制信号相乘得到已调信号。它是由AX515开发板50 MHz的时钟频率16分频得到,也就是方波的一个周期需要16个时钟信号的触发,即方波频率为3.125 MHz。

2.2 驱动电路的设计

根据发光二极管的放电特性,LED上升沿不是垂直的,而是有一个慢慢上升的过程,所以传输方波信号的速率受到一定限制。实验过程中通过电路修改尝试补偿存在的问题,结果表明需要选择合适的电容值对LED限流,才能使发光二极管发射出比较完美的方波信号。电路图如图3所示。

图3是发送电路,主要由电容和SI2300MOS型三极管构成,选用此三极管放大功率驱动LED发光,虽然有较大的功耗,但是抗干扰能力强,同时电路简单。

3 OOK可见光通信系统接收端的设计

3.1 接收电路设计

图4是接收电路硬件电路图,主要由光电探测器、运放OPA847构成的互阻放大器、运放OPA335构成的同相积分器、芯片TLV3501构成的判决电路等模块构成。

图4中,[R1],[C1],Z1用于提供一个2.7 V稳定的参考地电压;运放芯片U1,[R2]构成互阻放大器,U1采用OPA847,反馈电阻的取值决定了模拟部分的增益,[R2]采用0402封装,以尽可能减小寄生电容。依靠此电阻存在的寄生电容可以抑制振荡,同时,较小的寄生电容有利于提升系统高频特性。运放U2,[R3],[R4],[R5],[R6],[C2]構成同相积分器。对于一般的互阻放大电路往往难以兼顾高灵敏度和宽动态范围:若电路的增益高、灵敏度高,则放大电路在强光下容易饱和;反之,若要求能够在强背景光下检测信号,则电路增益必须减小。本电路增加了此积分器设计兼顾了高增益和高抗饱和能力,使得系统也能够在室外环境下正常工作。同时,此积分器也使得整个电路具有高通特性,常见的50 Hz工频干扰光(如日光灯光)能够得到比较有效的抑制。VR1,VR2,VR3是稳压器,保证电路电压稳定,U3构成判决电路,通过TLV3501能有效进行高低电平的判决,为解调作准备。

3.2 基于Verilog的OOK解调

光电探测器把光信号转换成电流的形式传输,经过互阻放大器后转变为电压的形式,然后经过判决等模块后将得到的信号送入型号为AX530的FPGA开发板中,利用数字锁相环实现位同步,得到每一位信号的判决时刻,把位同步信号作为解调用的工作时钟解调出原信息。本文的解调原理框图如图5所示。

本文采用数字锁相环实现采样频率的同步。解调的思想是根据OOK调制信号的特点,即在高电平调制的地方有载波,而低电平调制的地方没有载波。所以通过载波同步信号采样恢复出调制信号,但是采样时刻要和数据位同步,在这里通过数字锁相环实现与载波信号锁相后,再利用锁相后信号的下降沿采样已调信号来实现OOK的解调,数字锁相环Netlist视图如图6所示。

为了提高解调采样数据的准确性,图6是解调时设计的锁相环Netlist视图,这里用数字锁相环对载波相位锁定后,其下降沿是数据比特(modata)的中心采样来减小解调的误码率。数字锁相环由异或门鉴相器(XOR_pd:u1)、加减脉冲计数器(Kcounter:u2)、脉冲增减模块(idcounter:u3)、控制器(利用clk对fin脉冲的测量并给出[N]值模块counter_[N]:u4)、分频器([N]分频模块div_[N]:u5)等5个模块组成。输入信号与分频信号通过鉴相器模块后,鉴相器根据输出信号相位是否超前(滞后)于输入信号,从而产生加减脉冲计数器的计数方向用来控制信号,加减脉冲计数器根据计数方向控制信号来调整计数值。当控制信号为高电平时进行减计数,当计数值到达0时,就可以输出借位脉冲信号;反之,当控制信号为低电平时进行加计数,当计数值达到预设的[K]模值时,此时输出进位脉冲信号,脉冲增减电路则根据借位脉冲和进位脉冲信号在输出电路信号中进行脉冲的增加和减少操作,调整输出信号的频率持续进行上面的过程进行调整,则分频器最终输出信号与输入信号频率一样,即作为解调使用的位同步信号。

4 调制解调仿真分析

编写一个顶层文件例化调制、解调模块后生成的RTL视图,如图7所示。图7中,two_ASK:U_mo为生成的调制模块,ASK_two:U_demo为生成的解调模块。

Quartus Ⅱ中的逻辑分析仪观察到的调制解调的整个过程如图8所示。其中,sig_S为基带信号,carriers为载波(频率为3.125 MHz),modata为调制信号,pll_carriers为采样频率(和载波同步),demodata为解调信号。从图8中可以看出,基带信号00100111为一个符号周期,解调出来的依然是00100111,解调结果正确。

5 实验测试及分析

本节主要对搭建的基于OOK的可见光通信系统进行测试,包括发送电路、接收电路和调制解调过程的测试以及收发电路通信距离、通信速率的测试,目的是在通信距离范围内测试搭建系统的最大传输速率。

图9a)为搭建起来的可见光通信系统实验平台,包括发射端、接收端、信号发生器以及示波器,值得说明的是,程序主要用USB?Blaster由FPGA开发板的JTAG口烧录开发板。图9b)主要是系统模块介绍,发射端包括发送板与驱动电路,接收端包括接收板与接收电路。

5.1 收发端电路测试

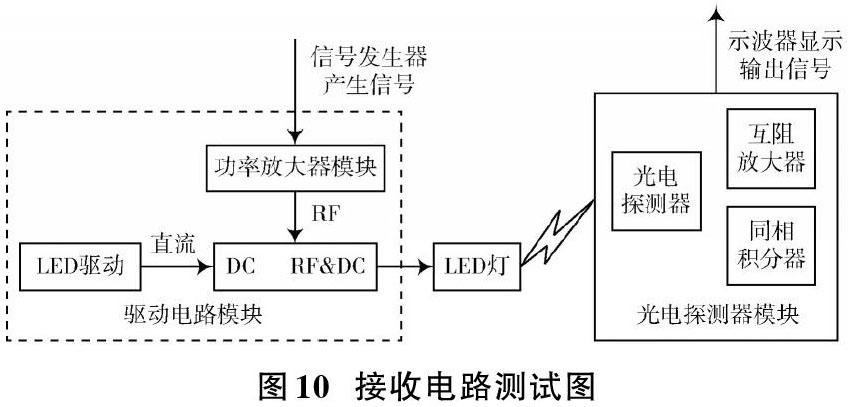

如图10所示,此次接收电路的测试主要由信号发生器和示波器完成,驱动电路上的LED灯由直流偏置电流和信号发生器产生的信号加载到LED灯上共同驱动发光,经过接收电路中光电探测器探测到的信息并且经过放大等处理后输出在示波器上显示。

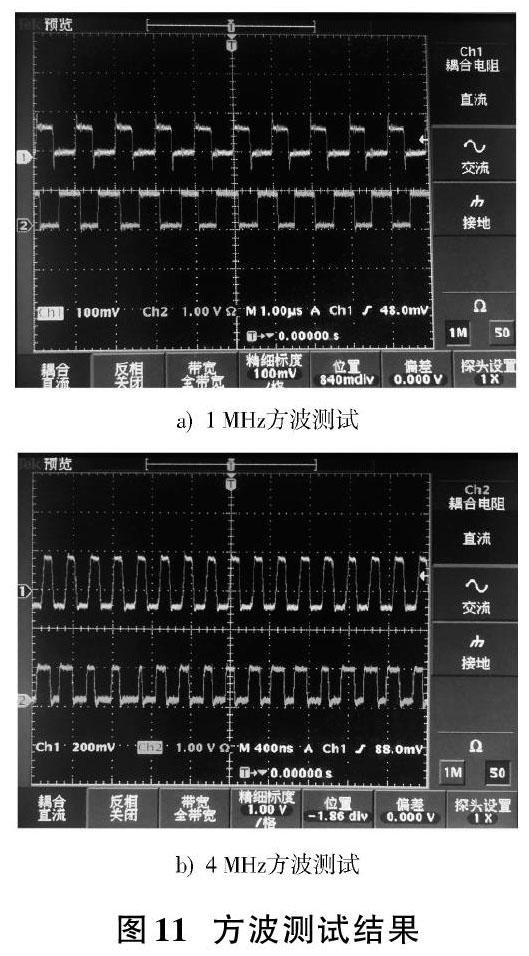

图11是根据图10方式测试的结果,图11a)是信号发生器产生的频率1 MHz未经过发送、接收电路板处理和经过发送、接收电路板处理的信号,其中,上方的黄线是发送端信号,电压为60 mV,下方的蓝线是接收端信号,经过电路处理放大后电压为1 V。图11b)是信号发生器产生的频率4 MHz未经过发送、接收电路板处理和经过发送、接收电路板处理后的信号,其中,上方的黄线是发送端信号,电压为280 mV,下方的蓝线是接收端信号经过电路处理放大后的信号,电压为1 V,经过测试表明,接收电路板可以达到系统需求。

图12是根据图10方式测试的结果,用信号发生器产生频率4 MHz的方波信号来测试收发电路通信距离。图12a)~图12d)是通信距离分别为5 cm,12 cm,15 cm,22 cm时信号发生器产生的信号波形和经过收发电路处理后接收到的信号波形。其中,上方的黄线是信号发生器产生的信号波形,下方的紫线是经过收发电路处理后接收到的信号波形,可以看出,收发端电路的距离在12 cm范围内能很好地实现信号的接收,超过12 cm接收端接收到的信号波形会出现错误信息,发生误码,当收发端电路的距离为22 cm时,接收到的信号波形发生变化,显然不是要接收的信息。

5.2 系统测试

通过前面收发电路通信速率和通信距离的测试,本次主要在最佳通信距离12 cm范围内进行测试。图13中,上方的黄色线为FPGA产生的载波为3.125 MHz的OOK已调信号,电压值为220 mV,经过发送板电路的处理后驱动LED发光,下方的紫色线是光电探测器将探测到的光信号转变成电流信号,经过互阻放大器、同相积分器处理和TLV3501判决输出的信号作为接收端FPGA开发板要解调的信号,电压值为3.3 V。其中,每8个数据符号(00100111)为一个周期,可以看出只有输入信号“1”时载波才会与OOK理论仿真图8一致,能够实现很好地发射和接收,此系统验证成功。

6 结 语

本文主要通过FPGA设计了一个OOK的可见光通信系统进行实验验证。首先运用Verilog HDL语言进行调制解调以及同步模块的编写,并借助软件Quartus Ⅱ中的逻辑分析仪连接FPGA开发板进行仿真验证,然后对收发电路的传输速率和通信距离进行测试,系统测试结果表明,传输速率达到3.125 Mb/s,收发电路在12 cm范围内能很好地完成信号接收。

注:本文通讯作者为孙晓红。

参考文献

[1] 王永进,王金元,朱秉诚.可見光通信最新研究进展[J].邮电设计技术,2017(8):1?6.

[2] 迟楠.让Li?Fi点亮你的网络[J].中国经济报告,2016(1):116?118.

[3] 邬江兴.可见光通信在中国[J].中国科技产业,2014(10):32?34.

[4] 梁景熙,刘宏展.2ASK可见光通信系统的硬件设计与实现[J].现代电子技术,2015,38(21):56?59.

[5] 梁景熙,张剑鸣,刘宏展.基于FPGA的PPM可见光通信系统的仿真与实现[J].光通信技术,2015,39(9):57?59.

[6] 李茹,张涛,朱秋煜,等.基于FPGA的OOK可见光通信系统设计与实现[J].工业控制计算机,2016,29(12):106?107.

[7] 武梦龙,郭佳,刘文楷,等.LED作为收发元件的双向可见光通信系统方案及实现[J].光学学报,2018,38(4):62?68.

[8] 杨宇,刘博,张建昆,等.一种基于大功率LED照明灯的可见光通信系统[J].光电子激光,2011,22(6):803?807.

[9] 毕成军,陈利学,孙茂一.基于FPGA的位同步信号提取[J].现代电子技术,2006,29(20):121?123.

[10] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.