简易数字电子时钟的设计

2020-08-26高伟元李盼亮

高伟元,杨 栋,李盼亮,高 晗,丁 鹏

(甘肃农业大学机电工程学院,甘肃 兰州 730070)

随着科技水平的不断发展进步,数字集成电路的应用范围也越来越广阔,生活中有许多应用数字集成电路的东西,比如生活中常见的数字电子时钟。数字电子时钟具有的基本功能为能准确计时,显示时、分、秒、可实现自动校正、具有整点报时以及复位功能,数字电子时钟的设计可以使我们更好的掌握课本内的理论知识,以理论结合实际,应用知识解决日常生活的问题,以及体验科技给我们生活带来的便利。

1 设计思路

数字电子时钟的核心就是秒脉冲发生器和进制电路,通过秒脉冲发生器产生的秒脉冲给秒计数电路计数脉冲,然后在通过进制电路给分、时计数电路计数脉冲,进而达到秒计数电路每60s向分计数电路进一位,然后自动清零;分计数电路每60min向时计数电路进一位,然后自动清零;时计数电路每24h自动清零的目的。由于需要校准时间和芯片的锁存功能,需要为电路的分和时计数电路设计复位功能和校正功能。具体数字电子时钟框图如图1所示。

图1 电子时钟框图

2 模块电路的设计

2.1 秒脉冲电路模块

1Hz的计数脉冲是通过32768Hz的石英晶振经过14分频和2分频所得,具体电路如图2所示。

图2 秒脉冲电路

2.2 秒计数和分计数电路模块

秒计数电路模块采用反馈清零法,即利用74LS160芯片的异步清零端,当秒计数电路到达60(01100000B)时,用秒计数电路十位输出端的Q1,Q2的高电平加与非门对两片芯片的步清零端加低电平进行清零。具体电路如图3所示。

图3 秒计数电路模块

分计数电路模块和秒计数电路模块功能类似,接法也类似,均采用反馈清零法。

2.3 时计数电路模块

时计数电路模块也采用反馈清零法,即利用74LS160芯片的异步清零端,当时计数电路到达24(00010100B)时,用时计数电路十位输出端的Q1和个位的输出端Q2的高电平加与非门对两片芯片的步清零端加低电平进行清零。具体电路如图4所示。

图4 时计数电路模块

2.4 总体电路设计

通过秒脉冲发生器产生的秒脉冲给秒计数电路时钟脉冲,秒计数电路在60s的时候给分计数电路一个脉冲的上升沿,让分计数电路每60s自动加1,进而给分计数电路每60s一个上升沿的时钟脉冲,然后在通过分计数电路在60min的时候给时计数电路一个脉冲的上升沿,让时计数电路每60min自动加1,进而给时计数电路每60min一个上升沿的时钟脉冲。对于复位和校正功能,可以利用74LS160芯片的清零端对分进制电路和时进制电路进行复位,利用秒脉冲给分计数电路和时计数电路进行自动校正。

当数字电子时钟的分计数和秒计数电路到59(01011001B)分 59(01011001B)秒时,蜂鸣器响起,进行一秒钟的整点报时操作,即需要两个四输入与门和两输入与门,当分计数、秒计数电路的十位的Q2、Q0和个位的Q3、Q0同时为高电平时,给蜂鸣器一个高电平,蜂鸣器响起。具体电路如图5所示。

图5 总体电路图

3 电路仿真

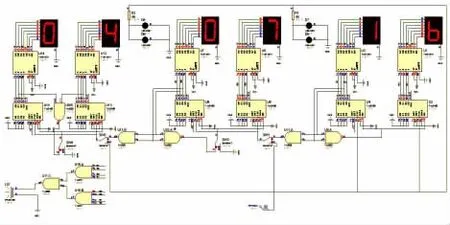

在用Proteus电路仿真过程中要注意,由于模拟晶振会占用大量的CPU运算空间,会导致电脑卡顿和仿真的结果不准确,所以在实际仿真的过程中可以将振荡电路部分取掉,双击4060芯片,直接给4060芯片设置输入脉冲为32768Hz,或者直接给秒脉冲输入端给软件的秒脉冲。仿真电路如图6所示。

图6 仿真电路图

4 误差与分析

1)石英晶振产生的脉冲在经过4060芯片的14分频之后会出现波形的严重失真,会对秒脉冲有较大影响,导致计数出现误差。经过波形的测试,发现10分频之后,波形会逐渐出现失真,分频越高失真越大,所以可以先采用4060芯片对脉冲进行10分频,然后在对脉冲进行6分频,以此来改善秒脉冲的波形。

2)在实物仿真中,会发现校时的时候,打开或者关闭单刀双掷开关,会导致计数数字出现随意跳动的问题,这是因为开关的抖动,导致校时不准确,因此可以加入施密特触发器来防止开关抖动造成的校时不准确的问题。