基于UVM实现SM4算法的自动化验证平台

2020-08-22马盼,靳旭

马 盼,靳 旭

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

1 概述

随着国内高速铁路的快速发展,越来越多的前沿技术被应用于轨道交通安全通信系统中。由于硬件集成度高、可并行处理数据等特点,为提升铁路信号平台系统性能和降低软件复杂度,CPLD/FPGA(可编程逻辑器件)和定制芯片等硬件产品得到广泛应用。针对这些硬件产品,逻辑功能仿真验证是保证产品正确性和安全性的重要环节,其目的就是验证硬件产品是否满足设计需求[1]。目前铁路相关CPLD/FPGA逻辑仿真采用传统定向测试序列进行功能验证[2],这种方法针对不同序列搭建不同的测试环境,导致平台搭建时间长,平台移植复用性差,验证效率不高。

验证方法学的发展有效地提高了验证效率,通用验证方法学(Universal Verification Methodology,UVM)面向所有数字设计,涵盖从模块级到芯片级,从专用集成电路(Application Specific Integrated Circuit,ASIC)到CPLD/FPGA,从控制逻辑、数据通路到处理器的全部场景[3]。验证语言SystemVerilog的面向对象和随机约束等核心特性配合UVM提供的基础类库和基本验证结构可以快速实现验证环境的自动化。本文提出了以SM4加解密算法模块为验证对象,采用SystemVerilog语言构建基于UVM的自动化验证平台。

2 待测设计SM4硬件分析

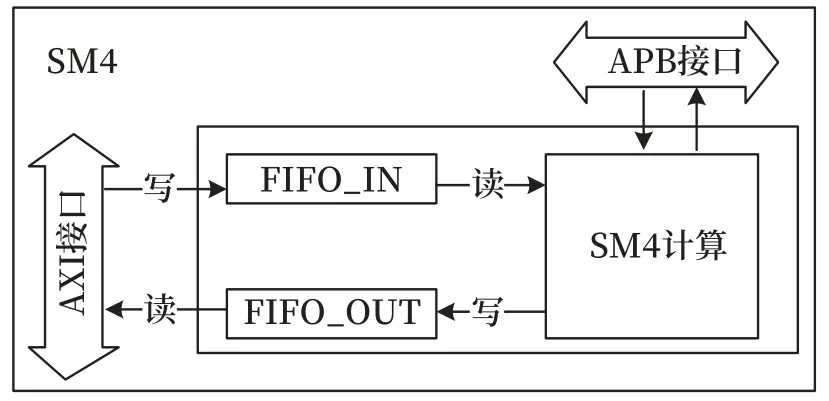

SM4硬件设计结构如图1所示,该硬件模块内部包含两个缓存先入先出队列(First Input First Output,FIFO),来暂存部分传输数据,一个SM4计算模块,其功能是解析传输数据,并计算SM4加解密结果。该算法遵循中华人民共和国国家标准《信息安全技术 SM4分组密码算法》(GB/T 32907-2016)进行轮密钥生成以及加密解密计算[4]。

图1 SM4硬件设计结构框图Fig.1 SM4 hardware design structure diagram

SM4硬件模块通信接口符合外围总线(Advanced Peripheral Bus,APB)和可扩展接口(Advanced Extensible Interface,AXI)总线协议,其中APB接口是片上总线协议(Advanced Microcontroller Bus Architecture,AMBA)中提出的一种低功耗和低复杂度的二级总线,在SM4硬件设计中传输配置模块内部寄存器信息。AXI是一种面向高性能、高带宽、低延迟的片内总线[5]。它的地址/控制和数据相位是分离的,支持不对齐的数据传输。在突发传输中,只需要首地址,同时分离的读写数据通道、支持未完成状态下的传输访问、乱序访问和更加容易达到时序收敛。在本文描述的验证对象中,AXI接口用于传输明文和密文数据。

3 UVM验证平台设计

UVM融合了VMM(Verification Methodology Manual)和OVM(Open Verification Methodology)验证方法学的特性,将验证过程中可重用和标准化的部分规定在其方法学的类库中[6],例如uvm_object、uvm_driver、uvm_env等,通过对这些核心类的继承和重载,使验证平台内的组件具有良好的封闭性并形成结构层次关系,这种具有复用性的验证环境可以有序完成不同的测试场景。一个UVM验证平台主要包括序列发生器、驱动器、监视器、代理容器、参考模型和计分板,这些组件集成在环境组件中,与待测设计通过定义的接口连在一起。

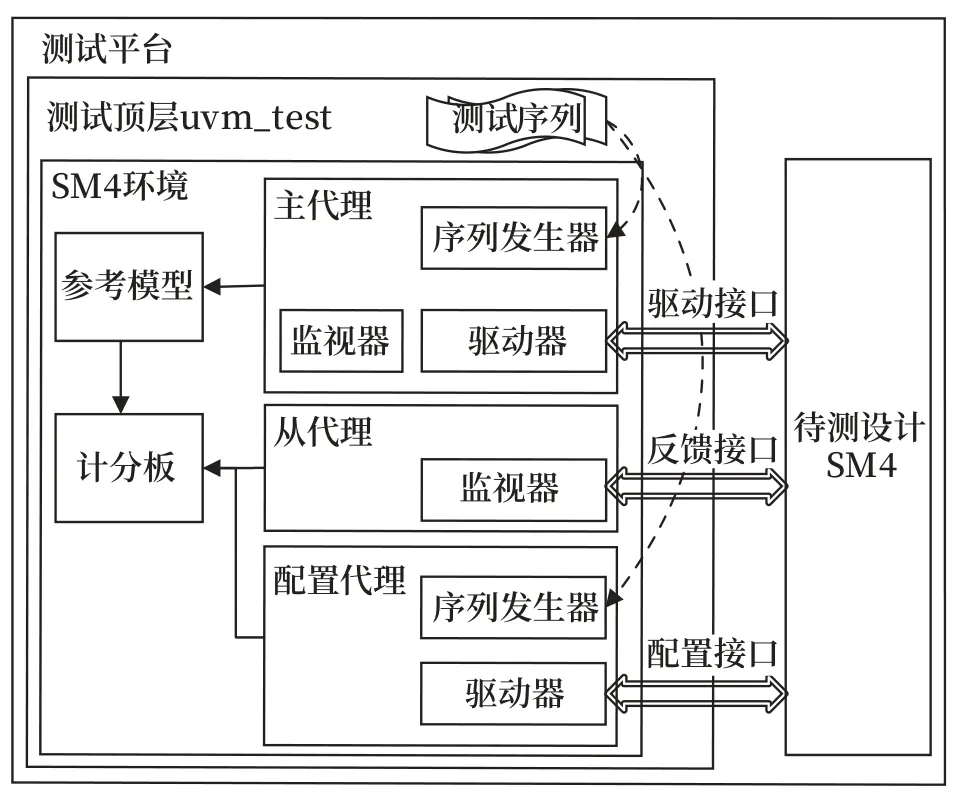

本文的验证平台根据SM4硬件结构的特性采用标准的UVM架构进行设计,其结构如图2所示。UVM验证平台组件之间通过事务级建模(Transaction Level Modeling,TLM)端口进行数据通信,从环境层次结构而言,测试顶层uvm_test用于建立整个验证环境,从环境的结构和连接关系到使用哪条测试序列都是由测试顶层决定[7]。

环境组件包含多个代理容器和其他组件,这些不同的组件共同构成完整的验证环境。通过测试顶层例化环境组件得到一个以uvm_test为树根的树状拓扑结构,这种树状环境结构具有可配置性,使得环境组件可以复用。

图2 验证平台结构Fig.2 verification platform structure

主代理容器封装了序列发生器、驱动器和监视器3个基本组件,其中序列发生器可以选择和调度由定序器产生的随机测试序列并传送给驱动器。驱动器从序列发生器中获取到事物数据后,根据端口协议经过模拟转化,在接口中对待测设计进行时序激励。监视器用于采样待测设计端口信号并转换成事务级数据返回给上层代理容器进行数据传输。在本设计中主代理容器负责向待测设计提供符合AXI接口协议的驱动信号,并将监视器采集到的驱动数据传递给参考模型。从代理中只有监视器一个组件,用于实时监视待测设计的计算输出,通过反馈接口采集结果数据。配置代理负责提供模拟寄存器的配置信号,该信号时序符合APB接口协议,用于配置测设计。

参考模型模拟待测设计的功能,在验证平台中参考模型与待测设计输入相同的数据,二者经过各自的计算后,将产生的数据传递到计分板中进行自动对比和报告。

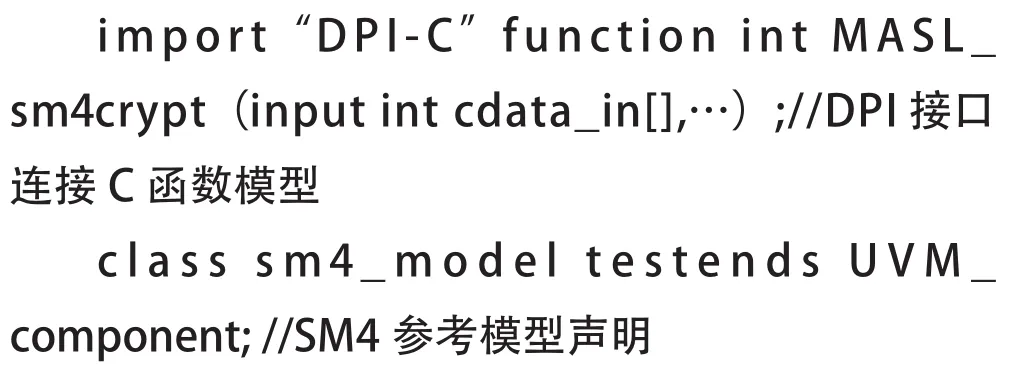

4 基于C的UVM参考模型

参考模型通常由验证人员使用硬件描述语言进行开发,对于运算方法复杂的设计,需要占用大量的时间进行概念理解、编写代码并调试,这无疑给验证开发带来了额外的负担。SystemVerilog语言提供的直接编程接口(Direct Programming Interface,DPI)可以连接C/C++高级语言,实现硬件与软件的跨边界通信[8]。

本文的待测设计为一个纯粹的算法模块,SM4算法具有标准的C语言函数模型,其功能为依据加密解密标志,对输入的明文进行SM4加密,得到密文,或者对输入的密文进行SM4解密,得到明文。为避免对算法C模型进行二次转换,本文提出的验证平台采用DPI接口将算法C模型嵌入UVM环境中进行联合仿真,具体方法如下。

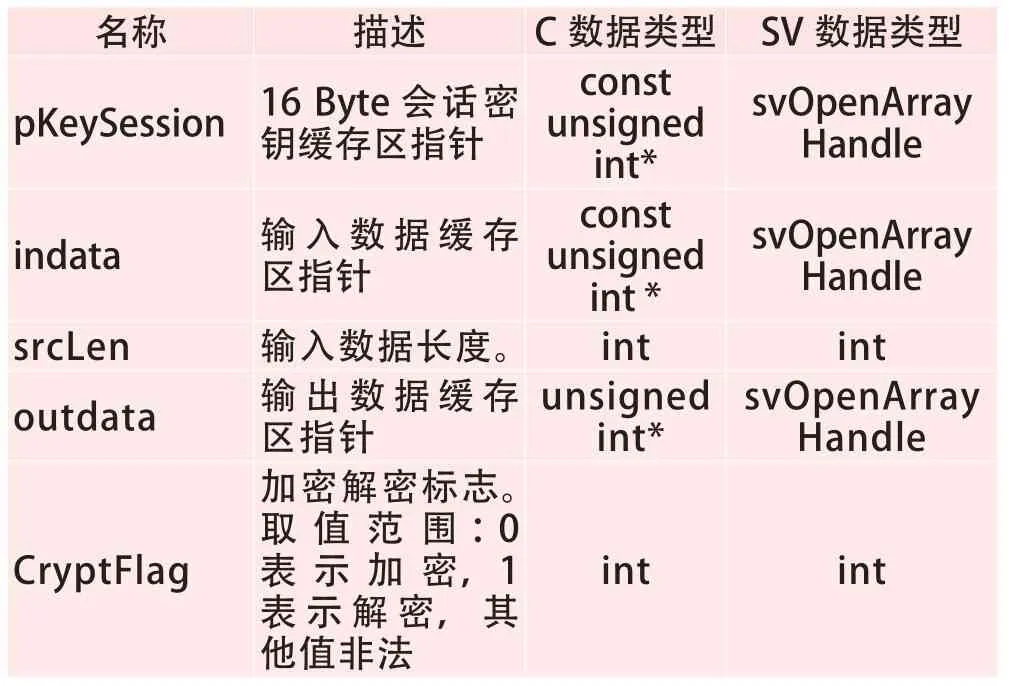

1)修改C函数接口,确定SystemVerilog和C语言程序输入输出之间的数据类型映射关系。在本设计中,其中C函数的端口定义如表1所示,修改前的C函数接口为:

int MASL_sm4crypt(const unsigned int*pKeySession,const unsigned int *indata,int srcLen,int CryptFlag, unsigned int*outdata); //C函数接口声明

对照表1映射标准,C函数结构修改成如下格式:

表1 C接口定义及与SV语言之间的数据类型映射Tab.1 Mapping of data type between C interface definition and SV language

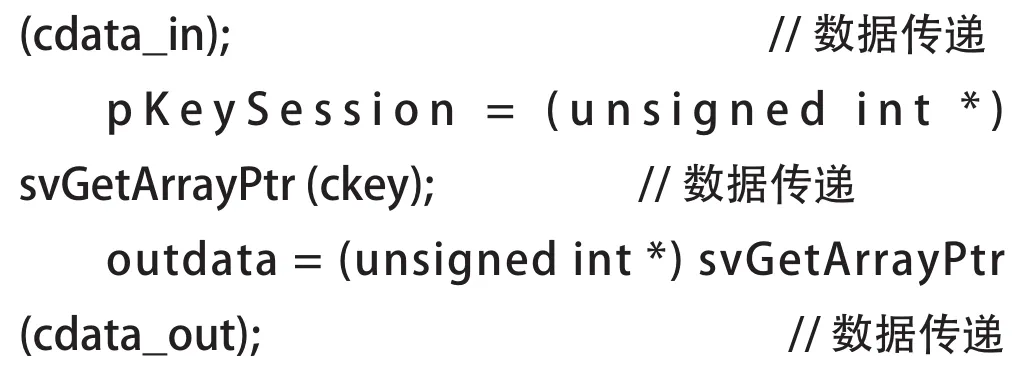

2)C程序内部声明指针,并将指针指向输入输出动态数组地址,进行数据传递。代码实现如下:

3)在C程序内导入数学库函数svdpi.h,库函数定义了SystemVerilog DPI结构和方法。

4) 在UVM参考模型中导入C函数模型。在导入C模型时,需要规定参数的方向:当数据是从System Verilog流向C函数时,参数方向规定为input,反而则为output,如果某个参数即从System Verilog流向C,同时又从C流向System Verilog,则需声明为inout型。

5)在UVM参考模型中调用C函数。在参考模型组件中,涉及UVM和C混仿的代码实现如下:

5 仿真运行结果

以测试序列rand_test(随机测试)为例分析验证结果。该测试序列由序列发生器产生不定长度的2 000包密文或者明文数据,再由驱动器产生APB配置信号和AXI读写操作信号进行单次激励,单次数据大小由随机化的长度信号决定,可实现16的整数倍字节传输,加密或解密计算方式选择由随机化加解密标志信号决定。

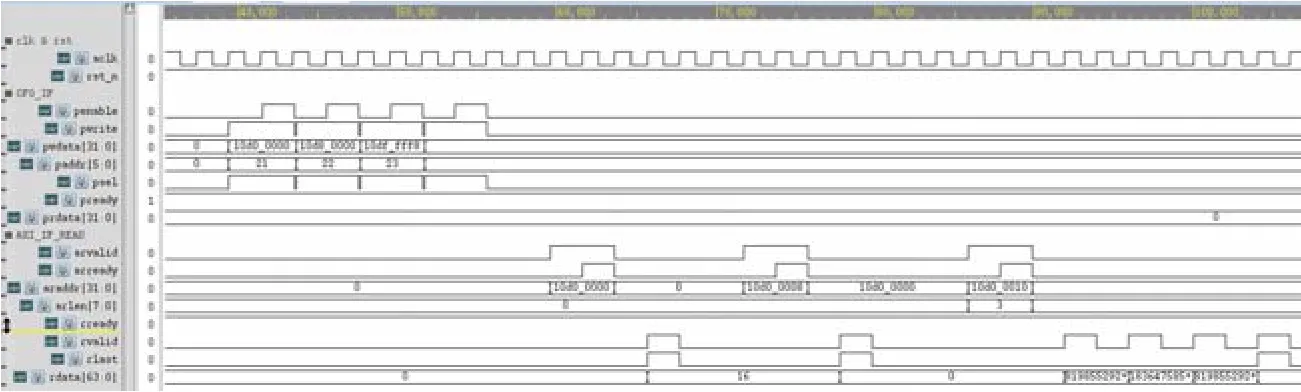

如图3所示为该测试序列单次数据包的AXI读数据仿真波形,根据APB端口配置的首地址,从地址0x10D0_0000开始,依次写入64位数据字节长度、64位加解密标志(0:加密,1:解密)、128位密钥和加解密数据。

图3 AXI读数据仿真波形Fig.3 Simulation waveform of AXI reading data

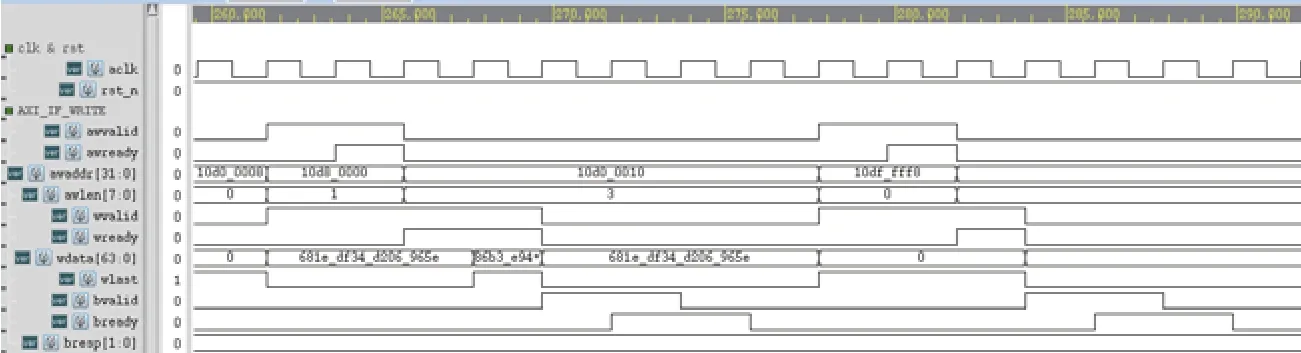

如图4所示为该测试序列单次数据包的AXI写数据仿真波形,加解密之后的数据写入地址由0x10D8_0000开始,全部计算完成并将计算结果成功写出后,计算结果标记地址0x10DFFFF8处标记为0,至此单次数据包激励完成,驱动器申请下一包数据进行驱动。

图4 AXI写数据仿真波形Fig.4 Simulation waveform of AXI writing data

测试序列的验证结果对比报告会实时在终端中打印出来并形成文件保存,如图5所示为仿真报告,打印信息表明测试序列经过2 000次成功对比,没有警告、一般错误或严重错误,该测试序列通过验证。经过随机测试,对未覆盖的地方采用定向测试,遍历FIFO空满边界,复位测试,并构造错误序列验证待测设计是否能及时检测并做出相应报警,经覆盖率统计分析得到代码行覆盖率为98%,决策覆盖率为95%,功能覆盖率达到100%,因为设计中存在一些实际运行中并不会出现的冗余情况,行覆盖率和决策覆盖率没有达到100%,与设计人员确认并排除此情况后,覆盖率符合指标。

图5 仿真报告Fig.5 Simulation report

6 结论

本文以SM4加解密算法模块为验证对象,采用随机测试向量并利用DPI接口内嵌C函数模型构建了基于UVM的自动化实时监控验证平台,实现UVM和C模型的联合仿真。从SM4参考模型的代码量来看,C函数的代码量为390行,嵌入C模型后的UVM参考模型代码量仅有100行,大大简化了验证平台复杂度,缩短验证周期。而随机测试序列和自动实时监控,区别于传统仿真,验证平台可以有序完成不同的测试场景,避免对验证平台的大量修改和单纯用人工检查,保证验证周期的完备性。该验证平台结构组件封闭独立具有复用性,可实现CPLD/FPGA和芯片硬件功能验证平台从模块级到系统级的移植。