基于CGH40010F的连续F类功率放大器仿真与设计

2020-08-14程晖

程晖

摘 要: 针对通信技术对通信基站射频前端指标要求日益增高的问题,为了设计更大带宽、更高效率的功率放大器,文中对连续F类功放的设计理论进行深入研究。基于CREE公司的CGH40010F高功率管完成了功放的设计、仿真、制作与调试。在仿真软件的选择上,文中使用的仿真环境为ADS;而在功放制作加工上,文中使用FR4射频板。测试结果表明,所设计的功放在1.7~2.7 GHz工作带宽内,可以实现大于39.5 dBm的输出功率和大于65%的效率。同时,为了解决功放的效率与线性度间的矛盾,对功放进行预失真实验。实验结果表明,在2.6 GHz的工作频点,功放在33 dBm输出时,ACPR可以从-34.5/-33.6 dBc 降低为-47.4/-48.3 dBc。

关键词: 功率放大器; 設计理论研究; CGH40010F; 通信基站; 连续功放; 放大器设计

Abstract: The development of communication technology results in a higher demand for the RF front?end index of communication base station. In order to design a power amplifier with larger bandwidth and higher efficiency, the design theory of class?F continuous power amplifier is studied in this paper. Design, simulation, manufacture and debugging of the power amplifier are completed on the basis of high power transistor CGH40010F made by Cree Company. In the selection of simulation software, the simulation environment used in this paper is ADS. In the production and processing of power amplifier, FR4 RF board is used. The testing results show that the designed power amplifier can achieve the output power of more than 39.5 dbm and the efficiency of more than 65% in the working bandwidth of 1.7~2.7 GHz. In order to solve the contradiction between the efficiency and linearity of the power amplifier, the predistortion experiment was carried out. The experimental results show that when the output of the power amplifier is 33 dBm at 2.6 GHz, the ACPR can be reduced from -34.5 / -33.6 dBc to -47.4 / -48.3 dBc.

Keywords: power amplifier; design theory research; CGH40010F; communication base station; continuous power amplification; amplifier design

0 引 言

通信系统的发展对通信基站中的各种射频器件有了更高的要求。作为通信基站中的主要耗能设备,功率放大器是射频前端的重要器件之一,其负责放大射频信号,保证射频信号有足够的功率发射[1?3]。功率放大器的发展有着以下几个明显趋势:

1) 效率不断提高。功放的效率决定通信基站的耗能,影响基站的通信规划,是功放最重要的指标之一[4?5]。

2) 带宽、功率不断提高。功放的输出功率提升,意味着更高的通信稳定性、更快的通信速率,同时可以依靠更少的通信基站覆盖相同的通信区域[6?7]。

基于以上分析,本文对功放的设计理论进行研究、分析。重点研究了连续类功放的设计理论,然后结合指标要求设计工作频段在1.7~2.7 GHz的宽频带功率放大器。功放使用CREE公司的CGH40010F高功率晶体管,实现频带内39.5 dBm以上的功率输出,其功放效率大于65%。同时,为了解决功放的效率与线性度间的矛盾,本文对功放进行预失真实验。经测试,功放在33 dBm输出时,ACPR可以达到-47.4 dBc/-48.3 dBc。

1 设计理论

1.1 逆F类功率放大器

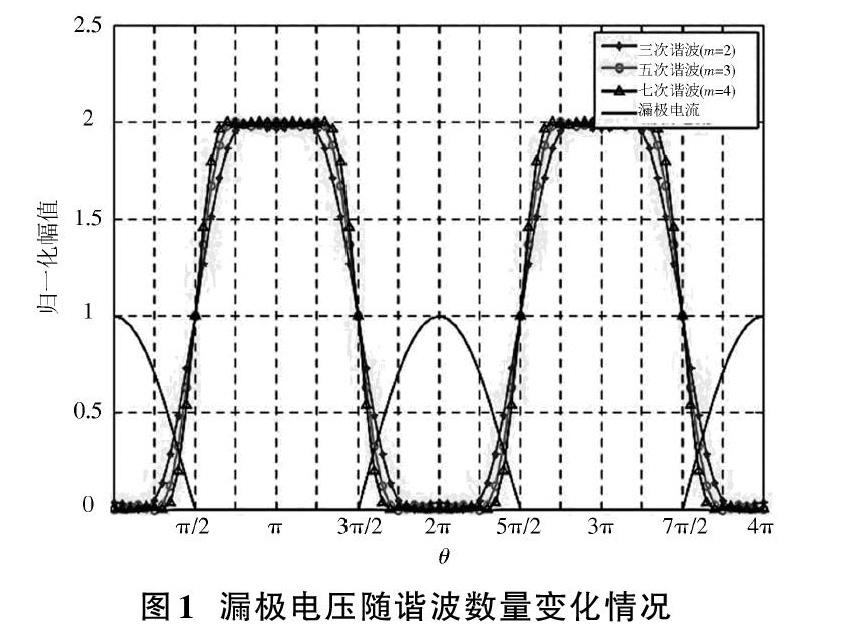

功率放大器是通信系统射频前端的重要器件之一,其负责将射频信号放大到指定的功率,然后由天线进行发射。功率放大器的性能关系到发射信号的质量,对于通信的完成起到极其重要的作用。常见的功率放大器种类有:A类、B类、C类、D类、E类和F类。由于通信技术的不断演进,对于功放的指标要求也愈加严苛。A类、B类、C类功放因其效率低下,已逐渐在通信系统中淘汰。F类功放具有较大的工作带宽与工作效率,同时在布板上有较小的体积和成本,因此得到了广泛的应用。F类功放在工作时,通过依靠不同的谐波阻抗,构建漏极电压、电流波形,从而实现更高的效率。在工作时,F类功放工作在半导通状态[8?10]。漏极电压随谐波数量变化情况如图1所示。

从图1可以看出,漏极电流根据谐波阻抗变换,控制晶体管在奇次谐波时开路、偶次谐波时短路,从而实现漏极电压波形近似为方波。此时,电压与电流的波形在时域上互补交叠,可以在理论上实现效率的100%。考虑有限次谐波,电压的波形可以写成:

根据式(2)可以在图1中得到不同谐波次数下的电压波形。可以看出,随着谐波次数的增加,电压波形越来越接近方波;电压波形的零点数与谐波次数m相等。零点的位置,可以由式(3)确定。

式中,r=1,2,…,m。当仅考虑3次谐波,即m=2时,根据式(3)可以得到两个零点分别为[-π6]和[π6]。此时,有: [V-π6=1-V1cos-π6-V3cos-π2=0Vπ6=1-V1cos-π6-V3cos(-π2)=0V-π6=0+V1sin-π6+3V3sin-π2=0Vπ6=0+V1sinπ6+3V3sinπ2=0] (4)

当考虑5次谐波,即m=3时,用同样的方法可以得出效率为94.8%。可看出,当F类功放的谐波次数增加,其效率会趋近于100%。

1.2 连续型F类功率放大器

F类功放理论上有着较高的效率,但无法实现较大的带宽[11?12]。在F类功放的基础上,重新定义电压波形如下:

式中,电压波形引入了4次谐波分量,但由于4次谐波项仅有正弦项,只会引入抗性负载,而不会消耗功率。因此,在该波形下的新功放和式(2)具有相同的输出功率与效率。

将3次谐波下的零点代入式(7),整理得到矩阵形式的方程组:

式中,[Ropt]是优化后的最优基波阻抗。对于连续类F功放,其奇次谐波开路、偶次谐波为纯阻抗。从式(11)可以看出,连续类F功放在保证效率的同时,拥有较高的带宽。

2 系统实现

2.1 功放指标

功放是射频系统内的主要耗能设备,将直流电转换为射频信号的功率。功放效率是衡量功放性能的重要指标之一,其定义如下[13?14]:

本文在设计功放时,除了功放的效率以外,还关注了以下线性度指标。

图3为功放输出功率与1 dB压缩点定义的示意图。由于晶体管的饱和特性,功放的输出功率并不是一直与输入功率成线性关系。从图中可以看出,当实际输出的功率与理想状态相差1 dB时,定义此时的输入功率为功放的1 dB压缩点。

图4为功放三阶节点示意图。三阶节点包括输入的三阶节点IIP3和输出的三阶节点OIP3。

IIP3、输入功率Pin与IMD3间存在如式(13)所示的关系。利用该关系,可以通过测量输入功率的基波功率、三次谐波功率和输入功率快速计算出IIP3。

图5给出了功放邻道功率泄露比ACPR的定义示意图。具体的定义方式为:

2.2 功放仿真与测试

本文设计的功放工作频段为1.7~2.7 GHz,使用的功放管为CREE公司的CGH40010F。在ADS中搭建的功放拓扑图如图6所示。

在仿真时,设置CGH40010F的相关参数,如表1所示。

图7给出了本文设计的功放实物图与测试平台。在测试中,矢量信号发生器VSG负责射频信号的生成,频谱分析仪VSA负责功放输出信号功率的测量。由于VSA的输入功率不能过高,在功放的输出端接入一个工作频率为5 GHz以下的衰减器。功放总体使用双电源供电。

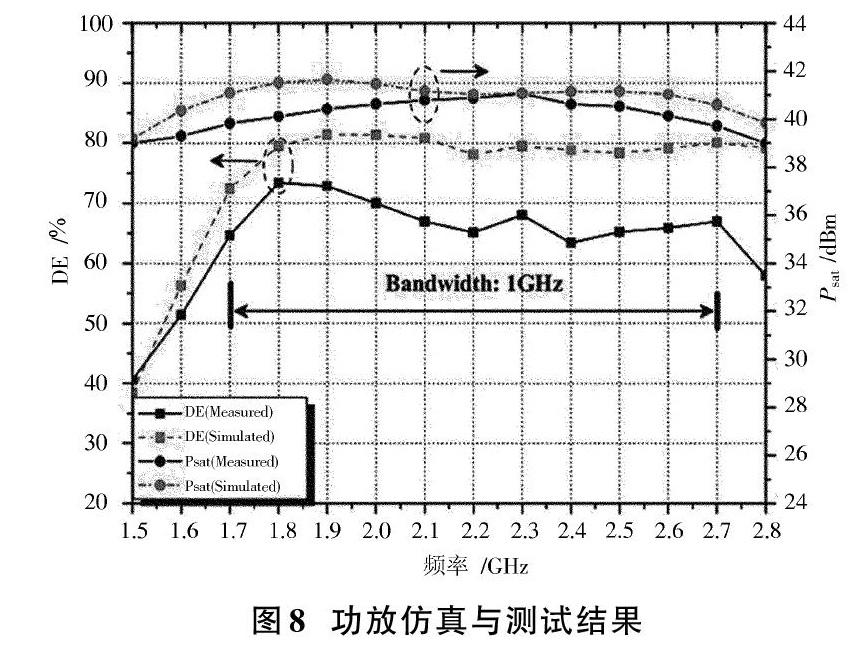

图8给出了功放输出功率和漏极效率的仿真与实际测试结果。从输出功率看,功放在1.7~2.7 GHz之间,仿真的输出功率大于40 dBm,实际测试输出功率大于39.5 dBm。因此,实际测试结果与计算机仿真结果基本吻合。功放的输出功率较大,在整个工作频带内有较高的平坦度;在漏极效率上,本文设计的工作在全频带内,仿真的效率可以达到75%以上。实际测试在1.7~2.0 GHz之内,效率在70%以上,与仿真结果基本吻合;在2.0~2.7 GHz内,效率可以达到65%以上。虽然与仿真结果有所偏差,但也实现了较高的效率,可以满足系统的需求。高频带内效率的偏差主要是由加工工艺造成的。

图9给出了在2.6 GHz时,对功放进行预失真实验的效果图。此时,功放的输出功率为33 dBm,使用信号为40 MHz的OFDM信号,VSA与VSG的采样速率设置为160 MB/s。在进行预失真前,功放的ACPR为-34.5 dBc/-33.6 dBc,预失真后的ACPR为-47.4 dBc/-48.3 dBc。通过预失真,在保证功放效率的同时,可以降低功放的非线性,提升功放输出的调制信号质量。

3 结 语

本文面向高带宽、高功率、高效率射频前端应用场景,对功率放大器设计的相关理论进行了研究。文中的第一部分对连续F类功放的实际理论进行阐述,第二部分基于这些理论进行功放的仿真、实物制作和调试测试。本文设计的功放可以在1 GHz带宽内,实现39.5 dBm的高功率与大于65%的高效率。因此,该功放可以满足通信基站的发展及未来的应用需求。

参考文献

[1] 程知群,张志维,刘国华,等.基于GaN HEMT的混合EF类功率放大器设计[J].微波学报,2019,35(2):34?37.

[2] 李玉龙,宋树祥,岑明灿,等.1.25 GHz高效率F类射频功率放大器[J].微电子学与计算机,2015,32(10):143?146.

[3] 高凯仑,叶焱,谢晋雄,等.一种高效率E~(?1)/F类GaN HEMT射频功率放大器[J].微波学报,2019,35(4):42?46.

[4] 谭大伦,张海.数字预失真器OP6180在宏基站中的应用[J].通信技术,2019,52(6):1534?1540.

[5] 劉亚会.基于FPGA的宽带数字预失真实现技术研究[D].北京:北京邮电大学,2014.

[6] 侯昊民,何进,彭尧,等.一种0.13 μm CMOS K波段宽带功率放大器[J].微电子学,2019,49(5):593?597.

[7] 张书源,钟世昌.基于谐波抑制的内匹配高效GaN功率放大器设计[J].电子器件,2019,42(3):608?612.

[8] 杨瑜,徐立.一种VHF频段放大器的数字预失真设计与实现[J].电子信息对抗技术,2018,33(1):73?77.

[9] 陈斌,黎绍峰,牛绍伍.宽频段大功率射频前端的设计问题[J].电子科技,2017,30(9):156?158.

[10] 张鑫,王斌,熊梓丞,等.应用于无线通信基站的Doherty功率放大器[J].重庆邮电大学学报(自然科学版),2018,30(6):783?788.

[11] 黄亮,李嘉进,章国豪.一种应用于LTE?A的双功率模式宽带功率放大器设计[J].电子技术应用,2017,43(9):30?33.

[12] 胡俊,陈晓娟.基于GaAs工艺的超宽带混合集成功率放大器[J].微电子学与计算机,2018,35(12):59?63.

[13] 李晨.高效率线性Doherty功率放大器研究[D].杭州:杭州电子科技大学,2019.

[14] 徐余龙,施雨,李庄,等.一种W波段SiGe BiCMOS平衡式功率放大器[J].微电子学,2019,49(1):63?67.