VDMOS器件参数及IDSS失效问题研究

2020-07-27李明姚雪霞曹婷刘国梁

李明 姚雪霞 曹婷 刘国梁

摘 要:功率VDMOS就是垂直导电的双扩散结构器件,功率VDMOS克服了其他MOS的各种缺点,是在功率集成工艺基础上发展起来的新一代电子器件。IDSS是衡量VDMOS器件性能的一个重要参数,同时,影响VDMOS产品良率的各个参数,也是一个难以解决的问题。从VDMOS器件结构及工艺入手,对参数失效原因做了较全面的分析,总结了VDMOS器件参数失效的因素及对应的工艺控制难点。以供VDMOS工作者以及相关技术人员参考。

关键词:VDMOS;IDSS;DS漏电;DS 短路

中图分类号:TN386 文献标识码:A 文章编号:2096-4706(2020)06-0027-04

Abstract:Power VDMOS is a vertically conductive double-diffusion structure device,which overcomes various shortcomings of other MOS and is a new generation of electronic devices developed on the basis of power integration technology. IDSS is an important parameter to measure the performance of VDMOS devices. Meanwhile,it is also a difficult problem to solve that various parameters affect the yield of VDMOS products. Starting from the structure and technology of VDMOS device,the cause of parameter failure is analyzed comprehensively,and the factors of parameter failure of VDMOS device and the corresponding process control difficulties are summarized. For reference of VDMOS workers and related technicians.

Keywords:VDMOS;IDSS;DS leakage;DS short

0 引 言

功率半導体器件VDMOS结构,即垂直双扩散形成表面沟道的MOS。是多子主要电子参与器件,所以具有MOS功率器件的优点,比如:生产工艺简单、开关速度快、容易实现短沟道、驱动功率小。VDMOS采用自对准工艺,降低生产工艺对准难度,并且元胞是并联的,具有负的温度系数,易实现大电流和更宽的安全工作区。同时,其工艺特点决定了它能方便地和其他类型的器件相集成,推动了电力电子技术的发展。

VDMOS的应用范围涉及开关电源、汽车、通信、手机、电脑、工业、航天、办公用品等,其应用非常广泛。目前,全社会都在提倡节能降耗、绿色环保,功率MOSFET对节约能源、提高小功率装置的效率和性能具有重要的意义。特别是在照明开关驱动方面,有巨大的市场。因VDOMS有开关速度快、功率低、开关损耗低等优点,对我国绿色照明工程有巨大的帮助。本文针对本公司VDMOS生产过程中VDMOS产品参数失效的问题的研究,特别IDSS失效问题进行多方面的研究。

1 VDMOS器件关键参数介绍

如图1所示,VDMOS结构就是P型注入和N+注入后两次扩散形成P型区和N+型区,在硅表面P型区和N+型区之间形成沟道,在栅极加压后沟道开启,电流在沟道内沿表面流动,然后垂直地被漏极收集,图中S为源极,D为漏极,G为栅极。VDMOS的制造工艺过程中采用自对准双扩散工艺,自对准因为不会产生跑偏问题,可以精确控制沟道长度、短沟道与穿通电压的矛盾。VDMOS结构中,若沟道长度太短,当源漏电压较大时,在达到结的雪崩击穿电压之前,源漏之间已经穿通,也就是源漏电压未达到设计的击穿电压。若想获得更高的击穿电压就必须加大源漏结间的距离,但这样会使器件跨导变小,降低频率特性。而采用双扩散工艺可以克服这一矛盾,在N-外延层上进行P区和N+区双重扩散,精确控制沟道长度、形状。漏区与沟道之间存在着N-外延层,它使PN-结的耗尽区主要向N-区一侧扩展,从而有效地阻止了穿通效应的发生。外延层厚度可做得足够大,以达到击穿电压的要求。

VDMOS器件关键参数包括开启电压(VTH)、导通电阻(RDSON)、源漏击穿电压(BVDSS)、栅源漏电(IGSS)、源漏间漏电(IDSS)等。

开启电压:VDMOS的有源区在栅电压的控制下,逐渐由耗尽变为反型,直至形成导电沟道。则当有源区达到表面反型形成沟道的最小栅源电压,我们定义它为VDMOS开启电压,用VTH表示。可能造成VDMOS开启电压用VTH超规格的原因:沟道区的掺杂浓度(P-BODY的注入剂量、驱入)、栅极氧化层的质量以及厚度。

导通电阻:每个VDMOS结构都可以说由八部分电阻组成(如图2所示),也就是说电流由源极流向漏极需要经过这八部分电阻,分别为:源极接触电阻(Rcs);源区体电阻(Rbs);沟道电阻(Rch);积累层电阻(Ra);结型场效应晶体管电阻(Rj);外延层电阻(Re);衬底电阻(Rbd);漏极接触电阻(Rcd)。可能影响VDMOS导通电阻的因素为源极接触电阻,此区域为重掺杂,占导通电阻的比例很低,一般不会发生异常;沟道电阻,沟道长度(SRC/BODY的结深)的大/小,造成沟道电阻偏大/小;积累层电阻,积累层电阻占RDSON的比例很小,产生问题的可能性很小;外延层电阻,外延层的厚度/电阻率都直接影响到阻值;衬底电阻,衬底为重掺杂,电阻率比较低,但是衬底很厚,由衬底的厚度决定衬底电阻大小;漏极接触电阻,主要是金属和D极接触的电阻,与背面金属电阻和金属和背面材料接触合金有关。

源漏击穿电压:对于VDMOS这种结构,源漏击穿电压BVDSS规定为Vgs=0时在源漏间所加的最大反偏电压,它表征了器件的耐压的极限能力。反偏电压的击穿主要是以突变结PN-结的雪崩击穿方式决定的,而且由于没有少子贮存效应,不存在二次击穿,因此简化了对击穿特性的研究。可能影响源漏击穿电压因素:P-BODY/N-EPI之间的结出现问题,漏电变大,击穿电压变低;P-BODY掺杂浓度/驱入异常;改变BODY注入剂量/驱入,可以最直接/有效地影响漏击穿电压;EPI缺陷;分压环异常;表面缺陷,造成表面漏电。

栅源漏电(IGSS):IGSS是指在指定的栅极电压情况下流过栅极的漏电流。可能影响栅源漏电的因素:栅极氧化层质量;POLY层次的残留;CONT的对偏,CONT对偏直接会造成G/S短路;S/G之间金属残留。

源漏间漏电(IDSS):IDSS是指在当栅极电压为零时,在指定的源漏电压下的源漏之间的泄漏电流。既然泄漏电流随着温度的增加而增大,IDSS在室温和高温下都有规定。漏电流造成的功耗可以用IDSS乘以源漏之间的电压计算,通常这部分功耗可以忽略不计。源漏间漏电IDSS是衡量VDMOS器件性能的一个非常重要的参数,一般VDMOS产品要求IDSS<100 nA,若IDSS偏大,轻则使功耗增大,器件寿命缩短,重则导致DS短路,器件功能不正常。同时,VDMOS器件失效项目中,IDSS也是非常难解决的问题。由此可见,对IDSS失效的控制对于VDMOS器件来说是非常重要的。

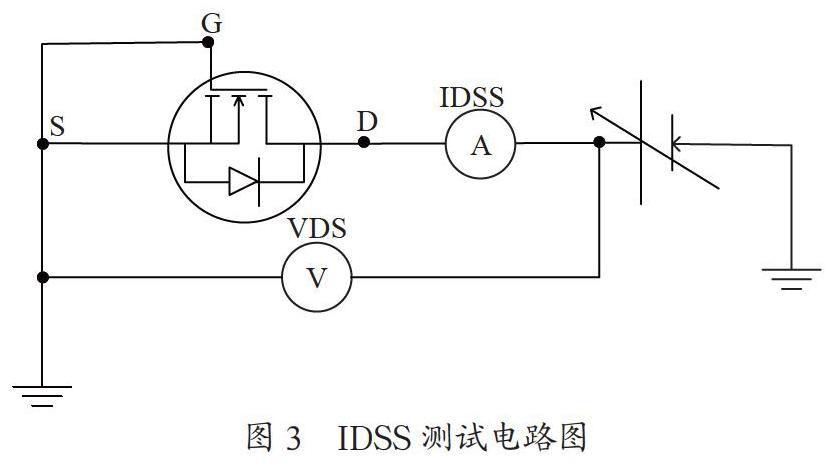

测试电路如图3所示,GS短接接地,在DS间加设定正向(反向)偏压VDS,测量DS间的电流为IDSS,一般IDSS测量规范小于100 nA。

2 IDSS失效原因分析

图4为平面VDMOS器件的剖面结构。对于VDMOS器件来说,一个芯片可能由成千上万如图4所示的元胞构成,任何一个元胞源漏漏电偏大或者短接都会导致整个器件失效。IDSS失效一般都不会是短路,而是漏电偏大。短路的话,就直接是P-BODY/N-EPI的结击穿了。

从剖面结构分析以及VDMOS器件特点可知,导致源漏漏电偏大甚至短接的主要原因有以下几种:设计原因导致漏电偏大;工艺条件对源漏漏电的影响;在线生产过程沾污对源漏漏电的影响汇总。

2.1 设计原因导致源漏漏电偏大

VDMOS器件20 V到1 200 V设计都有,不同电压设计不同。设计主要是产品BV不够导致源漏漏电偏大较多。

设计造成产品BV不够导致源漏漏电偏大要有以下几种:环区注入宽度不够;环区离截止环多晶场板距离不够;沟道太短,沟道设计太短会出现短沟道效应,导致源漏漏电偏大。

环区注入宽度不够或环区离截止环多晶场板距离不够会影响环区在高压下耗尽宽度并影响耐压,导致相应条件下测试漏电很大;1 000 V产品IDSS测试条件是偏压VDS= 1 000 V,环区注入宽度和环区离截止环多晶场板距离对应的源漏击穿电压和IDSS测试结果如表1所示。

2.2 工艺条件对源漏漏电的影响

工艺条件造成产品BV不够或者饱和掺杂导致源漏漏电偏大主要有以下几种:环区注入剂量;衬底EPI电阻和厚度。表2表示环区注入剂量与源漏击穿电压和IDSS的关系;衬底EPI电阻/厚度与源漏击穿电压和IDSS的关系如表3所示。

2.3 在线生产过程沾污对源漏漏电的影响汇总

(1)VDMOS生产过程中要分开硼磷分开,避免沾污,特别是高温炉管和炉前清洗必须分开。不然会存在互相沾污影响产品参数;比如硼1 150 ℃扩散时产品有磷沾污,会导致IDSS低良,如图5所示,深色区域表示IDSS失效,BV击穿会变软击穿,所以会导致IDSS测试不过。

(2)VDMOS生产过程中的光刻涂胶过程都会清洗背面,若背面有光刻胶残留,等到下一步炉管高温作业时会影响下一片的正面;这些沾污会导致IDSS漏电变大,如图6所示,深色区域为IDSS失效,测试结果如表4所示。

(3)VDMOS生产过程中离不开CASSETTE,每一批WAFER都装在CASSETTE,若CASSETTE与WAFER接触位置比较脏,会沾污WAFER,导致WAFER接触位置IDSS偏大,产品低良。如图7所示,深色区域表示CASSETTE与WAFER接触位置IDSS低良,测试结果如表5所示。

3 结 论

本文介绍VDMOS的结构、介绍制造过程中自对准双扩散工艺,及此工艺的优点所在。让大家能够清晰地了解VDMOS的结构和自对准双扩散工艺。还讲解了VDMOS静态参数,同时根据经验总结出影响参数的相关因素,方便大家分析参数异常。最重点是根据实验列出影响IDSS相关因素,方便为大家提供设计及生产过程中的VDMOS低良参数作为参考。

参考文献:

[1] BALIGA B.J. The future of power semiconductor device technology [J].Proceedings of the IEEE,2001,89(6):822-832.

[2] 陆宁.关于VDMOS栅源漏电问题的研究 [J].电子与封装,2010,10(12):27-31.

作者简介:李明(1984-),男,蒙古族,內蒙古通辽人,工程师,多年从事半导体行业,熟悉VDMOD设计和生产工艺,毕业于辽宁大学电子科学与技术专业,本科,主要研究方向:半导体工艺流程设计、产品良率控制。