铪基高κ材料研究及进展

2020-07-25程文海周涛涛卢振成王凌振蒋梁疏

程文海,王 海,周涛涛,卢振成,王凌振,蒋梁疏

(浙江凯圣氟化学有限公司,浙江 衢州324004)

1961 年首次生产出Si 半导体集成电路上只含了4 个晶体管,仅4 年后即1965 年集成电路上就集成了64个晶体管。有了前期知识的积累,1965年底Intel公司创始人之一MOORE 提出了有名的Moore定律,按照等比缩小的原则,朝着单个晶体管更小、集成度更高、功耗更低和速度更快的方向发展,硅基MOS(金属氧化物半导体)集成电路一直遵循这一规律。

传统的栅介质层SiO2由于具有良好的热稳定性,以及非常出色的界面特性,使其在Si 基集成电路领域被使用了长达半个世纪之久。但是,元器件关键尺寸按照Moore 定律缩小,栅介质层厚度的不断减薄,随着器件尺寸进入到90 nm 技术节点的时候,SiO2的厚度已减小至1.2 nm,沟道势垒高度将因漏电流增大而降低,在2 nm 以下,由于电子的隧穿效应,使用SiO2作为栅极介电层产生的泄漏电流不再可接受[1-2]。因此,在进入到45 nm技术节点时,需要使用高介电常数(κ)栅介质替代传统的SiO2栅介质,同时可获得更大的栅介质的物理厚度,从而有望解决因栅极漏电而引起的电路失效问题。

1 Hf基高κ材料

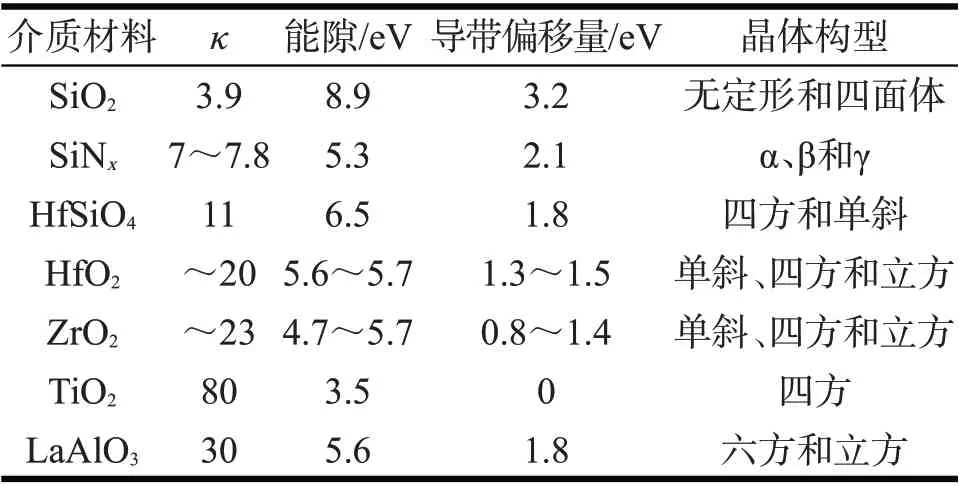

从上世纪90 年代末开始,国内外分别对高κ材料的系统性研究,直到2007年,Intel公司45 nm技术节点首次采用后栅工艺使用氧化铪(HfO2)材料作为高κ栅介质层,这是HfO2高κ材料的首次量产,从此确定了HfO2在高κ栅极介电材料领域的主导地位[3-5]。几种常见栅介质材料性能对比见表1[6]。

表1 常见栅介质材料性能对比Tab 1 Comparison of the performance of common gate dielectric materials

虽然HfO2有较大的κ(~20)、大的禁带宽度(~5.7 eV)、良好的热力学稳定性和与Si衬底有合适的能带偏移[7]。但随着电子元器件尺寸进一步减小,高纯非晶态HfO2的κ已经不能再满足集成电路发展需求。与SiO2相比,HfO2本身存在着诸多不足,比如HfO2也有一些内在的缺陷,如结晶温度较低、易产生氧和杂质渗透及缺陷[8];再者HfO2与Si直接接触会显著降低衬底Si 中载流子的迁移率,再结晶时会成为氧原子或杂质原子扩散的通道,进而引起漏电流增加或在HfO2与Si 衬底之间产生SiO2界面层[9]。为满足生产需要,研究者通常采用掺杂或杂化方式改变HfO2性能,形成新的Hf基高κ栅介质材料。

对于简单掺杂改变κ,目前主要研究较多的掺杂元素包括Ti、Al、Zr、Ta、Si、N 等,形成HfTiOx、HfAlOx、HfZrOx和HfSiON 等结构[10-14]。或者掺杂一些稀土元素,如元素La或Y形成HfLaOx或HfYOx等结构,在HfO2掺入稀土元素形成Hf 基高κ栅介质材料,可有效增加κ、改变电子结构、抑制氧空位的生成和增大能隙,从而提高其在MOS器件中应用性能[15-16]。

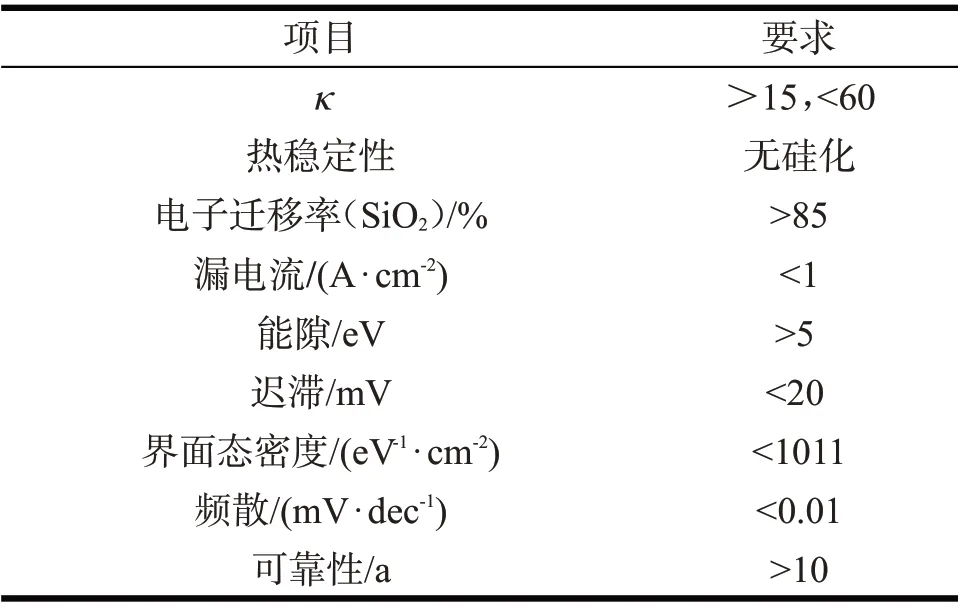

Hf基高κ材料在保持等效氧化层厚度(EOT)的同时可以拥有更大的物理厚度,这样可以减小栅电极与沟道间的直接隧穿电流。在选择Hf基高κ材料除考虑有较高的κ外,还需满足[17]:

1)Hf 基高κ材料有较高的结晶温度,结晶后晶界会为载流子提供通道导致漏电流增大,所以期望MOS 元器件制造过程中在高温处理下Hf 基高κ材料仍处于非晶状态。

2)Hf基高κ薄膜沉积在Si衬底上后热力学稳定性良好,尽量避免热处理过程中高κ栅极电极和Si衬底之间发生反应,生成低κ界面层。

3)禁带宽度要大,介质导带与硅导带间势垒要高,载流子迁移率要低,界面态密度及缺陷密度要低。

理想高κ栅介质材料要求见表2。

表2 理想高κ栅介质材料要求Tab 2 Requirements of ideal high-κ grid dielectric materials

2 制备方法

制备Hf 基高κ薄膜的方法多种多样,如溶胶凝胶法、化学气相沉积(CVD)、物理气相沉积(PVD)、分子束外延(MBE)、脉冲激光沉积(PLD)和原子层沉积(ALD)等[18-25]。

ALD 技术可以将薄膜淀积厚度精确控制到原子层水平,高的深宽比沟槽、高密度的非晶态薄膜、通孔样品以及纳米粒子粉末都会保证100%台阶覆盖率,并且能保证薄膜生长具有良好的均匀性和优异的电学特性。ALD还对数据存储器、微电机系统(MEMS)、显示面板等这些需要高质量,高均匀度以及超薄薄膜器件的发展以及应用有着巨大的潜力。

2007 年,Intel 公司应用ALD 技术沉积HfO2制成45 nm鳍式场效应晶体管(Fin-FET),产业和学术界对这种介质沉积方法开展了大量的研究。ALD技术可以从原子水平上在Si 衬底表面实现原子层的堆积,从而可以保证薄膜生长的均一性和一致性。与CVD 技术类似,ALD 技术也是在通过在衬底表面发生化学反应而生长薄膜。不同的是ALD基于2 步独立且自限制不断循环,可以精确控制每一次循环的厚度,实现原子层精确叠加。随着日趋减薄的EOT 厚度,ALD 技术沉积高κ介质止逐渐成为无法替代的新型栅介质沉积方法。此外,这种ALD技术沉积方法台阶覆盖率高且覆盖厚度均一,因此可以实现多维复杂结构上的薄膜沉积。

丁士进等用ALD 技术制备Al2O3/HfO2纳米叠层薄膜作为绝缘介质层,得到高性能金属-绝缘体-金属(MIM)电容器,每个Al2O3和HfO2单层的厚度通过ALD的反应循环次数来控制,该方法生长很薄的薄膜时可以达到精确的厚度控制,所制得的电容器可分别满足射频旁路电容器和模拟电容器的基本要求,在10 kHz~20 GHz 内稳定的高电容密度12.8 fF/μm2[26]。陆旭兵等公开了1 种面向铁电存储器应用的ALD制备Hf0.5Zr0.5O2铁电薄膜的方法,以Hf 源和Zr 源分别作为反应前驱体,H2O 为氧源,腔体温度是270 ℃,反应前驱体加热温度是80 ℃,得到Hf0.5Zr0.5O2铁电薄膜,具有薄膜铁电性均匀、剩余极化强度大、介电常数大、漏电流小的优异等性能[27]。

LEE等以三(N,N'-二异丙基甲酰胺基)镧、四-(乙基甲基)酰氨基铪为前驱体,以H2O 为氧源,在Si 基板通过ALD技术沉积得到可应用于高κ栅极电介质的LaHfOx纳米层压膜。获得薄膜EOT 在1.23~1.5 nm,漏电流密度为13×10-9~13×10-6A/cm2(平带电压为1 V)。该薄膜在950 ℃时仍保持非晶态,这表明其非常好的热稳定性[28]。

3 应用现状

Hf基高κ材料用途主要包括2类,用于储存器的电容介质(如DRAM)和用作晶体管MOSFET 的栅膜介质,二者对高κ介质材料的要求也不同。作为储存器的电容介质要求高κ薄膜具有顺电相,通常κ越高越好,还需满足漏电流低、介电损耗小、击穿电压高、翻转时间短、耐疲劳性能好等要求。作为晶体管MOSFET 的栅膜介质要求κ不能太高也不能太低,κ过高,即材料的物理厚度太厚,会产生边缘效应,在工艺生产中将出现光刻深度及布线时的爬坡等问题;κ如果过低,则体现不出新型栅介质的优越性。栅介质的κ与能隙存在一定的负相关关系,因此在选择材料时能带和介电常数之间存在着一定的权衡。除此之外,在将高κ栅介质材料应用于电子元件时,为了保证元件性能还必须考虑一些其他因素如低缺陷密度和界面陷阱等。因Hf基高κ材料作为栅介质广泛应用于VLSI,因此介绍Hf基高κ栅介质材料的应用。

集成电路制造过程,当晶体管尺寸缩小时,短沟道效应是最重要的问题,沟道的势垒高度将因漏电电压增加而降低,从而引起热电子发射电流增大。为了解决以上问题,MA等采用具有TiN/HfZrO2栅堆叠材料制备多晶硅隧道场效应薄膜晶体管(TFET),研究表明,该多晶硅TFET 低阈值电压为~-1.218 V、亚阈值摆幅(SS)为~-0.311 V/dec,并且具有沟道长度不敏感的传输特性[29]。

常规薄膜晶体管(TFT)中载流子输运机理是具有散射效应的热电子发射,采用漂移扩散输运模型解释此陷阱态能级诱导能垒增高,从而产生较强的沟道长度依赖性。对于多晶硅TFET 而言,载流子输运机理是带间隧道,受沟道长度影响较小,包括带间隧道效应和陷阱隧道效应。多晶硅TFET的不同载流子输运机理将导致栅介质厚度效应。与多晶硅TFT 相比,当多晶硅TFET 栅介质HfZrOx厚度从18 nm 减少到10 nm 时会增加栅极电容密度,并且多晶硅TFET 的SS 和通态电流表现更好。这表明具有较高栅电容密度的多晶硅TFET将会替代传统的多晶硅TFT在3D IC的应用。

ROLLO 等以高κ介电材料(HfO2)为对象,研究了高深宽比为特征的传感器鳍式场效应晶体管(Fin-FET),优化设计FET 以得到更高的跨导(从而获得较好的信噪比)、更大的动态范围和化学稳定性。传感器Fin-FET高深宽比的几何形状可以提供更高电流,以及更高平面沟道传导比,比传统硅纳米线更可靠。这种具有HfO2的Fin-FET结构器件对输出和传输信号提供了最佳线性响应,并且提供了更宽的动态范围,也显示出最佳的化学稳定性。因此该认为高深宽比Fin-FET/高κ介电体系(HfO2)提供了综合性能最佳的基于FET的传感器[30]。

有机-无机杂化材料由有机相和无机相相互作用形成的一类新型材料,有机相和无机相相互作用力包括氢键、范德华力、共价或离子化学键。因为这类材料的化学键极为丰富,使其特性可调节,因此可以设计出具有合适的机械、光学或电气特性的杂化材料。

RAO等低温下采用溶胶-凝胶法制备了无机-有机HfO2-GPTMS 杂化膜,该杂化膜可应用于高κ栅。采用椭圆偏振光谱分析(SE)、AFM、FESEM、FTIR、TGA 和XPS 等技术表征杂化膜。研究表明杂化膜表面均匀光滑,具有高光学透明度。金属-绝缘体-金属(MIM)结构电压与电容的介电性能关系通过测量漏电流来表征。根据此分析,漏电流密度为0.1 μA/cm2(1 MHz)时,电容和介电常数分别为51.3 nF/cm2和11.4。该杂化膜作为薄膜晶体管(TFT)介电栅的电性能,通过在ITO玻璃基板上沉积法制备TFT 底栅介电层(HfO2-GPTMS),然后溅射α-IGZO 薄膜作为沟道层,所得TFT 的电学特性显示出良好的饱和度迁移率4.74 cm2/(Vs),阈值电压很低,仅为0.3 V,Ion/Ioff为104,工作电压低于8 V[31]。

对于Hf 基高κ材料在储存器的电容介质应用,LYU 等采用SrTiO3为模板在Si(001)上集成铁电Hf0.5Zr0.5O2和La2/3Sr1/3MnO3底电极的外延双层。与SrTiO3(001)单晶衬底上的等效膜相比,Hf0.5Zr0.5O2膜显示出性能增强。厚度10 nm 以下的薄膜具有34 μC/cm2的残留极化率。Hf0.5Zr0.5O2电容器在4 V 工作电压下具有很长的保存时间,可长达10 年以上,并且在长达10 个循环周期中仍具有很高的耐疲劳性[32]。使用SrTiO3模板在Si(001)上外延Hf0.5Zr0.5O2薄膜,显示出的极强的铁电性能,为硅上单片集成存储器开发提供了方向。

4 结 语

高κ介质材料替代传统SiO2作为栅介质是集成电路发展的必然趋势,其在先进的MOS元器件中得到广泛应用。Hf基高κ材料由于热稳定性好、κ大小合适,因而其是一类很有前途的材料。纯净HfO2自身存在某些物化缺陷,可以通过改变合成工艺或向纯净HfO2中掺入杂质元素,诱导HfO2发生晶相转变,形成杂化Hf 基栅介质薄膜材料是解决纯净的HfO2自身缺陷有效途径之一。

Hf 基高κ介质薄膜制备方法有很多,对于不断缩微化的集成电路,栅介质薄膜厚度越来越小,目前集成电路制程迈向3 nm 节点。ALD 技术在薄膜沉积方面有传统成膜技术所无可比拟优势,其成膜几何厚度已达1 nm,ALD 成膜技术将替换CVD、PVD 等淀积技术成为主流。改善和发展ALD 制备工艺仍是Hf基介质薄膜材料研究中的焦点问题。

Hf 基高κ材料在MOS 元器件制作中有很大应用价值,这是VLSL技术迅速发展对高κ介质材料需求的必然趋势。科学家对高κ材料进行了深入研究,Hf 基高κ材料的研究已取得了很好的成果,并且得到广泛实际应用。但从研究情况分析,Hf 基高κ材料仍然存在很多问题,如Hf 基高κ材料与硅基界面粘合性较差,存在杂质扩散,载流子的迁移率会下降等。因此,如何得到优异综合性能的Hf 基高κ材料是当前材料科研工作者急需解决的主要问题。进一步探索新的Hf 基高κ材料,提高其与衬底材料相容性及改善界面性能,通过掺杂或发展制备工艺获得优异综合性Hf基高κ材料是重要途径。