基于FPGA和FLASH的多路数据存储技术

2020-07-23吴嘉伟魏志强张会新

吴嘉伟 魏志强 张会新

摘 要: 针对多路数据存储中所采集数据传输与存储速率不匹配的问题,提出一种基于FPGA和FLASH的多路数据存储技术。FPGA芯片可以通过RS 422串并转换模块将输入的串行数据转换为并行数据存入第一级数据缓存,主控模块对其重新编帧后存入第二级数据缓存中,最后在FLASH控制模块作用下把数据存入FLASH存储器中。经测试,从FLASH存储器中读取的数据正确,该系统工作可靠。

关键词: 多路数据存储; FPGA; FLASH; 串并转换; 数据缓存; 数据重新编帧

中图分类号: TN919?34 文献标识码: A 文章编号: 1004?373X(2020)04?0034?04

Multi?channel data storage technology based on FPGA and Flash

WU Jiawei1,2, WEI Zhiqiang3, ZHANG Huixin1,2

(1. Key Laboratory of Electronic Measurement Technology, North University of China, Taiyuan 030051, China;

2. MOE Key Laboratory of Instrumentation Science & Dynamic Measurement, North University of China, Taiyuan 030051, China;

3. Beijing Institute of Aerospace Metrology and Testing Technology, Beijing 100076, China)

Abstract: A multi?channel data storage technology based on FPGA and Flash is proposed to improve the mismatch between the collected data transmission rate and its storage rate in multi?channel data storage. The FPGA chip is adopted to convert the inputted serial data into the parallel data by means of the RS?422 serial?to?parallel conversion module and store them into the first?level data caching, refresh their frame and store them in the second?level data caching by means of the master control module, and store the data in Flash memory by means of the Flash control module. The testing results show that the data read from the flash memory is correct and the system is provided with reliable run.

Keywords: multi?channel data storage; FPGA; FLASH, serial?to?parallel conversion; data?caching; data frame refreshing

随着我国工业、农业、军事、航天等事业的不断发展,各种电子系统、自动化装置以及传感器等也在不断对其功能和结构进行改进,需要记录和存储的数据也越来越多,常常需要同时采集和存储多个通道的数据。而所采集的数据传输速率不一定可以与FLASH存储器的存储速率相匹配。针对此,提出一种基于FPGA和FLASH的多路数据存储技术,利用FPGA内部的RAM构造两级数据缓存,有效解决了该问题。

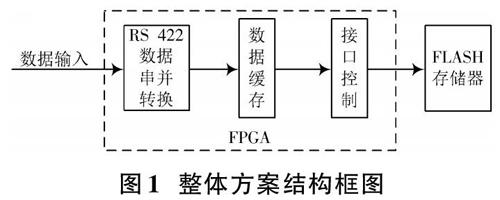

1 整體方案

系统需要完成RS 422数据的串行?并行转换、数据缓存和FLASH接口控制,这几项工作可以由FPGA来完成,而不需要借助其他器件。整体方案的结构框图如图1所示。

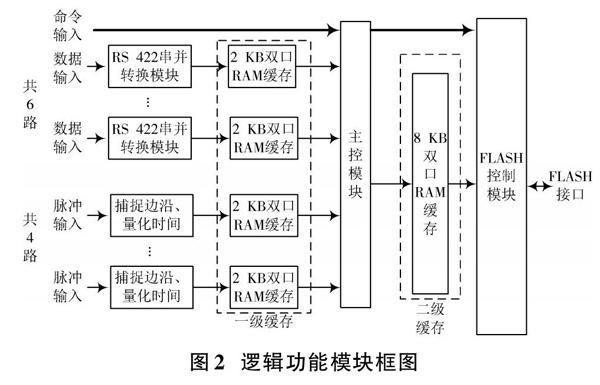

2 FPGA逻辑功能

FPGA的逻辑功能模块主要由RS 422数据[1?2]串并转换模块(2 KB和8 KB的双口RAM缓存)、FLASH接口控制模块和主控模块组成,其组成框图如图2所示。

串并转换模块可以实现UART[3]通信功能,将由1位起始位、8位数据、1位停止位组成的串行数据转换成8位的并行数据,再输入到第一级的2 KB双口RAM缓存中。主控模块是整个FPGA逻辑功能模块的核心,主要负责接收如系统复位、启动采集,以及对FLASH的擦除、读取等控制命令,还能在采集状态中判断一级缓存中的数据量是否达到可以输出的标准,若达到,就将其中的数据读取,按照一定的帧结构编帧并输入到下一级缓存。FLASH控制模块的功能是向FLASH芯片发出命令来控制芯片的读写和擦除。本设计所运用的两级数据缓存,第一级为2 KB双口RAM缓存,用来存放经过串并转换的输入数据,主控模块对其数量进行检测,达到读取标准后即将其读取并重新编帧,写入第二级的8 KB双口RAM缓存中,在FLASH控制模块的作用下写入FLASH存储器中。

在本文设计的系统中,输入的串行数据速率为921.6 Kb/s,所使用的时钟信号的频率为36.864 MHz,将输入数据按每504 B数据和8 B帧标记为一组编为一帧,主控模块判断一级缓存中的数据量是否达到512 B,若达到,则从中读取504 B数据,重新编帧输入第二级缓存。

3 两级数据缓存模块设计

本设计使用的FPGA芯片是Xilinx公司的XC3S400,其中设计有RAMB16_SM_SN随机存储器[4],其中每块RAM都有2 KB的数据存储空间和256 B的校验位存储空间,可以选择适应实际需求的地址和数据宽度。以下分别介绍内部数据缓存模块的两级。

1) 2 KB双口RAM缓存。本设计使用了型号为RAMB16_S9_S9的2 KB双口RAM缓存,其原理图如图3所示,端口A和端口B具有相同的结构,操作方法也是一致的,两个端口的相同地址对应的是RAM的同一個存储单元,且都可以进行读写操作。将端口A和端口B分别设置为写数据端口和读数据端口。ENA是读写、复位使能信号,为低电平时,数据无法写入RAM,输出也不会变化,所以必须使ENA为高电平才能进行读写操作。当SSRA为低电平,WEA(写使能)为高电平时,在时钟信号上升沿,数据由DIA端口写入由ADDRA指示的存储单元;而当SSRA与WEA均为低电平时,在时钟信号上升沿,ADDRA指示单元中的数据会由DOB端口输出[5]。

2) 8 KB双口RAM缓存。8 KB双口RAM缓存的WEA(B),ENA(B),SSRA(B),CLKA(B)的接法可以参照8 KB双口RAM缓存中相同管脚的接法,ADDRA(B),DIA(B)和DOA(B)的接法有所变化。将4块RAMB16_S2_S2组合起来构成8 KB双口RAM缓存。将存入一级缓存的8位并行数据拆解成两位一组分别存入4块RAMB16_S2_S2中,4块RAMB16_S2_S2共用地址线和控制信号,工作状态一致。当输出信号时,将之前被拆分为4组两位数据的8位并行数据重新组合,再输出。8 KB双口RAM缓存的组成框图如图4所示。

4 主控模块控制两级缓存的逻辑

主控模块读取一级缓存中的数据,重新编帧并存入二级缓存。重新编帧的数据以512 B为一帧,包括4 B的帧头FDB18540、1 B的帧标志(分别为00H,33H,66H,99H,CCH,FFH)、3 B的帧计数以及数据。帧头在每一帧数据的最前面,用来指示一帧数据的开始,使数据更有条理便于查看;帧标志的作用是对来自不同通道的数据进行区分;一帧数据结束后帧计数就加一,帧计数可以用来统计数据的量,而且如果帧计数不是连续递增的,就说明有数据丢失的情况出现。帧头、帧标志、帧计数共8 B,从一级缓存中读取的数据有504 B。

主控模块控制两级缓存的工作流程图如图5所示。设备加电之后,直接往第二级缓存中写入设定好的帧头;主控模块对第一级缓存中的数据量进行轮询,如果有完整的一帧,就依次将帧标志、帧计数和第一级缓存中的数据写入第二级。完成以上工作之后,帧计数加一。

5 FLASH控制模块逻辑

FLASH控制模块对FLASH存储器发出指令,FLASH存储器收到指令后执行相应的擦除、写入、读取操作[6]。擦除命令优先级最高,其次为写入命令,最后是读取命令。本设计中擦除和写入是按照顺序进行的。FLASH控制模块的工作流程图见图6。

图6 FLASH控制模块工作流程图

本设计选用型号为K9WBG08U1M的FLASH存储器。该器件的擦除、写入、读取等一系列操作都是通过写入相应的命令来实现的[7],K9WBG08U1M只有一组8位的并行总线,配合锁存信号ALE和CLE来决定输入的是命令、地址,还是数据,从而达到这8位总线的复用[8]。一片K9WBG08U1M有8 192个数据块,每块又包含64页,每页有4 096 B数据。

该芯片按块擦除,按页写入和读取。在擦除、写入、读取前首先要检测无效块[9],方法是:读取每块前两页的数据,如果都为FF,就说明该块有效,可以进行操作;否则,该块为无效块,后续操作应该跳过无效块[10]。

5.1 擦除操作

擦除FLASH的流程图如图7所示。

5.2 写入操作

写入操作的流程图如图8所示。

5.3 读取操作

读取操作的流程图如图9所示。

6 测试结果

测试数据设置为步长为1的递增数,用上位机软件读取FLASH中的数据,测试结果如图10所示。

从图10可以看出数据帧结构与设定的编帧结构一致,每帧数据都由4 B的帧头、1 B的帧标志、3 B的帧计数以及504 B数据组成(图中只显示了部分数据)。

7 结 语

本文提出一种基于FPGA和FLASH的多路数据存储技术,FPGA完成了对输入数据的串并转换、数据缓存和对FLASH存储器的控制。测试结果表明,通过这种技术,数据输入速率和存储速率不匹配的问题可以得到解决,能够正常完成数据记录工作,提高了系统可靠性。

参考文献

[1] 张芹芹,叶冰.一种新型RS 422总线数据提取技术[J].中国科技信息,2018(2):26?27.

[2] 吕波,张涌,黄侃,等.基于FPGA的四口RAM设计与实现[J].仪表技术与传感器,2017(1):34?37.

[3] 贾亮,冀源.基于FPGA的串口通信控制器设计[J].微型机与应用,2016,35(22):33?35.

[4] 吴文杰,李利品,王杏卓,等.多道能谱仪ARM与FPGA高速数据并行通信设计[J].核电子学与探测技术,2017,37(11):1151?1155.

[5] 赵倩,唐磊.一种基于NAND FLASH的多通道存储系统编址方式研究与实现[J].微电子学与计算机,2018,35(9):32?36.

[6] 代明清,边庆,周啸,等.基于NAND FLASH的高速大容量存储系统设计[J].电脑知识与技术,2018,14(13):208?210.

[7] 张惠臻,周炎,王成.基于 NAND FLASH的嵌入式大规模数据存储机制[J].华中科技大学学报(自然科学版),2017,45(1):46?51.

[8] 高阳,王代华,王晓楠.存储测试系统中FLASH的存储可靠性技术研究[J].现代电子技术,2017,40(18):131?134.

[9] 王美丽.FPGA中BRAM的设计[D].西安:西安电子科技大学,2012.

[10] 边大亮.基于闪存的双通道图像记录器设计与实现[D].太原:中北大学,2015.

[11] 童巍.散货堆场地图系统关键技术的研究和实现[D].上海:上海交通大学,2017.