一种用于自适应直方图均衡化的硬件加速器

2020-07-09陆申阳郭爱英沈华明

陆申阳,冉 峰,郭爱英,沈华明

(1.上海大学微电子研究与开发中心,上海200444;2.上海大学新型显示技术及应用集成教育部重点实验室,上海200444;3.上海大学机电工程与自动化学院,上海200444)

低照度夜视系统主要用于夜视成像、汽车驾驶辅助、安防监控等领域,是一种非常重要的图像增强技术,在军事和民用方面都被广泛应用.但是,在低照度环境中理想的光照条件和曝光度往往难以得到满足,摄像头捕获到的视频图像存在亮度低、噪声大、对比度低等缺点,直接影响到后续的图像处理质量.针对低照度视频图像的处理需求,图像增强技术应运而生.传统的图像增强技术,如直方图均衡化、伽马校正、色调映射等,往往存在图像曝光过度、暗区细节丢失、整体对比度低等缺点[1-3].目前由于广泛使用的经过优化的直方图均衡化技术、暗通道算法、神经网络算法、Rtinex算法等过于复杂,计算量过大,故不宜于硬件实现.

为了克服上述图像增强技术的缺点,学者们主要展开了如下2个方向的研究.

(1)改进图像增强算法[4-9].例如,文献[4]的动态直方图均衡(dynamic histogram equalization,DHE)算法是根据极大值或极小值割直方图后再分别均衡.此算法自适应性强,能有效拉伸集中在低灰度区域的灰度级,但该算法在寻找极小值时容易出错.文献[9]中的反距离加权插值自适应图像直方图均衡化算法(inverse distance weighted interpolation adaptive histogram equalization,IDWIAHE),该算法在非重叠子块直方图均衡化方法的基础上,综合运用每个像素点周边的灰度信息,消除不同子块之间的块效应,较好地保存了图像的细节信息.但是该算法结构非常复杂,难以在硬件上实现.

(2)基于硬件平台设计和优化硬件电路[10-15].文献[10]针对640×480大小的图像在现场可编程逻辑门阵列(field programmable gate array,FPGA)上实现了直方图均衡化电路设计,得到了画面清晰、细节完整的图像,但是由于设计中图像尺寸固定,故难以推广应用.文献[11]在FPGA上以译码器和计数器为基础实现了一个直方图均衡化电路,从而提高了处理速度.但是,由于每个灰度级都需要一个计数器,故当处理高灰度级图像时计数器的个数将倍增;此外,该算法在低灰度区域存在大量的灰度合并现象,导致对比度等级无法区分,画面细节丢失严重.文献[12]也在FPGA上设计实现了直方图均衡化电路,该方法采用乒乓操作,可实现高速连续的图像处理,但是该算法未考虑数字显示与模拟显示的不同,在硬件平台上处理得到的图像严重失真,画面模糊,图像细节全部丢失.

针对上述算法性能和硬件实现无法平衡的问题,本工作提出了一种用于自适应直方图均衡化的硬件加速器(hardware accelerator,HA)的设计方法.首先,针对过度增强、噪声放大、暗区细节丢失、自适应算法复杂等问题对均衡算法做了基于自适应的对比度改进;其次,采用乒乓和对比度策略,将改进型自适应直方图均衡化算法进行基于FPGA的硬件加速器设计;最后,基于实验室和真实场景的实验结果表明,本硬件加速器能够平衡算法性能和硬件实现之间的矛盾,达到了适度提升亮度、对比度,保留图像细节的效果.

1 相关理论

灰度级直方图描述的是一幅图像的灰度分布情况,即图像中每一灰度与该灰度级出现的频数之间的统计关系.经直方图均衡化处理后,图像亮度和对比度得到明显提高,但是增强过程中容易产生过度增强和灰度合并现象,导致噪声放大、图像细节丢失等问题.为了克服传统直方图算法的不足,本工作提出了改进的自适应直方图均衡算法.

1.1 直方图均衡算法

直方图灰度级范围为[0,L−1],其中8位灰度图像L为256.首先根据式(1)计算出每个灰度级对应的像素数量H(rk),其中k=0,1,···,L−1;rk为第K个灰度级;nk为一帧图像中第k个灰度级对应的像素数量,通过累加计算得到

同时得到每个灰度级的概率密度函数

式中:N为图像的总像素数.

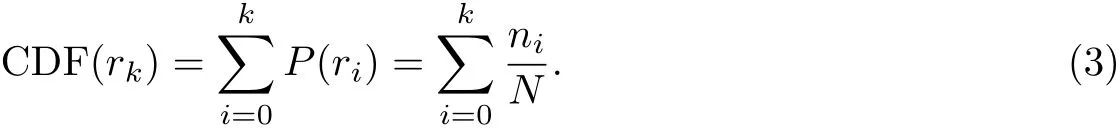

由式(2)的统计结果计算图像灰度级的累积概率密度函数(cumulate density function,CDF)

根据式(3)可以推导出CDF(rL−1)为1,可见图像均衡前后总灰度值不改变.用映射函数S(rk)来描述输入像素与输出像素的关系,

式中:rk为输入的第k级灰度值,S(rk)为输出的第k级灰度值,rL−1为最大灰度值.

1.2 改进型自适应直方图均衡算法

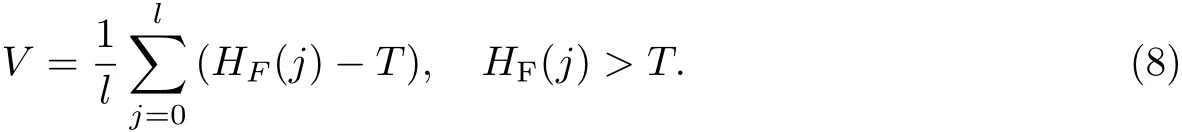

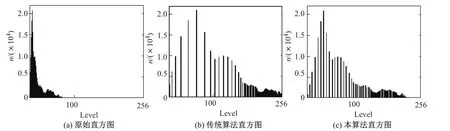

分析式(3)可知,当ni较大时,会导致概率密度函数显著增大,进而导致式(4)中对应输出值及后续输出值普遍偏大,产生过增强、噪声放大现象.当ni的值较小时,会导致概率密度函数只发生微量变化,进而导致式(4)中多个输入rk只对应同一个输出值S,即多个输入灰度值映射出同一个输出灰度值,产生灰度合并现象,导致图像细节丢失、画面模糊.式(3)中的ni来源于式(1)中的nk,对于一幅低照度图像大部分像素点集中在低灰度区域,高灰度区域的像素点个数较少,即低灰度区域nk值较大,高灰度区域nk值较小(见图1(a)),横坐标为灰度级,纵坐标为对应灰度级的像素点个数.因此HE算法会产生大量的灰度合并现象和过增强现象,主要表现为图像模糊不清、细节丢失、偏亮等.

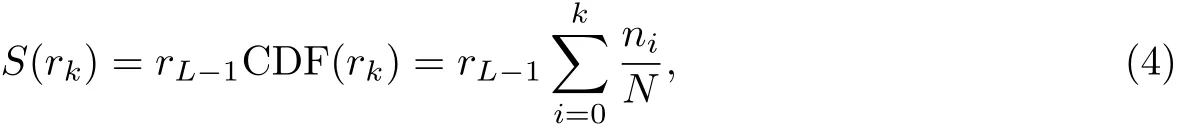

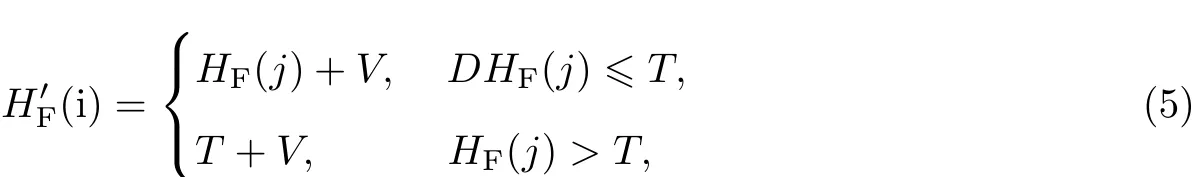

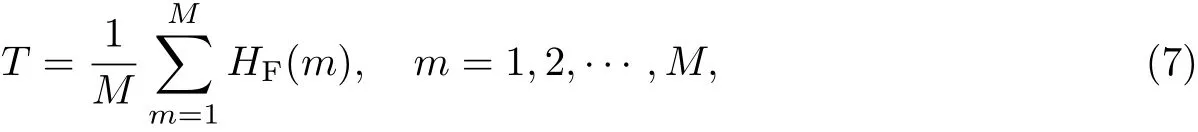

针对HE算法的上述缺点,本工作引入了阈值T和增量V来调整每个灰度级对应的像素点个数nk,实现自适应地限制对比度拉伸程度,抑制灰度合并现象,构建出一种新的改进型自适应直方图均衡化(interpolation adaptive histogram equalization,IAHE)算法.阈值T的引入减少了低灰度区域的像素点个数,而增量V的引入增加了高灰度区域的像素点个数,使得像素点分布更加均匀.此外,在检测峰值前剔除了直方图中的零分量,保证了阈值T计算的科学性和准确性.增量V的引入确保了直方图总面积不变,即在计算概率密度函数时分母N仍然是图像总像素个数,在算法性能提升的同时其计算复杂度未增加.具体改进方法如下.

IAHE算法将HE衡算法中的式(1)替换为

式中:HF(j)为原直方图中的非零分量.

式中:k=0,1,···,L − 1;j=0,1,···,l,l为直方图中非零分量个数.

阈值T由剔除零分量之后的直方图的峰值确定,其表达式为

式中:HF(m)为检测到的局部极大值;M为极大值的个数.

增量V由大于阈值T的直方图分量确定,其表达式为

式(1)替换为式(5)就是对原始直方图自适应调整,其过程如图1所示.

图1 直方图自适应调整过程Fig.1 Adaptive adjustment process of histogram

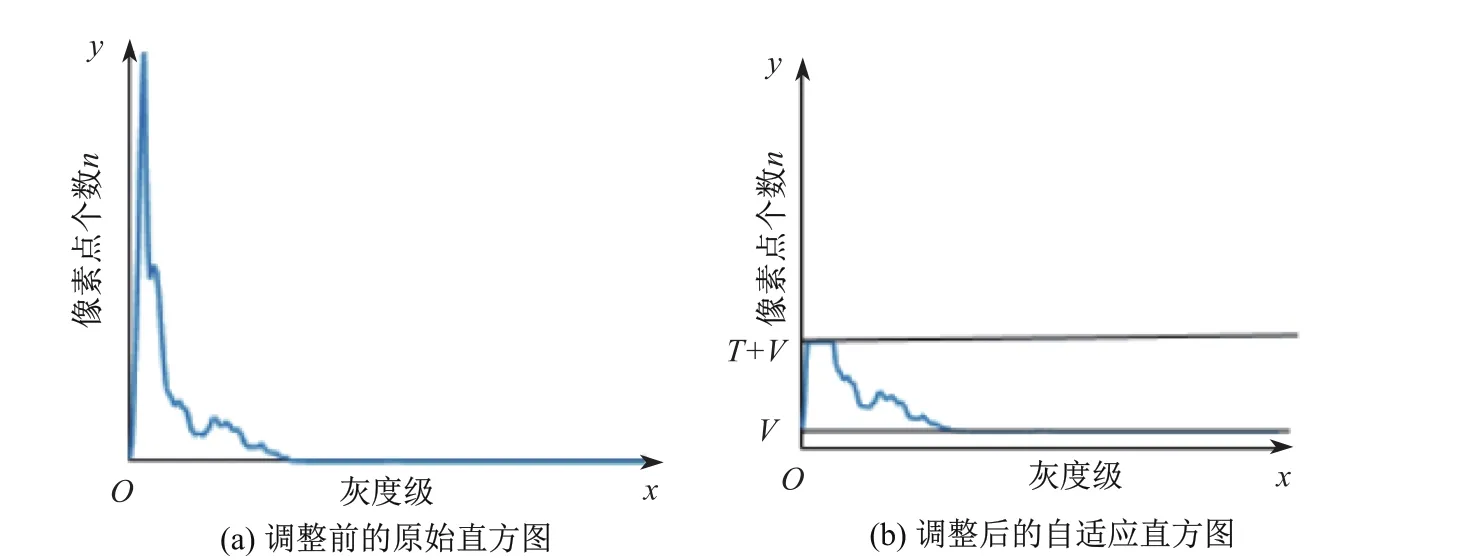

2 硬件加速器的设计

适用于IAHE算法的硬件加速器的实现能提升图像增强的处理速度和增强效果.针对HE算法的硬件实现通常包括3个步骤:统计、累加和映射.这种设计结构精炼、算法简单,在资源面积上占有一定优势,但是过增强和灰度合并现象严重,进而会导致图像增强效果不理想.本工作从增强效果和硬件实现的双需求出发,提出了一种自适应IAHE算法的硬件加速器设计结构,其总体结构如图2所示.

该结构的核心可以分为5个主要部分:控制模块(control module,CM)、缓存控制模块(ache control module,ACM)、统计控制模块(statistical control module,SCM)、自适应调整模块(adaptive adjustment module,AAM)和映射控制模块(mapping control module,MCM).

(1)控制模块主要负责算法的条件判断和信号控制,如累加计算条件的判断信号、使能信号、起始与结束信号的控制等,该模块利用有限状态机(finite-state machine,FSM)实现.

(2)缓存控制模块主要负责存储原始图像信息,用于映射输入,主要利用一块RAM和相应的读写时序控制模块实现.

(3)统计控制模块主要负责原始图像的直方图统计,具体是利用一块RAM和相应的累加计算、读写时序模块实现.

(4)自适应调整模块负责直方图的自适应调整,主要包括阈值T计算模块(T calculation module,TCM)、增量V计算模块(V calculation module,VCM)、直方图调整模块(histogram adjustment module,HAM)和均衡化模块(equalization module,EM)这4个子模块,其中直方图调整模块利用了乘法器、除法器、RAM和相应的读写时序控制模块实现.

(5)映射控制模块负责增强后的图像映射输出,主要利用RAM和查找表来实现.其余模块负责时钟信号的分频、数据的传输与显示等.如开发板的系统时钟频率为27 M,显示器所用扫描时钟频率为74.25 M,且直方图统计模块使用了倍频操作,因此锁相环(phase locoed loop,PLL)模块产生的2个时钟信号clk1,clk2分别为74.25,148.50 M.

图2 IAHE的硬件加速器设计结构Fig.2 Hardware accelerator design structure of IAHE

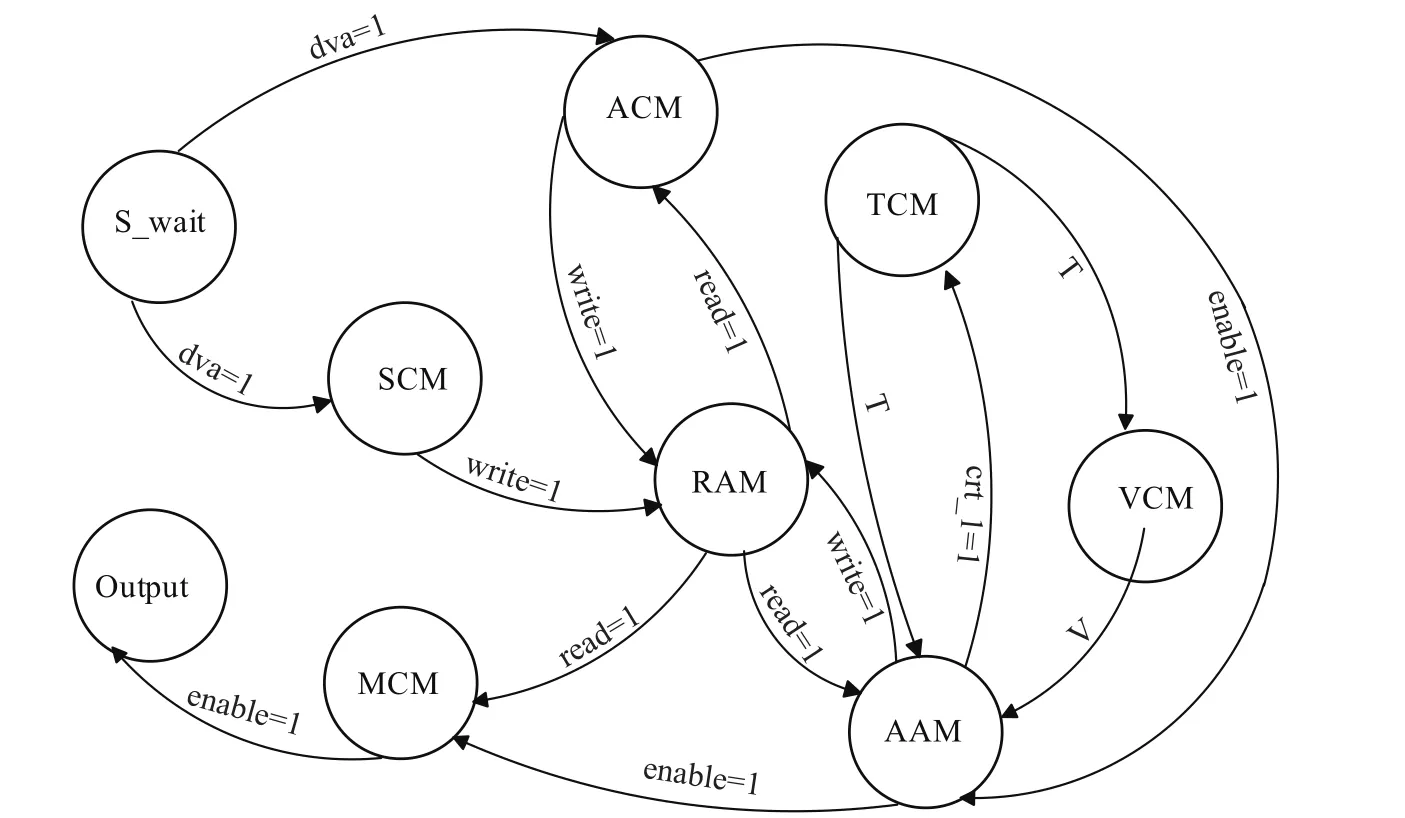

2.1 控制模块设计

控制模块主要用于控制各个模块的工作状态,产生控制各模块的信号并以并行的方式传输给各个模块.图3为控制模块的FSM实现.

首先,在图像增强过程开始之前将初始值设置为0,初始状态设为S _wait的空闲等待状态.当开始图像数据输入时,增强过程开始,此时完成图像数据的缓存以及统计;之后,根据统计出的原始直方图计算出调整参数阈值T和增量V,反馈到原始直方图上对其进行自适应调整,并且完成均衡化操作得到映射查找表.最后用缓存的图像数据通过查找表将输出结果映射并显示出来.

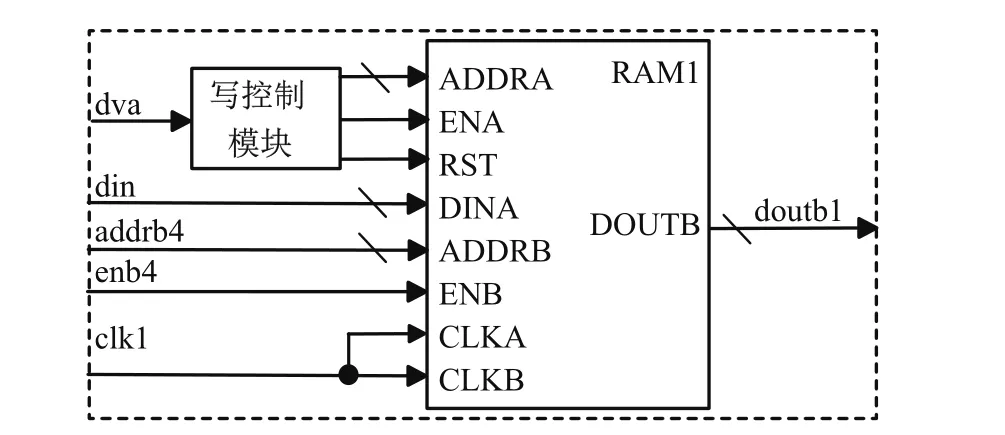

2.2 缓存控制模块和统计控制模块设计

图3 控制模块的FSM实现Fig.3 FSM implementation of the control module

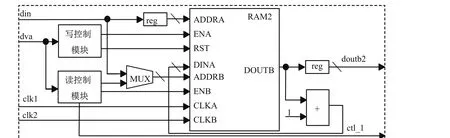

图4 缓存控制模块结构Fig.4 Structure of cache control module

图5 统计控制模块结构Fig.5 Structure of statistical control module

在进行缓存控制和统计控制模块设计时,充分利用FPGA强大的并行性能,缓存和统计操作可以同时进行;另外,缓存与统计过程采用乒乓操作,可以将速度降低一半.缓存控制模块主要用于初始阶段原始图像数据的缓存和最终阶段原始图像数据的输出,该模块由一个RAM和相应的读写模块完成 (见图4).RAM1中数据地址位为18 bit,存储为512×512(像素)的图像,位宽为8 bit,存储256级灰度值.图像数据din[7:0]作为RAM1的输入数据,数据伴随信号dva控制产生读写控制信号和写地址,完成缓存后等待映射控制信号.统计控制模块主要用于初始阶段在图像数据到来时,对图像数据进行直方图统计,该模块主要利用一个累加计算模块、一个RAM和相应的读写模块完成(见图5).RAM2中数据地址位为8 bit,对应256级灰度,将灰度值相同的像素点累加储存在相应的地址上,数据位宽为19 bit.图像数据din[7:0]作为RAM2地址寻找相同灰度级数据位置,数据伴随信号dva控制产生读写控制信号,当完成统计后将统计数据输出,并且产生控制信号ctl _1.

2.3 自适应调整模块设计

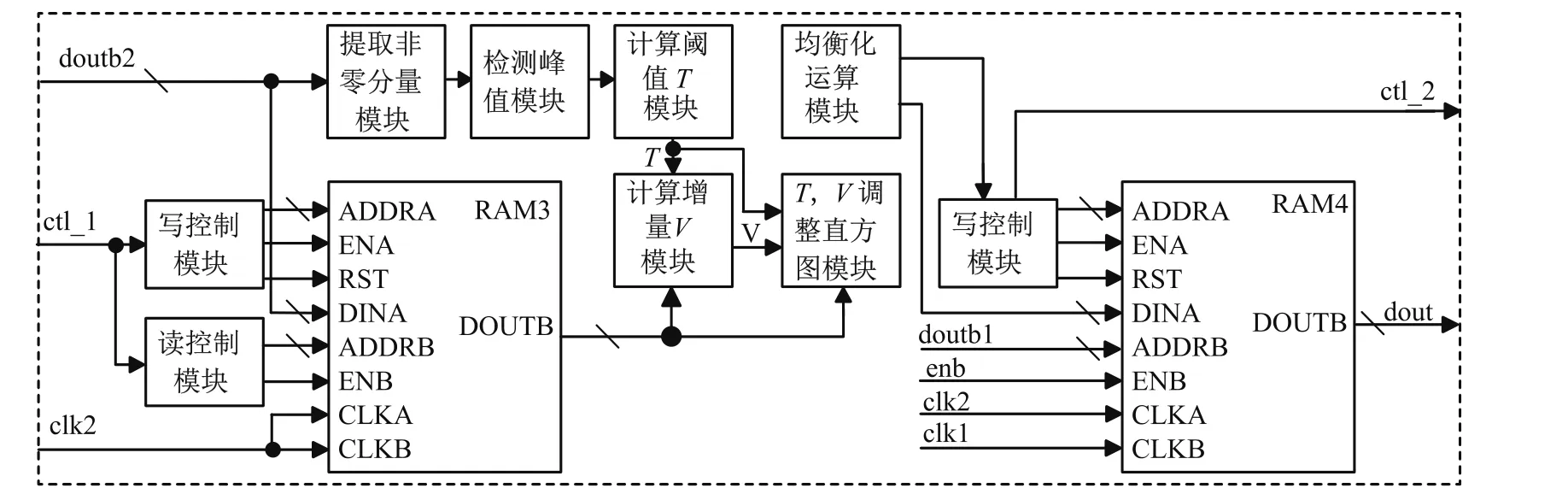

自适应调整模块包括提取非零分量、检测峰值、计算T和V、调整直方图和均衡化运算等子模块.自适应调整模块主要负责直方图的自适应调整和均衡化运算,其结构如图6所示.

首先,输入的原始直方图数据存入RAM3中,同时进行提取非零分量、检测峰值和计算阈值T操作.之后完成阈值T的计算后输出RAM3中的数据并计算增量V,再利用T和V调整直方图.最后,将上一步得到的直方图通过乘法器和相应的运算得到映射数据,存入RAM4中作为查找表.该过程中RAM3地址位宽为8 bit,用于存储直方图数据;RAM4地址位宽为8 bit,用于存储均衡化后得到的映射数据作为查找表.完成以上操作后进入等待状态,其中提取非零分量、检测峰值和计算阈值T同时进行.当完成提取非零分量后,检测峰值和计算非零阈值T也随之完成,所耗时间约为256个时钟周期.计算增量V时需要对每一个灰度级进行操作,也需要256个时钟周期.T,V调整、累加和均衡所耗时间同样约为256个时钟周期.

图6 自适应调整模块结构Fig.6 Structure of adaptive adjustment module

2.4 映射控制模块设计

映射控制模块主要用于产生RAM1的读地址和读控制信号.将原始图像数据读出,作为RAM4的读地址,查询相应灰度级对应的灰度值,从而映射出均衡化后的图像数据.该模块内部结构如图7所示.

3 验证结果分析

基于改进型自适应直方图均衡算法的硬件加速器验证分为算法功能验证和硬件加速器性能验证2个部分.

(1)在PC机上进行自适应算法的能和性能验证.PC机的配置参数为Intel(R)Core(TM)i7-6500@2.5 GHz与4 G内存.仿真软件为Matlab R2016a.

(2)在FPGA开发板上对硬件加速器的性能验证.开发板为AV150 FPGA,核心处理MCU为XC6SLX150.开发软件为ISE14.7,ModelSim SE-64 10.1c.

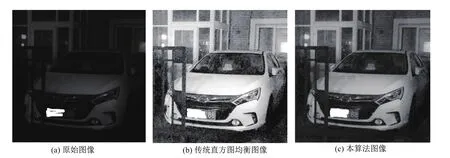

3.1 改进型自适应直方图均衡算法的功能验证与分析

为了验证算法是否能限制图像对比度拉伸、减弱图像增强程度、保留暗部图像细节等功能及性能,使用OV5640摄像头在一天中的6,9,12,15,18,21点等不同光照条件下,对学校以及学校周边的不同环境采集了1 200幅图像,并做了相关系列实验.图8为其中一组低照度图像的实验结果,该图是夜间居民楼旁的白色汽车图像,图像大小为512×512(像素).图8(a)整体偏暗,车窗及墙均不清晰;(b)为采用HE算法处理后的图像,图像整体偏白,成功地提高了图像的对比度,但是图像过亮存在“过增强”现象;(c)为采用本算法处理后的图像,对比度得到适度拉伸,亮度适中,图像细节保留完整.

图7 映射控制模块结构Fig.7 Structure of map control module

图8不同算法的增强效果Fig.8 Enhancement results of different algorithms

图9 是该组图像对应的直方图,横坐标为灰度级,纵坐标为像素点个数.表1统计了不同图像增强算法处理后图像及直方图的特性参数,包括灰度级个数、平均灰度、标准差、过暗区域(灰度值<50)像素点个数占比、过亮区域(灰度值>200)像素点个数占比以及图像的信息熵.

从表1中可以看出,经HE算法处理后的图像有效灰度级从147降低到了68,说明发生了大量的灰度合并现象,导致图像模糊、细节丢失;而IAHE算法的灰度级为97,有效抑制了这一现象.经HE算法处理后的图像平均灰度由21提升到了129,导致图像过亮;而IAHE算法仅提升到81,亮度适中.在标准差一栏中,IAHE算法低于HE算法,有效限制了对比度拉伸,得到的图像较为柔和.研究表1中图像过暗区域和过亮区域后可知,原始图像大部分像素点集中在低灰度,为夜间的低照度图像,大部分背景颜色为黑色,而经HE算法处理后的图像过暗区域占20.44%,过亮区域占22.25%,图像明显偏亮;而本算法的图像暗区占38.65%,亮区占0.57%,得到的图像明亮适中.经IAHE算法处理得到的图像熵值大于HE算法得到的图像熵值,说明IAHE算法得到的图像包含更多的信息.

图9 不同算法直方图对比Fig.9 Experiment histogram of different algorithms

表1 不同算法增强效果对比Table 1 Comparison of different algorithm enhancements

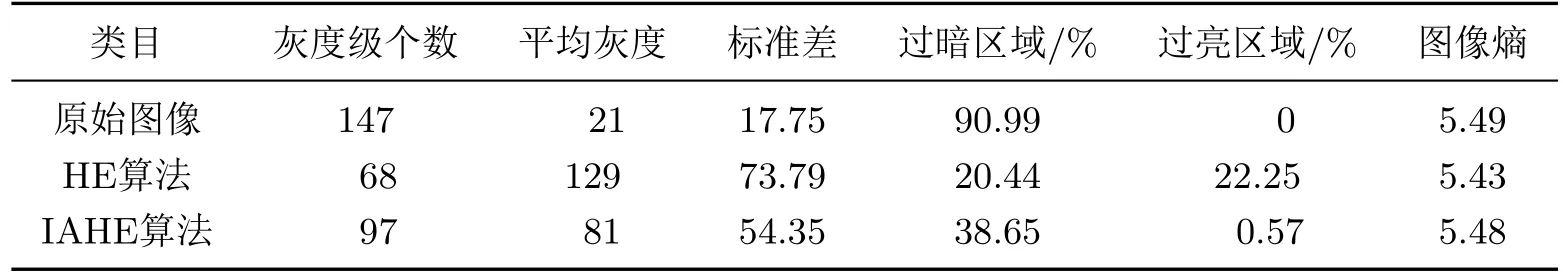

3.2 硬件加速器性能验证与分析

为了验证硬件加速器的性能,本工作开发了图像增强硬件实现验证平台,主要由代码输入与仿真调试窗口、核心处理和处理结果显示这3个部分组成,其实物图如图10所示.图中右侧为代码输入与仿真调试窗口,左下为核心处理部分,左上为处理结果显示部分.

图10 图像增强硬件实现验证平台Fig.10 Verification platform of image enhancement hardware implementation

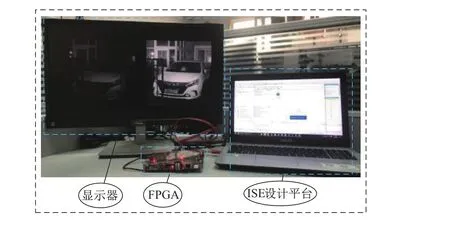

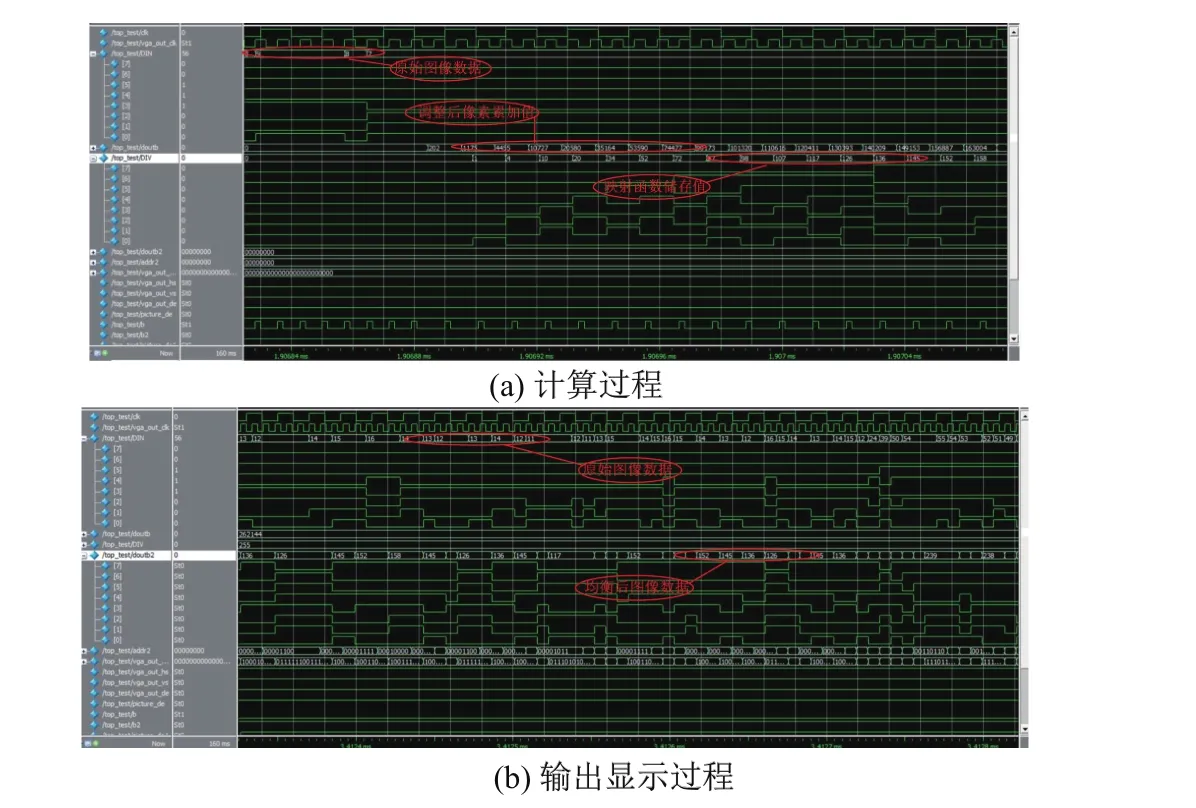

在ISE14.7下,采用Verilog进行硬件加速器的设计,其仿真波形如图11所示,图中(a)为算法处理的部分计算过程,(b)为算法处理后的部分结果数据.

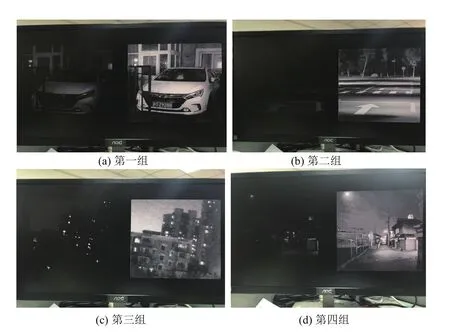

将结束仿真实验的逻辑功能正确的硬件加速器设计文件,通过USB Cable下载器烧录到FPGA里面.在针对测试集的图像进行测试时,选出其中4组典型的夜间低照度图像进行分析.为了方便查看处理效果,实验中将处理前后的图像同时显示在显示器上(见图12),每组实验结果均是左图为原始图像,右图为经过本工作设计硬件加速器增强之后的图像.每幅原始图像大小为512×512(像素),显示器分辨率为1 280×720(像素),未填充图像的显示器区域设置为黑色.第一组实验结果中原始图像仅能分辨出汽车轮廓和窗户轮廓,而处理后的图像车牌、铁门、墙面、窗户都非常清晰.在第二、三、四组实验结果中,原始图像都是仅有模糊的实物轮廓,几乎被黑暗完全淹没,难以分辨图像内容,而处理后的图像能明显看出路面上的斑马线和路标、楼房的天台和窗户、河边的房子和桥.这表明,增强之后的图像亮度和对比度都有了明显的提升,图像细节也保存得相当完好,噪声和过度增强现象得到了较大的抑制,产生了更好更清晰的图像.

图11 基于ModelSim的算法仿真Fig.11 ModelSim-based algorithm simulation

图12 基于FPGA的硬件加速器实验结果Fig.12 Test result of hardware accelerator based on FPGA

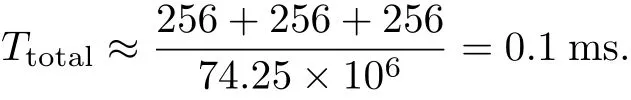

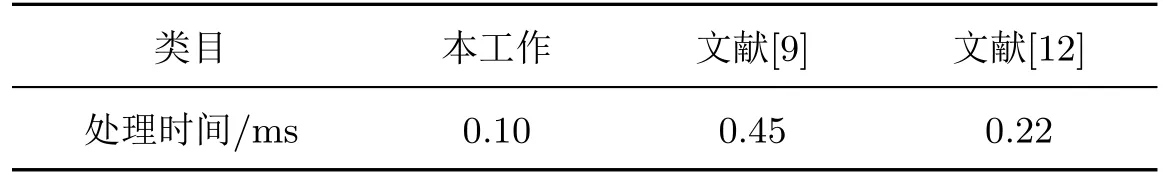

另外,在进行实时图像处理时,由于视频图像是连续的,故相邻图像具有很强的相似性.可以用上一帧统计的数据处理下一帧图像,这样既能满足实时性的要求,又能达到较好的增强效果.当一帧图像来临时,首先在对其进行统计的同时对其进行映射,映射关系来自上一帧图像,映射和统计同时完成;之后处理统计的结果形成下一帧的映射关系.至此,图像处理时间为原始直方图提取非零分量、计算增量V以及灰度级计算所用的时间,分别表示为T1,T2,T3,统计和缓存不再占用处理时间.处理时间可以表示为

由于直方图灰度级为256,提取非零分量时需要256个时钟周期,故T1约为256个时钟周期;计算增量V时需要对每个灰度级对应的像素点个数进行减法操作,需要256个时钟周期,故T2约为256个时钟周期;在映射函数值计算时需要对256个统计数值进行操作,也即需要256个时钟周期,故T3约为256个时钟周期.本实验使用的时钟频率为74.25 MHz,图像处理时间约为

表2统计了不同算法在硬件上实现的处理时间,其中本算法低于文献[9]中的多子直方图算法和文献[12]中的直方图均衡化算法,可见本工作设计的硬件加速器具有较好的性能.

表2 不同算法硬件处理时间Table 2 Hardware processing time of different algorithms

4 结束语

本工作设计了一种用于自适应直方图均衡算法的硬件加速器,平衡了算法性能和硬件实现之间的矛盾.首先,该加速器改进了自适应直方图均衡算法,使之能够利用自适应阈值有效限制对比度拉伸,克服了过度增强、噪声放大、丢失细节等缺点,且优化算法使之易于在硬件平台上实现;其次,该硬件加速器在FPGA硬件平台进行了测试,能够产生更好、更清晰的图像,达到了预期的增强效果,验证了其实用性和正确性.