一种级联型小数分频调制电路的设计实现

2020-06-11曾启明

曾启明

(深圳职业技术学院 广东省深圳市 518060)

1 引言

频率合成电路是射频通信芯片的关键部件,随着通信速率的提高,特别是5G应用背景下,频率合成电路的性能直接影响整个芯片的技术指标[1]。锁相环(Phase Locked Loop,PLL)是一种广泛应用于射频通信芯片的频率合成电路,其原理是利用参考时钟,间接通过锁相环路将输出信号的频率锁定在某一频率[2]。利用环路良好的窄带跟踪性能,PLL可以很好地选择所需频率的信号,抑制杂散分量,并且避免了大量滤波器,有利于集成化和小型化[3]。

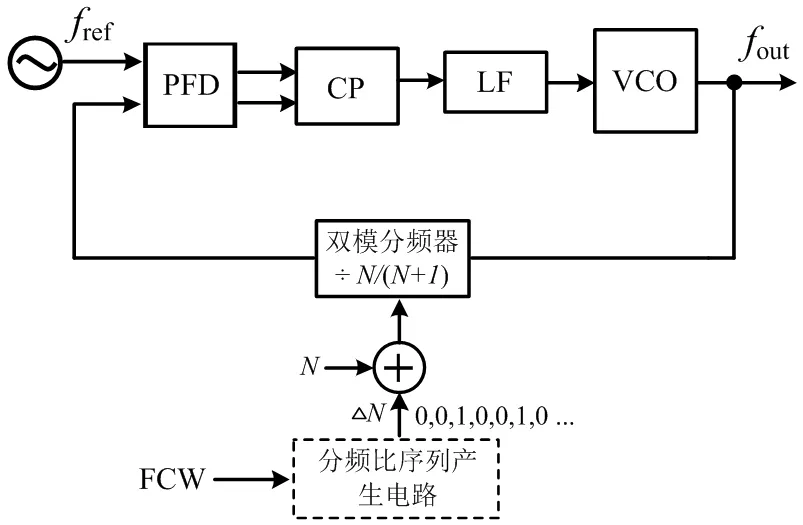

图1为基于双模分频器的小数分频锁相环电路结构,其主要部件包括参考信号源(fref)、鉴相器(Phase Frequency Detector,PFD)、电荷泵(Charge Pump,CP)、环路滤波器(Loop Filter,LF)、压控振荡器(Voltage-Controlled Oscillator,VCO)和分频器等。分频比序列产生电路根据频率控制字(Frequency Control Word,FCW),按照一定的工作频率输出包含小数信息的整数序列,并与N相加作为分频器的瞬时分频比,使其在{N,N+1}之间变化,从而在时间平均上实现所需要小数分频比。

当环路锁定时,VCO输出fout与外部参考时钟fref的关系可表示为:

其中,ΔN为包含小数分频信息的整数序列。根据公式(1)可知,小数分频锁相环能够以小于参考信号频率的步进输出信号频率,使分辨率不再受到参考频率的限制。

FCW的产生是实现小数分频的关键。因为分频比的变化,锁相环的实际输出频率也在不断变化。这种对分频比的调制如果是周期性,则必然产生杂散;如果是非周期的,则体现为相位噪声的恶化[4-5]。因此,产生FCW的调制电路除了能够将一个介于0和1之间的小数输入转化为离散的整数序列之外,还必须具备噪声整形特性。

2 调制电路的数学模型

图2(a)是一阶调制电路的结构框图,调制器在输入端对过采样时域离散信号和反馈信号之差进行积分。在实际电路实现中,积分器一般使用相位累加器实现,如图2(b)所示。图中,M为累加器的模(M=2n,n为累加器字长)。C为累加器溢出值,R为累加器余数。

图1:小数分频锁相环的结构框图

图2:一阶调制电路及相位累加器

上述一阶调制电路的差分方程可表示为:

因此,一阶相位累加器可以作为一阶调制电路的实现基本单元,并通过级联,实现高阶调制电路。

表1:不同分频比下调制电路输出结果分析

图3:三阶级联型调制电路

图4:调制电路的VCX仿真结果

3 三阶级联型调制电路

通过优化设计,本文实现的三阶级联型调制电路结构如图3所示。图中累加器字长为15位,首级累加器的一端输入对应调制器的输入x[n],调制电路工作时,x[n]=A为常数。累加结果作为量化误差延迟一个时钟周期后作为另一端输入再与A相加。累加器的溢出值对应调制器的输出y[n],若当前累加结果大于其模M时,溢出值为1,否则为0。因此,当输入为常数A时,累加器在M个fdiv周期内将溢出A次,溢出值在时间平均上等于小数分频比A/M。

在分频器输出fdiv的每一个上升沿,首级累加器对A进行累加,累加结果延时一个时钟周期后赋给下一级累加器继续累加。各级累加器的溢出位在噪声整形电路中合并为3位二进制补码输出,即{000,001,010,011,100,101,110,111},因此ΔN对应十进制范围为{-3,-2,-1,0,1,2,3,4}。整数分频比B的宽度为5位,其范围为{0,+1,+2,…,+29,+30,+31}。Δ-Σ调制器的3位输出与5位整数分频比相加后作为环路中多模分频器的5位模控制信号DIV_OUT。

图5:5.8GHz小数分频锁相环芯片版图

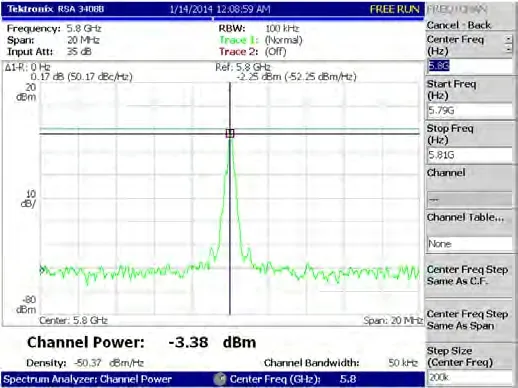

图6:目标频率为5.8GHz时锁相环的输出频谱

4 仿真及测试结果

仿真实验中,调制器电路使用Verilog HDL语言建模,并基于台积电 0.18μm CMOS标准数字流程实现。仿真结果使用Synopsys VCX仿真工具进行分析。仿真中整数分频比设为24,而小数分频比则按照0.05的步长设置为0.1至0.95之间的值进行多次仿真,以综合评估调制电路输出分频序列的准确性。

第一次仿真,设置小数分频比为24.75,仿真结果如图4所示。根据仿真结果,调制电路的输出能够按照设计要求输出正确的分频序列,第10000个统计周期时DIV_OUT的累加值为247500,即调制器在10000个周期内实现的平均分频比为24.75。

表1给出了将小数分频比设为0.1-0.95时,调制电路在10000个时钟周期内的实际分频输出结果。根据实验结果可以看出,调制电路能够按照设计要求输出正确的分频序列,平均误差仅为0.4%。

本文所设计的调制电路已应用于5.8GHz小数分频锁相环芯片,实物版图如图5所示。

测试实验中,令锁相环的输出频率为5.8GHz,即分频比为45.3125,使用Tektronix RSA3408B频谱分析仪进行输出频谱的测量,结果如图6所示。输出频谱的测试结果说明,锁相环能够准确地振荡在5.8GHz的设计频点,频谱两边的裙带及杂散能够得到很好的抑制。锁相环在偏移5.8GHz中心频率1MHz处的相噪声-109dBc/Hz。

5 结论

频率合成电路的性能直接影响射频通信芯片的整体指标,本文在GHz量级的高速应用背景下,设计实现了一个基于累加器的三阶级联型调制电路,并应用于5.8GHz小数锁相环。调制电路可以采用全数字形式实现,有利于低功耗和微型化。仿真及测试结果表明,调制电路能够按照设计要求输出准确的频率控制字,10000个时钟周期小数分频区间[0.1,0.95]内的平均误差仅为0.4%。经流片测试,基于该调制电路的5.8GHz相环路芯片能够准确锁定目标频率,满足设计要求。