基于UVM的FPGA数字下变频模块级验证方法的实现

2020-06-08吴迪飞

吴迪飞

摘要:为了解决使用FPGA开发数字下变频(Digital Down Conversion,DDC)模块的验证需求,提出并实现了一种基于UVM(universalVerificationMetodology,通用验证方法学)的验证平台。该验证平台以数字下变频模块为验证对象,以UVM提供的基类验证组件为架构搭建而成,通过c函数模型的调用,串行参数的解析等方式发送不同类型的激励数据至DDC模块;同时,验证平台自动采集经频谱搬移和滤波处理的基带IQ数据,在与参考模型进行对比后自动将正确的数据导出并写入文件进行频谱分析。在验证过程中对UVM特性机制的大量运用在保证测试效率的同时提高了可重用度。

关键词:数字下变频;通用验证方法学;测试平台;仿真验证;可重用

中图分类号:TN713;TN95 文献标识码:A

文章编号:1009-3044(2020)10-0269-04

1背景

现代雷达系统中广泛运用FPGA进行实时数据处理。在雷达接收回波信号的中频处理阶段,通过数字下变频的手段可以在保留有效信息的同时减小数据率,降低对后端器件的性能要求,是各型雷达系统的关键技术组成。基于FPGA实现的数字下变频模块,具有设计规模较大,功能复杂的自身特点,在使用传统验证平台对其进行调试验证时,因平台结构过于单一且无特定激励产生机制,造成测试激励范围有限、功能覆盖率低、代码的可重用性差等各类缺陷;在变更参数设定而需要更改测试用例时,往往导致代码量和用时成倍增加,容易造成验证不全面,效率低下,错误定位不准确等各类问题,这些因素都会对后期系统联试带来极大影响。

为应对同类大规模数字逻辑设计的验证需求,由Accellera在继承VMM,OVM的基础上推出了UVM,并得到了各大EDA厂商的支持。与传统RTL(寄存器传输级)验证平台相比,UVM基于面向对象的硬件描述语言SystemVerilog,兼具封装、继承等面向对象语言的特点和约束、功能覆盖率等验证独有的特性,拥有大量的库函数和基类,这些类库提供了通用的程序,如层次组件结构,传输级模型(TLM),以及配置数据库(uVM_config_db)等,这使得验证平台可以根据实际需求灵活地搭建结构。同时,平台能够提供定向触发和随机触发的组合激励模式,自动化进行DUT(Design Under Test,待测设计)的验证,并能对测试结果进行收集比对,有效提高了验证覆盖率,实现错误快速定位。

本文以雷达系统中的数字下变频模块为例,以UVM为架构,搭建了完整的可重用功能验证平台,针对提取的功能点通过构造受约束的随机测试激励,对模块进行了充分高效的验证,并对覆盖率进行了分析。

2验证对象和UVM

2.1数字下变频原理概述

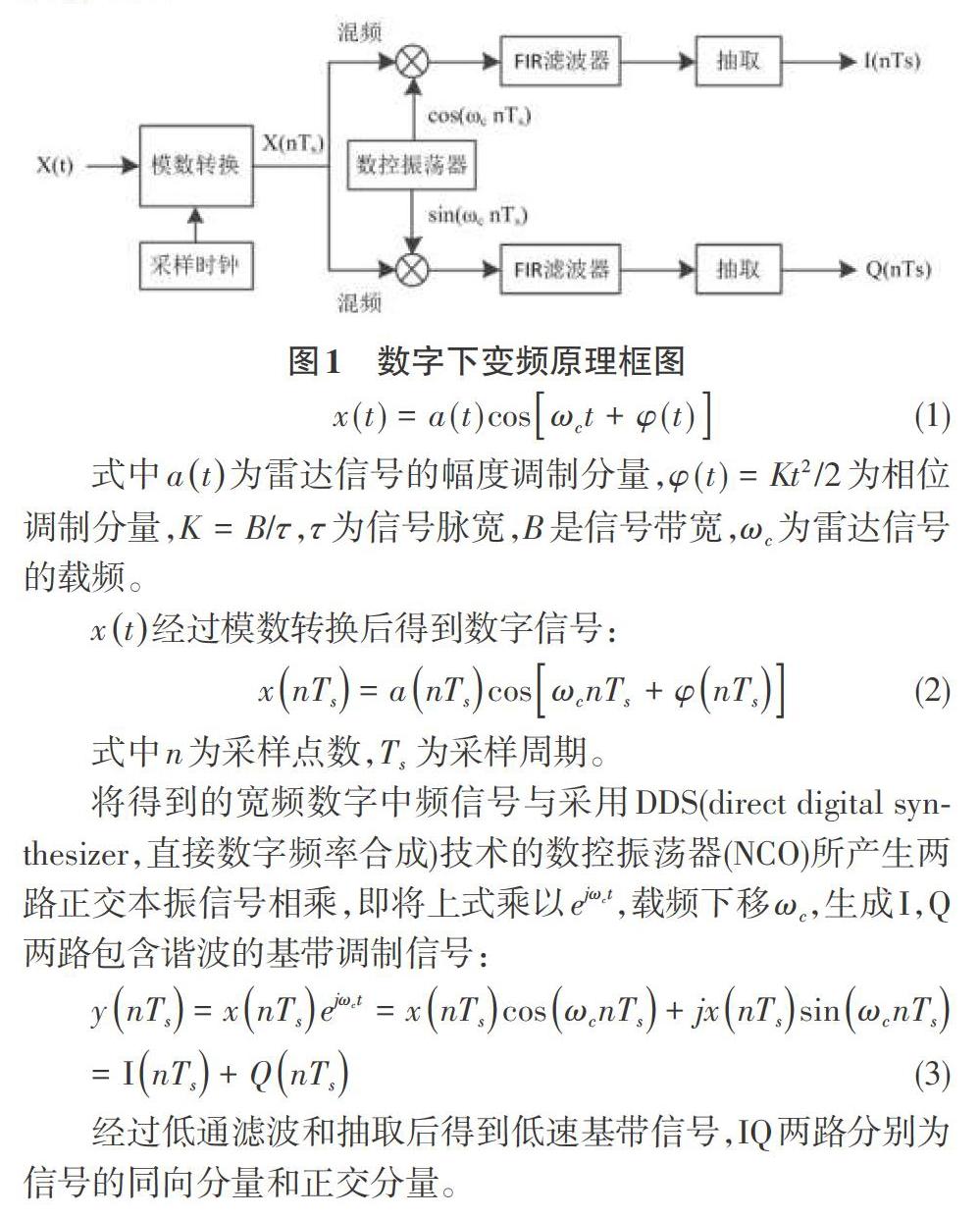

在相控阵雷达的接收前端一般需要进行数字下变频,将一定范围带宽的雷达回波中频信号频谱搬移至基带,从中提取所需要的窄带信号,在保留有效信息的同时减少采样点数,进一步降低数据采样速率,因此信号的数据率和带宽是功能验证的主要指标。数字下变频的基本原理如图1所示,对一个雷达回波信号有:

经过低通滤波和抽取后得到低速基带信号,IQ两路分别为信号的同向分量和正交分量。

2.2 UVM验证平台

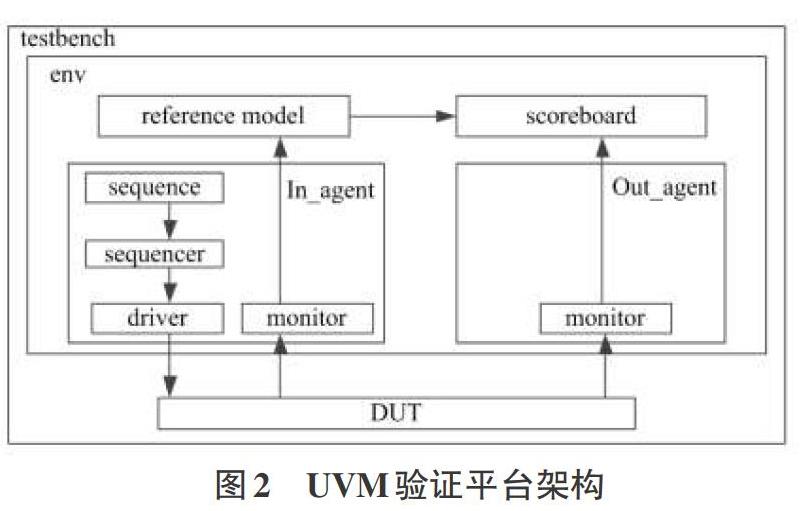

UVM验证平台由一些可重用的验证组件通过一定的层级结构组成,每个组件都由基类派生得到,拥有特定的功能,能够实现数据与协议的解耦,保证了平台能够自动化执行。由于采用了层次化的验证结构,平台经过顶层配置即可以遍历的方式自动调用各验证组件,实现了各个组件的自由组合,大大提高了可重用性。一个典型和最基本的UVM平台架构如图2所示,包含了代理组件(agent)和环境组件(env)两个基本类。在环境组件中集成了一个或多个代理组件,参考模型和记分板。每个代理组件中封装了定序器(Sequencer),序列发生器(se-quence),驱动器fDriverl和监视器(Monitor)。在验证平台运行后,In_agent中的定序器从序列發生器接收产生的TLM激励数据,然后将其发送到代理的驱动器上,驱动器将激励的数值赋到相应的接口信号中以驱动DUT的输人,In_agent中的监视器将这些输入信号同步发送至参考模型,Out_agent中的监视器接收经DUT产生的输出信号,记分板比对参考模型和DUT两者的输出得到验证结果。

3验证平台实现方法

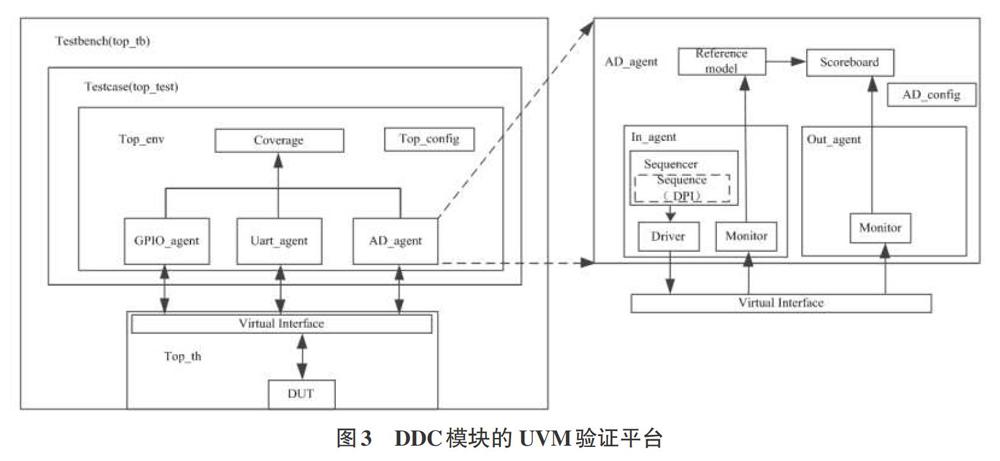

基于UVM验证方法学,结合数字下变频系统特点搭建的模块级验证平台包含了测试项,验证环境和测试序列三个方面,其总体结构如图3所示。对DDC模块的功能特性进行验证,需要搭建完整的验证环境并产生受约束的随机激励,同时对结果进行校验。

3.1测试项编写

整个验证平台的搭建按照自顶向下的顺序进行。在验证平台的顶层(top- tb)实例化整个DDC模块作为DUT,同时用Sys-temVerilog的run_test函数创建一个UVM测试类ftop_tesI),这个测试类中包含了UVM顶层验证环境(Top_env)和所有的验证组件并使之运行。通过关键词Interface定义一组虚拟接口(Vim-al Interface)来连接基于类的UVM验证环境与基于RTL模型的DUT。使用UVM配置数据库方法使得虚拟接口在整个验证环境可用。一个测试类的核心部分包括如下组件:序列发生器,驱动器,监视器,验证环境,代理,记分板,参考模型,覆盖率收集器。

3.2验证环境搭建

UVM验证环境在测试类中创建,验证环境是一个自定义类,从uvm_env基类扩展得到,包含了一个配置组件(Config),一个覆盖率收集器(Coverage),一个记分板(Scoreboard)及若干代理(AgenI)。代理组件派生自uvm_agent基类,每个代理与DUT中的一类I/O管脚连接并使用对应的接口协议。根据数字下变频功能模块的特性,DUT与验证平台进行数据交互主要有以下三类接口信号,需要设置三个代理:

1)DDS需要依据同步串口解析出的频率调谐字,频率步进调谐字,相位调谐字和脉宽码等波形参数,产生不同频率、脉宽的本振波形信号,建立同步串口代理组件;

2)对采集的雷达中频回波信号进行模数转换,并产生基带IQ调制信号,建立AD代理组件;

3)模块需要的时钟复位及导前等控制信号,建立通用输入输出接口fGPIO)代理组件;

验证平台的参数配置在顶层完成,该平台的配置组件通过uvm_object基类创建得到,对相应代理中是否对功能覆盖率进行收集,是否为主动代理等配置参数进行设定并添加所有输入输出变量的实际位宽。利用UVM配置数据库(uVM_coiffig_db)这一机制将全部配置信息纳入UVM配置数据库中,底层代理组件将从库中获取顶层的配置信息,从而完成整个测试环境的配置。

本设计中所有的代理组件为设置为主动模式,即在每个代理组件划分为输入代理和输出代理两个部分,在每个代理中使用监视器组件分别对DUT的输入和输出进行监测,该组件扩展自uvm_monitor基类。在每个采样时钟的上升沿对数字下变频各子模块输出信号和经滤波抽样的基带IQ信号进行采集,并将得到的数据保存为UVM变量发送至记分板和覆盖率收集器。

在测试环境中各代理通过监视器建立与功能覆盖率收集器的连接。在本设计中,功能覆盖率收集器要求对输入信号完全覆盖,在覆盖组中指定整个DUT实例为采样对象,覆盖点包括了AD采样后的数字信号和最后输出的基带10信号。平台通过调用UVM的Write函数从监视器中拷贝序列项句柄,并通过Sample函数统计信号端口的区间遍历信息,检测在每个区间上被击中的情况。

验证平台记分板的主要功能是验证DUT的实际输出是否和预期一致。组件中包含了一个Matlab语言编写的完整算法作为DDC模块的参考模型,采用与发送至DUT完全相同的输入信号作为激励,通过监视器监视DUT输出的方法将实际结果和预测结果进行比对来判断相关功能是否实现。

3.3测试序列执行

在UVM中,序列项对象(sequence_item)是最基本的通信单元,用来定义UVM环境内部变量及随机化约束,它通过继承uvm_sequence_item基類得到。在本设计的不同代理组件中有不同定义,串口代理中规定了串行数据帧长及传输字节间延时,在GPIO接口代理中为系统导前和复位信号,在AD接口代理中为数字化的AD信号和IQ数据。

验证平台的核心是要根据设计的测试用例产生一系列的随机测试序列。这由UVM中的序列发生器组件完成,它派生自uvm_sequenee基类,根据设定的变量约束产生所有的测试激励。在各代理组件中分别产生不同的序列,将这些序列组合后按照一定顺序将随机化后的序列项对象的值传递至驱动器。在AD接口代理中,根据设定的采样频率,采样点数,中心频率,信号带宽转换成对应窄带回波信号的脉冲宽度,频率变换率等参数,并进一步计算出信号对应的复数表达式并进行截位,同时进行模数转换。作为测试激励数据的AD采样信号为宽带高速数据流,具有高位宽,高深度,高数据率的特点,通过在序列发生器中声明DPI接口调用C函数模型完成这一过程。在GPIO的序列发生器中产生负脉冲宽度为lus的导前和复位信号。在串口序列发生器中根据数据字典生成15MHZ带宽的载频信号作为本振进行频谱搬移。

在本验证环境中用从uvm_sequencer基类扩展得到的定序器作为序列项路由。每个代理的定序器从序列发生器处接收序列,然后将其发送到对应的驱动器上。在定序器中定义序列项的类型后可以对同一代理添加多个序列,并指定需要发送的序列。每个代理组件的序列发生器设置一个默认执行序列de-fault_sequence,同时在测试类中设定并启动一个虚拟序列,该序列将不同代理的默认序列进行组合并负责调度协调执行,并在顶层调用UVM的工厂机制对测试序列进行重载,选择在序列发生器中所用的序列。

驱动器派生自uvm_driver基类,按照一定的时序关系将序列项转化为端口信号。当驱动器获得序列项的时候,为了配合转换驱动的值到接口变量需要和序列发生器,DUT两者进行同步,同步过程通过数据阻塞传输机制完成。验证环境在顶层以start方式启动虚拟序列后,序列发生器在虚拟序列中包含的子序列会在对应的定序器上执行,每个代理的序列发生器在实例化序列项对象后使用body函数调用start_item语句,start_item阻塞直到驱动器请求一个序列项,在uvm_driver基类中有一个内建端口seq_item_port,包含了get_next_item和item_done一对系统函数,驱动器调用seq_item_port.get_next_item请求一个序列项,然后驱动器阻塞直到收到一个序列项。在每个数据采集时钟的上升沿,驱动器将序列项的值赋给接口变量,然后调用seq_item_port_item_done解锁序列发生器,反馈握手信号,说明一次传递结束,执行finish_item任务,body函数退出,解锁测试的start,表明一个测试用例已完成。

4结果与分析

对于已搭建的测试平台,不同接口设定多个不同的测试用例对功能进行验证。在120MHz波形采集时钟和数据采集时钟下,串行接口按照串行协议发送帧数据,根据解析出的各波形参数生成本振载波;AD接口代理发送70MHz带宽的雷达窄带回波信号,通过C语言的文件处理函数fwrite将数字化的正交基带IQ调制信号记录并保存在文本文件中,在对其归一化处理后倒入matlab进行频谱分析,可以得到如图4所示的经抽取滤波后IQ信号频率和幅度分布,其信噪比SNR、无杂散动态范围SFDR等信号指标均在正常范围。

在接收AD代理发送的数字信号序列时,经过数字下变频处理的基带信号仿真波形如图5所示,其中CHl组代表经数字下变频DUT输出的数据,CH2组为通过Matlab参考模型输出得到的数据。FLAG_IQ为IQ信号采样标志位,高电平代表有效数据,低电平为重复数据,I_SP、Q_SP是滤波抽取后得到的信号同向分量和正交分量,由光标测算可以得到每经过100008ps对信号进行一次抽样,数据率约为10msps,满足系统要求。经对比,两组信号的数值和时序完全一致,这说明数字下变频模块的功能已经基本实现㈣。

针对UVM的功能覆盖率,本验证环境提供了较为直接准确的方式。如图6所示,验证平台对实例化的工程各单元输入和输出信号区间进行了采集,其功能覆盖率达到了100%。对于传统验证平台,由于并没有特定的方法对功能覆盖率进行统计,很难得到功能覆盖率的具体数据。

5结束语

本文基于雷达系统中数字下变频模块的验证需求,以UVM验证方法学为基本架构,借助SystemVerilog语言特性和UVM提供的相关内建功能,选择合理的配置机制,提出了一个分层结构的验证平台设计方案。该方案建立起的验证平台具备良好的灵活性、重用性和易维护性,测试团队采用此统一架构可有效提高测试效率。最后,通过设计不同类型的测试用例,高效地进行了100%的功能覆盖率测试,实现了全面验证。