一种Flash 安全存储控制器的设计与实现*

2020-06-08何卫国黄金金李雨励饶金涛

何卫国,黄金金,李 军,李雨励,饶金涛

(成都三零嘉微电子有限公司,四川 成都 610041)

0 引 言

目前,嵌入式系统中广泛使用Flash 存储器存储系统启动引导文件等重要数据[1]。Flash 存储器具有不易失、功耗低、可靠性好以及容量大等优势,但很容易受到攻击被窃取敏感信息或被恶意篡改,如冷启动攻击和侧信道攻击等,造成系统的安全可靠性降低,关键信息泄露。因此,如何有效应对外部的安全攻击至关重要。

在软件层面,文献[2]基于JFFS2 设计了符合Flash 物理特性的加密文件系统,完成数据的加密任务。常用的加密文件系统包括CFS、EFS 等,都工作在Linux 平台或Windows 平台,而不是针对嵌入式系统设计。如果直接移植到嵌入式系统,会大大降低嵌入式系统的性能。根据NAND Flash 的物理特性,该文基于JFFS2 设计了一种EJFFS 加密文件系统,在确保数据安全的同时,保证NAND Flash的读写速率。

在硬件层面,文献[3]使用CPLD 实现了Flash存储器的加密,在处理器和Flash 总线之间串联了一块CPLD,对Flash 地址、数据进行处理。CPLD是可编程器件,非常适合完成各类算法和组合逻辑,通过在线编程功能可以灵活使用不同算法。文献[4]在嵌入式系统存储器数据加密技术的基础上,提出了一种地址加扰安全防护措施,通过使用比特置换网络实现地址加扰,保证了地址加扰的实时性。由于处理器的初始化代码与处理器型号相关,特定型号的处理器其初始化代码相对固定,因此很容易被攻击者探知。通过对系统初始化过程中写入存储器的地址进行加扰,可以有效保护系统程序的安全。文献[5]使用AES-GCM 实现加密算法和数据完整性算法,建立了一种片外访存加密认证机制,将存储器划分为1 kB 大小的页面,每个页面生成一个128 bit 的认证码。嵌入式系统读取外部存储器时,会将读出密文生成的认证码与保存的认证码对比,如果不一致,说明数据被篡改。还有一些文献使用其他的加密算法如LBlock、KLEIN 等实现安全存储[6-7]。AMD 为了抵御冷启动、Bus Snooping 等攻击,也提出了硬件内存加密机制SME 与SEV[8],基于原有的内存控制器,将密钥放在内存控制器上,对内存进行写操作、读操作时,内存控制器对数据进行加解密。

本文设计实现了一种Flash 安全存储控制器,以数据加密和混乱地址映射来防止攻击者从存储器入手攻击关键信息,并对Flash 存储器进行分区,通过认证机制控制用户访问Flash 存储器。

1 控制器结构

1.1 总体结构

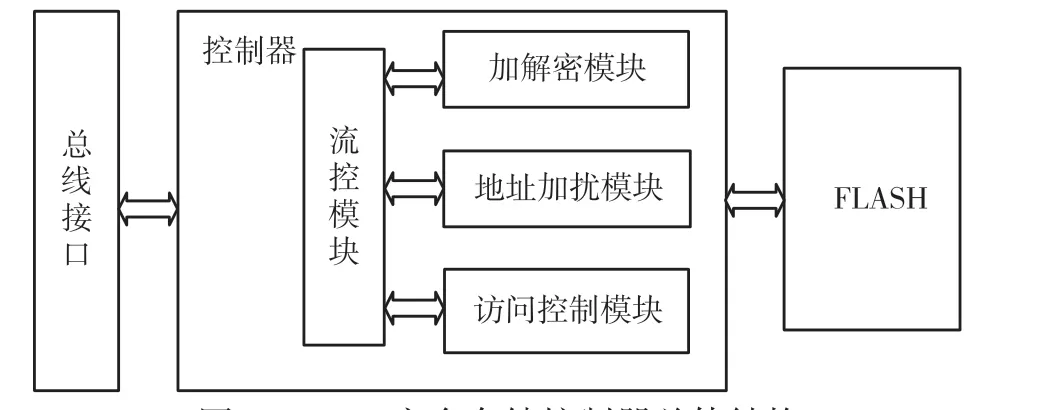

图1 为Flash 安全存储控制器的总体结构,主要包括流控模块、加解密模块、地址加扰模块及访问控制模块。

各个模块的功能如下。

(1)流控模块:接收总线信号,判断操作区域的访问权限,完成数据在各个模块之间的流动 控制。

(2)加解密模块:对Flash 中的存储数据提供加密服务,保证Flash 存储数据的保密性。这样即使攻击者读取Flash 存储器的内容,在没有密钥的情况下也无法获取存储数据的信息。

(3)地址加扰模块:对读、写操作的地址进行加扰,混乱数据的存储位置,进一步提升存储数据的保密性。

(4)访问控制模块:对Flash 存储器进行分区,控制不同等级用户的访问范围;对Flash 中的受保护区域实行认证保护机制,用户只有认证通过才能对受保护区域进行读、写操作。

图1 Flash 安全存储控制器总体结构

1.2 数据安全存储

为了保证Flash 的访问速率,本文的加解密模块由国密SM4 算法实现。SM4 算法是一种分组算法,加解密速度快且逻辑简单较易实现,非常适合作为Flash 存储数据的加解密算法。SM4 的运算流程是先输入密钥进行密钥扩展,后输入数据进行加解密处理。本文在一次密钥扩展后会将扩展结果保存,后续如果密钥不更换则不需要密钥扩展过程。这样可以将SM4 运算时间缩短一半,进一步提升Flash的访问速率。

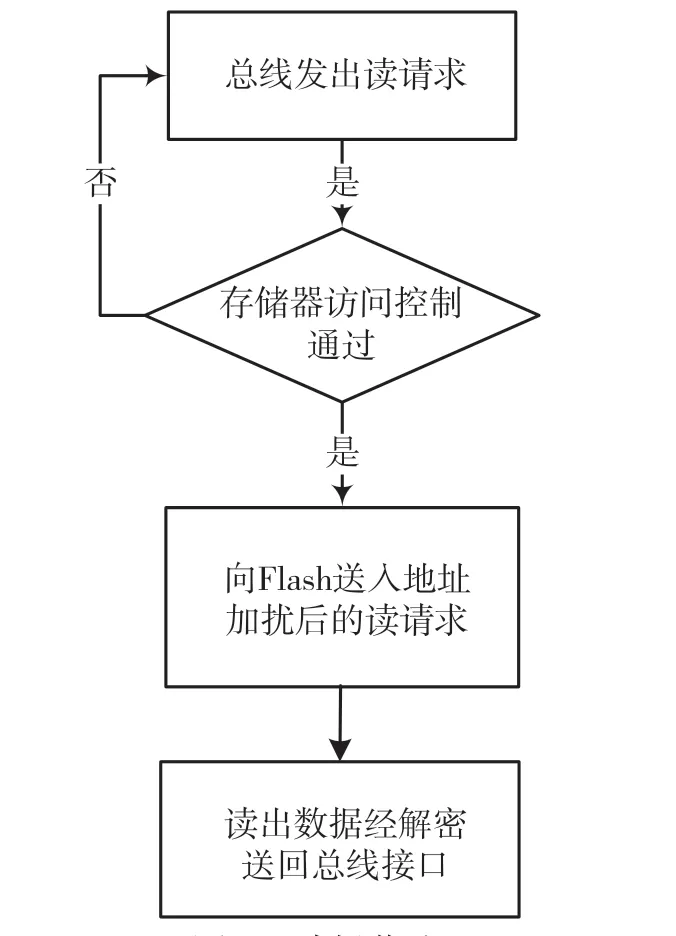

读、写操作流程分别如图2、图3 所示。

图2 写操作流程

图3 读操作流程

当流控模块识别到总线发出写操作时,首先判断写操作地址所在区域是否开放访问权限,如果开放,将写地址送入地址加扰模块,将写数据送入加解密模块进行加密,之后将处理好的地址和数据按照Flash 接口协议送入Flash 存储器。当流控模块识别到总线发出读操作,也要首先判断读操作地址所在区域是否具有访问权限。如果有,则将加扰后的地址送入Flash 存储器,等待Flash 发出读回的数据,然后将数据送入加解密模块进行解密,再送回总线接口。

1.3 分区访问控制

在一些应用场景中,Flash 中存储的数据具有不同的密级。不同等级的用户可访问的数据范围不同。为了实现不同等级用户的访问控制,本文在Flash 控制器中加入了分区访问控制逻辑。将Flash存储器空间划分为多个区域,并将用户分成两级,包括普通用户和管理员用户。普通用户针对某一区域进行认证,如果认证通过,则获得该区域的访问权限。管理员用户通过认证,则获得所有区域的访问权限。

如图4 所示,Flash 空间被划分为认证数据区和多个主存储区。认证数据区用来保存所有主存储区的相关信息,包括认证值、当前错误认证的次数、被允许的错误认证次数等。如果普通用户针对某一区域的错误认证次数超过被允许的错误认证次数,则该区域的访问权限会被锁死,用户无法再通过认证获得访问权限,需要通过管理员认证来解锁。如果管理员用户的错误认证次数超过被允许的错误认证次数,则全片锁死。

图4 Flash 分区

普通用户的认证过程描述如下。

(1)用户发出口令后,首先判断当前错误认证的次数是否超过被允许的错误认证次数,如果不超过则进入流程(2),如果超过则当前区域的访问权限锁死,用户无法操作当前区域;

(2)将用户口令与认证值进行比较,如果完全一致,则获得当前区域的访问权限,如果不一致则进入流程(3);

(3)错误认证的次数增加,获取当前区域的访问权限失败。

首次认证时,用户使用设定好的认证初始值作为口令进行认证。认证成功后,用户可以将认证初始值改成仅用户知晓的值,从而有效保护用户的数据安全。

2 测试结果与分析

2.1 测试环境

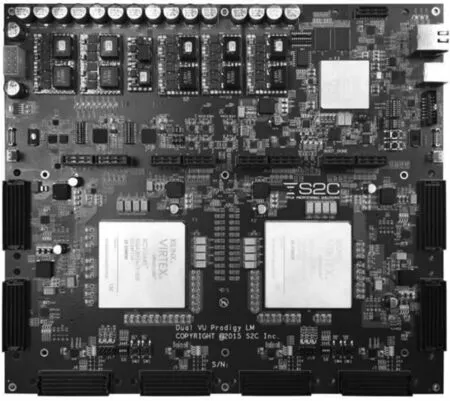

测试环境基于某嵌入式SoC 芯片原型系统,模拟用户的认证流程和对Flash 的读写流程来验证Flash 安全存储控制器的功能。实验环境如图5 所示。

2.2 实测结果

(1)未认证情况下向主存储区发送写请求,控制器拒接了此次写请求,数据未被写入Flash;向主存储区发送读请求,控制器拒接了此次读请求。

(2)认证失败后向主存储区发送写请求,控制器拒接了此次写请求,数据未被写入Flash;向主存储区发送读请求,控制器拒接了此次读请求。

(3)认证成功后向主存储区发送写请求,控制器允许了此次写请求,密文数据被写入Flash,且写入地址为加扰后地址;向主存储区发送读请求,控制器允许了此次读请求,读出数据为正确的明文。

(4)认证失败超过限定次数后,管理员发送口令且认证成功,向主存储区发送写请求,控制器允许了此次写请求,密文数据被写入Flash,且写入地址为加扰后地址;向主存储区发送读请求,控制器允许了此次读请求,读出数据为正确的明文。

测试结果表明,Flash 安全存储控制器能够实现分区访问控制,且数据在Flash 存储区中以加扰加密状态存储。可以根据用户制定的用户策略设定部分主存储区不需认证即可访问,形成开放区和敏感区,使应用范围更加灵活。目前,本设计已经应用于实际产品中并流片完成,证明了本设计的可用性和实用性。

图5 实验环境

3 结 语

本文设计实现了一种Flash 安全存储控制器,在通用Flash 控制器工作原理的基础上添加加解密模块和加扰模块,将Flash 存储空间划分为多个分区,实现对不同等级用户的访问权限的控制,最后通过实际测试验证了控制器功能。该Flash 安全存储控制器完全由硬件实现,对Flash 访问速率影响相对较小,且访问过程安全可靠,提高了系统的安全防护能力,可在很多平台推广应用。