接口时序一致性连续定量监测技术研究

2020-06-06宫久路谌德荣

高 亮,宫久路,谌德荣

(北京理工大学 机电学院,北京 100081)

0 引言

在武器系统电气系统中,非标接口主要用于系统之间以及系统内部传递具有特殊传输要求的信息(如:指令)。非标接口往往由系统工程师设计时序或选用标准时序,产品工程师采用可编程电路实现时序,测试工程师利用示波器对时序进行抽样检测。武器电气系统工作环境复杂且条件恶劣,其应用环境存在多种引起时序变化的因素(如:温度的变化),电气系统需要在地面进行大量的环境适应性试验。如果在地面环境试验中对接口参数进行连续定量地监测,获取非标接口时序参数的分布特性,则可为非标接口时序参数的最优设计提供精确的数据支撑。

对接口时序的一致性分析主要采用仿真加抽样测试来完成[1]。对于标准接口,采用为示波器或逻辑分析仪配置协议插件实现对I2C、CAN等标准总线时序的自动测试和上层协议分析[2-3],典型产品有广州致远电子公司生产的ZDS4000系列示波器;对于非标接口,测试则依赖定制化系统[4-5],相关研究多集中于特定应用领域的系统设计[6-7]。时序监测系统的智能化、通用化是亟待解决的重要课题[8]。

本文通过建立时序参数模型,设计被测参数的图形化输入接口,以事件码序列为触发条件,设计Dynamic Event Warping-Boyer Moore (DEW-BM)算法从数据流中捕获目标时序,根据参数模型定位受约束信号沿位置,将信号沿之间的时间距离作为被测参数的测量值,通过验证时序参数是否满足约束不等式给出分析结果,实现对非标接口时序一致性的长期连续定量监测。

1 系统设计

接口时序一致性分析是指对信号波形的建立时间,保持时间等参数进行测量,并与规定的约束值对比,检查所有周期的波形是否符合协议标准。对比测试是时序一致性分析的常用方法,其主要测试流程如图1所示。

图1 对比测试基本流程图

本文基于虚拟逻辑分析仪结构设计时序监测的硬件系统,如图2所示;利用DSLogic逻辑分析仪模块实现接口信号数据采集及阈值比较,其性能参数如表1所示;通过USB总线接收数据流并以二进制文件存储到服务器硬盘。

图2 监测系统结构框图

表1 DSLogic性能参数表

名称最大采样率通道数输入电压范围/V参数值20M@1640M@816-30~30

基于B/S架构设计时序分析软件,如图3所示,通过读取数据文件和输入被测参数信息进行时序一致性检测,并在前端页面显示时序一致性分析结果。

图3 时序分析软件工作流程图

2 关键技术研究及设计

2.1 参数描述模型

对比测试的关键在于标准模式库的建立,传统上通过编写协议插件实现模式库的生成,缺乏接口时序统一的描述模型和输入接口,这是现有时序监测系统难以通用化的根本原因。建立时序描述模型,实现被测时序的输入接口,是解决时序监测系统通用化问题的可行方法。

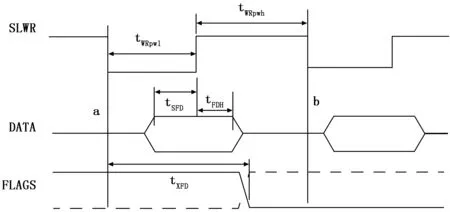

时序一致性分析中常见的测试项目有:建立时间、保持时间、电平持续时间等[9],在本质上这些参数都是描述两个信号沿之间的时间间隔。因此只需要知道被测参数的起始位置,终止位置和约束值三个参数便可以使计算机实现自动测量。时序参数的测量示意图如图4所示,对应地需要输入信号沿a,信号沿b和约束值Tsu的数值描述,其中Tsu直接由接口时序规定,具有明确的数值,而信号沿的位置则需要建立一种规则来准确描述,本文通过定义信号的沿函数,利用沿函数值来标识信号沿在时序周期中的位置。

图4 时序参数测量示意图

定义1:设有(0,1)域上的二元时间序列Xg:

Xg=[x(g)1x(g)2…x(g)n]

若存在整数p,使得x(g)p-1+x(g)p=1且x(g)p-1×x(g)p=0,则称Xg在p处有沿,若Xg在p1,p2,…,pN处有沿,且p1 (1) 按照上述定义,信号沿a的位置可描述为(A,4),信号沿b的位置可描述为(B,2)。为了实现自动对比还需要输入测试值与约束值的约束关系,分为最大值约束和最小值约束两类,因此Tsu可由参数模型表示为: (A4B2minTsu) (2) 被测参数均表示为形如式(2)的矢量模型,当需要输入多个参数时,即对应输入多个约束矢量。为了便于工程实现,本文设计基于csv文件的时序参数输入接口,其输入格式如图5所示。 图5 基于csv文件的时序参数输入格式 接口时序一般具有周期性,在上一个工作周期结束至下一个工作周期开始前存在无关时序,工作时序呈片段离散地分布于整个监测数据流中,因此筛选出目标时序片段是时序分析需解决的首要问题。其难点在于当接口时序发生错误时,目标时序片段可能不再符合触发条件,作为无关时序被过滤,导致时序错误未被发现。因此设计一种具有时序容错能力和高效的数据捕获方法,成为时序一致性分析正确性的保证。 传统上,逻辑分析仪通过设置边沿、码型等触发条件捕获目标信号[10],但捕获正确性低,需依赖人工滑动定位目标时序,无法直接应用于自动测量。目标信号捕获通过协议分析软件实现,其分析对象是已经被离散化后的布尔时间序列,因此码型触发是最优选择。在理想时序下只存在一种码型,但由于实际电路中的信号存在抖动,信号沿重叠处附近会产生额外的码字,如图6所示,01和10分别是b信号沿偏离理想位置时额外产生的码字。若同一有效沿处重叠信号沿数量为n,则产生的码字最多有n-1个,最少有0个,目标时序呈现出多模式的特征,模式集随并行信号数量的增加呈指数级增长。为了降低匹配的复杂度,提出事件码并以事件码序列作为触发条件,接口时序可用唯一的事件码序列表征,实现将多模式匹配简化为单模式匹配。 2.2.1 事件码 数字系统依靠信号间逻辑值的不同组合实现不同的逻辑事件,本文将理想时序下逻辑事件有效时各信号对应的逻辑值组合称为事件码。数字系统由时钟驱动,逻辑事件的有效时刻即对应着时钟信号的有效沿,以图4所示时序为例,若clk的下降沿为有效时刻,则A和B信号对应的事件码为(11 01 11 00 10 10 11 11 01 00 00 00),对连续相同的事件码合并得到事件码序列(11 01 11 00 10 11 01 00)。对于信号沿不重叠的时序,其信号抖动不会改变时序的事件码序列,如(A,5)和(B,3)信号沿偏离理想位置;当存在信号沿重叠时,如(A,3)和(B,1)发生偏移则会产生新的码字,当采样分辨率高于偏移距离时,这些码字就能被观测到。但是这些码字不具有实际的逻辑操作,因此不能认为是事件码,用扰动码符号*标识并说明重叠信号的数量,则图4时序的事件码序列表示为(11 01 11 *2 00 10 11 01 00)。当有n个信号沿重叠时,可最多插入n-1个完全不同的扰动码,信号抖动会造成信号沿在理想位置附近移动,但不会造成信号的二次翻转,所以扰动码不能与插入位置前后的事件码相同,即上述事件码序列中的*不能为(11)和(00),则事件码序列长度为: m≤l≤m+r-k (3) 式中,m表示事件码的数量,r表示在理想时序下重叠的信号沿数量之和,k表示有k个不同的时钟有效沿时刻发生重叠。 2.2.2 匹配算法 设被测接口时序有p个可测信号,采样频率为fsamp,采样时长为t,对各信号同步采样,则采样数据可表示为: (4) 数据序列的长度q=t×fsamp,将上述矩阵中同一列的数据点编为一个码元,由于采样频率一般是信号最大频率的数倍,相邻码元存在大量的重复性,游程压缩后可得到数值序列Dn和游程序列Tn: Dn[d1d2…dn] (5) Tn[t1t2…tn] (6) 式中,ti表示压缩前最后一个di对应的时刻,目标信号捕获即为从数据序列Dn中搜索与事件码序列Pl完全匹配的子序列,这是具有通配符的单模式串匹配问题,常见的串匹配算法有Brute-Force(BF),Knuth-Morris-Pratt(KMP)和Boyer-Morre(BM)算法等[11]。但由于事件码序列含有通配符*且长度不确定,因此无法直接应用上述算法。文献[12]指出BM算法在最坏情况下具有最好的计算复杂性,在最好情况下的计算复杂性优于KMP算法,因此本文以BM算法为基础,通过对事件进行动态弯折,设计信号的模糊匹配算法DEW-BM(Dynamic Event Warping-Boyer Morre),实现对目标信号捕获,详细算法步骤如下: 1)将事件序列P的首字符p1和数据序列D中的某一字符di对齐,称位置i为尝试位置。由式(3)可知最后一个事件码一定位于di+m-1到di+m+r-k-1之间,以di+m+r-k-1为起点,从右至左开始匹配第一个符合条件的字符,若存在字符di+s=pm且di+s在Tn对应的时间点ti+s不超过匹配阈值τ,则对齐di+s和pm;若不存在匹配字符,则对齐di+m-1和pm。 2)以pm为起点,从右向左匹配后缀,匹配时如果pi是通配符*,则按3)中的规则执行,直至出现p1=di或pk≠di+k-1(1≤k≤m-1),前者表示匹配成功;后者表示匹配失败并继续后续步骤,将D中首次出现的不匹配字符di+k-1称为坏字符,将已匹配成功的序列pk+1,pk+2,…,pm称为好后缀。 3)当pj=dj且pj-1=*number时(*为扰动码,number表示重叠数),若从dj-1到dj-number中存在字符dchar与pj-2匹配,则将dj至dchar之间的数据序列弯折与pj-1对齐;若不存在匹配字符,则将dj-1至dj-number的数据序列与pj-1对齐。上述两种情况对齐后,均表示pj-1匹配成功,继续匹配下一字符pj-2。 4)计算坏字符的移动距离shiftbc,在P中从右至左查找首次出现的坏字符di+k-1,以bmBc[char]表示坏字符在P中的位置序号,若P中不存在坏字符,则将P移动至坏字符的下一个字符,令bmBc[char]=-1;若存在一个或多个坏字符,则选取P中最右的那个字符移动至与坏字符对齐;综上shifbbc=k-1-bmBc[char]。 5)对P做扫描后缀匹配预处理,计算匹配度数组suffix,suffix[i]的值表示从pi开始向前扫描,能够与P后缀匹配的最大长度。 6)计算好后缀的移动距离shiftgs,以bmGs[char]表示子串后缀的最后一个字符在P中的位置序号,若P中存在与好后缀前导字不同的子串,则将最靠右边的字串对齐;若无符合条件的子串,则寻找P中的最长前缀使其与好后缀的后缀对齐;若上述两者都不满足,则直接移动P至坏字符的下一个字符,并令bmGs[char]=-1;上述匹配过程可通过步骤5)预处理完成,通过查询suffix数组可直接获取匹配结果,综上shiftgs=m-bmGs[char]。 7)选取shiftbc和shiftgs中的较大值作为下一次匹配的移动距离,跳转步骤1),执行下一次匹配。 算法流程如图7所示,右对齐位置的确定和通配符匹配规则设计是DEW-BM算法的动态弯折实现,主要用于解决传统BM算法应用时面临的两个问题:1)模式序列和目标数据序列的长度不一致;2)缺少通配符的匹配法则。 图7 DEW-BM算法流程图 当时序参数不满足接口时序所规定的约束值时称为异常时序,时序一致性分析的过程就是从捕获的信号数据中测量出各个时序参数的实际值,再与约束值进行比较。 2.3.1 时序参数测量 时序参数具有形如式(2)的描述,参数测量具有独立性,因此对于n个参数的测量可划分为n个并行的测量过程。设捕获的数据可描述为形如式(4)的数据矩阵,以式(2)所描述的参数为例,说明测量过程,设信号A由通道1测试,信号B由通道2测试,则有: 1)对d(1)行向量计算沿函数,初始化当前沿函数值index=0,若d(1)i与d(1)i+1的值不相同,则index=index+1,当index=4时,读取此时若d(1)i对应的若ti,记作tA;同理,读取B信号沿对应的时间值tB。 2)若约束关系为min,则判断|tA-tB|≥Tsu;若约束关系为max,则判断|tA-tB|≤Tsu。 3)若存在时序参数不满足约束不等式,则判定当前捕获数据存在异常时序,并记录异常时序的时间位置。 4)分别独立统计各测量参数的最大值和最小值,并在每次时序分析完成后更新。 2.3.2 测量误差分析 (7) max约束关系下的时序正确状态修正为: (8) min约束关系下的时序正确状态修正为: (9) 时序一致性分析系统的核心在于时序分析软件功能的正确实现,为了验证时序分析软件的分析结果具备一定的正确性和可靠性,基于信号完整性的分析,利用matlab模拟生成某FIFO的异步写入时序在各种噪声环境下的信源采样数据,时序关系如图8中的a至b段所示,时序约束如图9所示。时序分析软件通过读取采样数据文件进行分析,将分析结果与信源设定的期望结果进行对比。 图8 FIFO异步写入时序图 图9 FIFO异步写入参数 时钟信号是其他信号设计的参照,为了模拟信号的真实情况,需考虑时钟信号存在的时钟偏移、时钟抖动以及占空比失真等不稳定因素。其中时钟抖动是造成时序问题的最主要原因,文本在信源设计中仅考虑时钟抖动的影响。时钟抖动可分为固定性抖动fDj(t)和随机性抖动两类,其中随机性抖动接近高斯分布,固定性抖动一般不具有随机性,其分布形式表现为峰峰值2μ[14-15]。为了能用统一的概率分布模型描述固定性抖动,将峰值分布近似为高斯分布的左右两个部分,在第nT个系统时钟附近,时钟信号的固定性抖动的概率密度函数如下: (10) 时钟信号的总体抖动fTj(t)可表示为随机性抖动和固定性抖动的线性叠加: (11) 由上述公式可知,时钟抖动时多重高斯分布的叠加,在计算时会对应多个σ值,为了降低计算复杂性,计算式中的σ取相同值。同理,在确定时钟信号有效沿位置后,数据信号也会相对于时钟信号沿存在随机性抖动,其分布规律符合高斯分布。通过设置不同的σ,可模拟生成不同噪声条件下的信源,通过设置不同的采样频率fsamp和采样时长t,可得到不同测试条件下的测试数据。在信源生成过程中,以FIFO异步时序为一个最小周期T,生成周期性信源数据并存储为二进制文件,其详细的参数设置如表2所示。 表2 信源设计参数 1)按表2所示设置参数,利用matlab模拟生成3个不同的数字信源,将生成数据存储为二进制文件; 2)将FIFO异步写入时序的参数和事件码序列信息填入csv文件,并上传至时序分析软件,填写信息如图10所示。 图10 FIFO时序输入配置 3)时序分析软件分别读取3个数据文件进行时序一致性分析,输出测试结果; 4)统计测试结果,如表3和表4所示,并与期望结果对比,验证系统检测的正确性。 表3 异常时序测试结果 表4 干扰信源时序参数测量结果 ns 测试项目测量值最大值最小值平均值期望值tWRpwl534850.250tWRpwh726869.770tSFD12710.110tFDH11710.010tXFD615859.960 测试表明,时序分析软件能够完全捕获理想信源和正确信源的目标周期,干扰信源目标周期捕获遗漏三个,故障和警告时序的位置定位正确。干扰信源中各时序参数测量值与信源设计时的期望值相符,说明数据分析软件能够对异常时序定位,分析结果具有较高的正确性和可靠性。 经分析,未被捕获的三个周期均为时序异常周期,且时序异常类型为逻辑值翻转,导致目标时序的事件码序列发生改变,未能与时序模式序列匹配成功,因此未能捕获目标时序。 本文基于对比测试原理设计时序一致性连续定量监测系统,针对系统实现涉及的关键技术展开研究。通过建立时序参数模型实现被测参数的图形化输入,取代传统的协议插件;利用事件码序列表征目标时序特征,在BM算法的基础上通过动态事件弯折和通配符匹配规则的设计提出了DEW-BM算法,并成功应用于目标信号的捕获;基于误差分析对时序异常检测方法作出修正,将误差范围内无法自动判别的时序设为警告状态。最后基于虚拟仪器的结构搭建了时序一致性分析监测系统,并通过信源设计,对时序分析软件的功能正确性进行测试。结果表明数据分析软件能正确获取基于csv文件输入的时序信息,对不同信源的时序分析结果与期望结果一致,具有一定的正确性和可靠性。但目前的研究中还存在不足之处,后期研究将重点解决以下问题: 1)对监测系统的实时处理能力进行分析和设计,使系统由离线处理转变为实时处理; 2)缺乏真实接口时序的测试实验,补充对实际电路时序的相关测试与分析; 3)当接口时序出现逻辑功能性错误时,事件码触发方法不能完全捕获目标时序,需完善触发条件设计。

2.2 目标信号捕获

2.3 异常时序分析

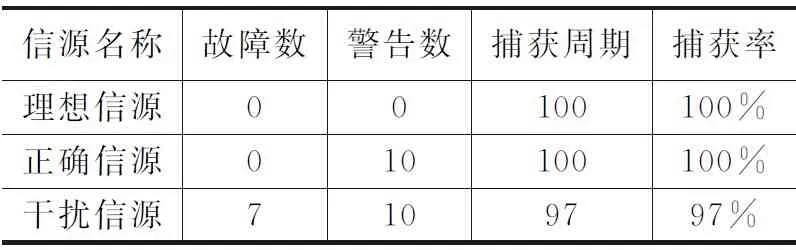

3 验证实验

3.1 信源设计

3.2 测试方法

3.3 测试结果

4 结束语