基于DSP的MIL-STD-1553B总线测试系统设计

2020-06-04张佳

张 佳

(西安航空学院 电子工程学院,西安710077)

MIL-STD-1553B 总线是为适应工业和军事的需要而提出的机载数据总线标准。MIL-STD-1553B 总线具有高速、灵活,通信效率高,修改、扩充和维护简便的特点。MIL-STD-1553B 最初是设计作为军用航空电子的航空数据总线,但目前已广泛地应用于军事、工业和科技领域。由于MIL-STD-1553B 总线优异的性能和特点,伴随着武器装备的更新,MILSTD-1553B 总线不仅在航空武器装备中得到了广泛应用,同时其应用也已扩展到了陆军和海军等其他兵种的武器装备中,空间飞行器、各类舰艇、地面装备等都有其应用。

MIL-STD-1553B 总线测试常用的测试方法是“工控机+测试板卡”的结构,工控机通常采用PCI/CPCI/PXI 等总线结构结构,配合相应的MIL-STD-1553B 总线测试卡,通过工控机中的上位机软件实现对MIL-STD-1553B 总线设备的控制与测试。这种测试方法的优点是成熟度高、周期短,缺点是成本高、测试系统体积重量大、不易移动。本文针对传统MIL-STD-1553B 总线测试系统存在的问题,提出了一种基于DSP 的MIL-STD-1553B 总线测试系统设计方案,该测试系统能够实现便携式测量且成本低,从而有效地解决传统测试方法所面临的问题。

1 MIL-STD-1553B 总线工作原理

MIL-STD-1553B 是美国国防部发布的一个军用标准,定义了机械、电气和串行数据总线的功能特征。MIL-STD-1553B 的全称是“数字时分命令/响应多路复用数据总线”。它具有多个冗余的平衡线路物理层、一个差分网络接口、时分多路复用、半双工命令/响应协议。该总线协议的功能是为不同系统之间进行数据和信息传递提供桥梁。

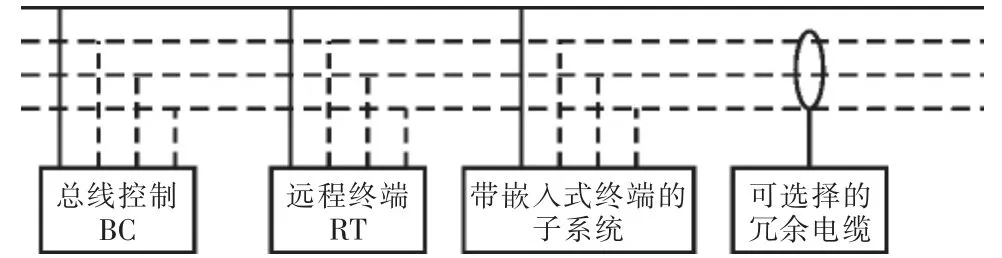

典型的MIL-STD-1553B 多路数据总线系统由控制多个远程终端(RT)的总线控制器(BC)组成,它们通过数据总线连接在一起,在总线控制器与所有相关的远程终端之间提供单个信息路径。数据总线上节点包含多种终端类型,通常包括总线控制器(BC)、远程终端(RT)和总线监视器(MT)3 种终端类型。这3 种终端通过多路总线接口(MBI)来完成其功能。一般情况下,将多路总线接口嵌在主控机内部,在一条数据总线上可以控制31 个远程终端,并且总线上也可以有1 个或多个总线监视器(BM)。总线监视器不参与数据传输,只能用作捕获和记录数据等[1]。在MIL-STD-1553B 数据总线上,只有总线控制器(BC)能够发起数据传输任务。各用户子系统设备作为远程终端(RT)是接入数据总线,如果远程终端(RT)要传输或接收数据,同样需要BC 进行控制[2]。各终端之间的信息传输方式有多种,在总线控制器与特定远程终端之间,或者在总线控制器与1对远程终端之间,允许6 种类型的信息。

(1)控制器到远程终端传输。总线控制器发送1个16 位接收命令字,紧随1 到32 个16 位数据字。然后,所选的远程终端发送1 个16 位状态字。

(2)远程终端到控制器传输。总线控制器向远程终端发送1 个发送命令字。远程终端然后发送1个状态字,紧随1 到32 个字。

(3)远程终端到远程终端传输。总线控制器发出1 个接收命令字,紧随1 个发送命令字。发送远程终端发送1 个状态字,紧随1 到32 个数据字。接收终端然后发送其状态字。

(4)无数据字的模式命令。总线控制器发送1个命令字,子地址为0 或31,表示“模式代码”类型命令。远程终端用1 个状态字响应。

(5)有数据字的模式命令(发送)。总线控制器发送1 个命令字,子地址为0 或31,表示“模式代码”类型命令。远程终端以1 个状态字作为响应,紧随1 个数据字。

(6)有数据字的模式命令(接收)。总线控制器发送1 个具有子地址0 或31 的命令字,表示“模式代码”类型命令,紧随1 个数据字。远程终端用1 个状态字响应。

为了提高MIL-STD-1553B 数据总线工作可靠性,单个总线由在1 MHz 时具有70~85 Ω 阻抗的线对组成。在使用圆形连接器的情况下,其中心引脚用于高(正)曼彻斯特双相信号[3]。发射器和接收器经由隔离变压器耦合到总线,并使用一对隔离电阻器和可选地耦合变压器分支出短截线连接。曼彻斯特编码用于在同一线对上呈现时钟和数据,并消除信号中的任何DC 分量。通常采用双冗余或三冗余方式。所有设备连接到所有总线。在当前主控制器发生故障的情况下,指定新的总线控制计算机。MIL-STD-1553B 数据总线的典型拓扑结构如图1所示。

图1 MIL-STD-1553B 总线拓扑结构Fig.1 MIL-STD-1553B bus topology

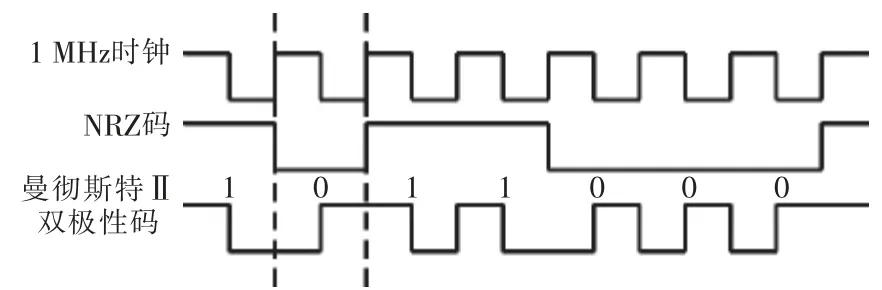

1553B 总线以异步、命令/响应方式实现信息的传输,它的工作方式为半双工方式。在数据传输过程中,所有的通信由总线控制器启动,并且终端设备无法自行启动信息传输[4]。总线上的数据以消息为单位,数据流由消息组成。总线消息包含命令字、数据字和状态字3 种类型的字,所有的消息字都采用曼彻斯特Ⅱ型码。

曼彻斯特Ⅱ型码原理如图2所示。

图2 曼彻斯特Ⅱ型双极性码Fig.2 ManchesterⅡbipolar code

2 1553B 总线控制器

在构建MIL-STD-1553B 多路传输数据总线时,必须使用1553B 协议芯片及其附属电路。目前,诸多厂家均推出了1553B 总线协议芯片,这些协议芯片普遍设计了多样的接口方式,可以与不同的主控制器连接,其中具有典型代表性的是DDC 公司的ACE(advanced communication engine)系列多功能模块,它属于超大规模混合集成电路,功能强,适宜复杂应用。

MIL-STD-1553B 协议的BU-61580 型号ACE 多功能模块是DDC 公司研制的1553B 总线协议芯片。它可在主处理器与1553B 总线之间实现通信,该芯片包含了终端与CPU 之间的完整集成接口,支持MIL-STD-1553 A 和B 以及STANAG 3838 总线协议[5]。ACE 模块采用1.9 平方英寸、70 引脚的薄型封装,采用适合严苛应用环境的多芯片模块MCM(multi-chip module)陶瓷封装。

BU-61580 芯片包含了2 个低功耗的双端收发器、协议逻辑处理单元、存储器管理逻辑单元、处理器接口逻辑单元并且内置了共享静态RAM 和缓冲接口。其电磁兼容性满足MIL-STD-883B 军标,芯片采用单电源(+5 V)供电。

BU-61580 与主机处理器的接口包含17 个内部操作寄存器以及额外的8 个测试寄存器和64 K×16个共享内存空间。BU-61580 的4 K×16 内部RAM 位于此空间中。

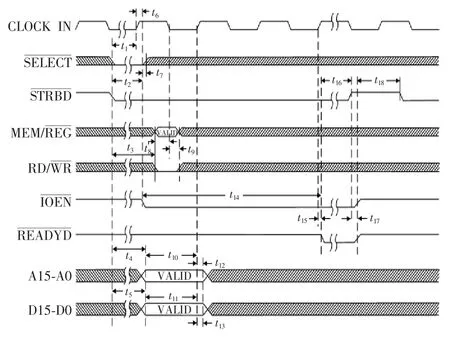

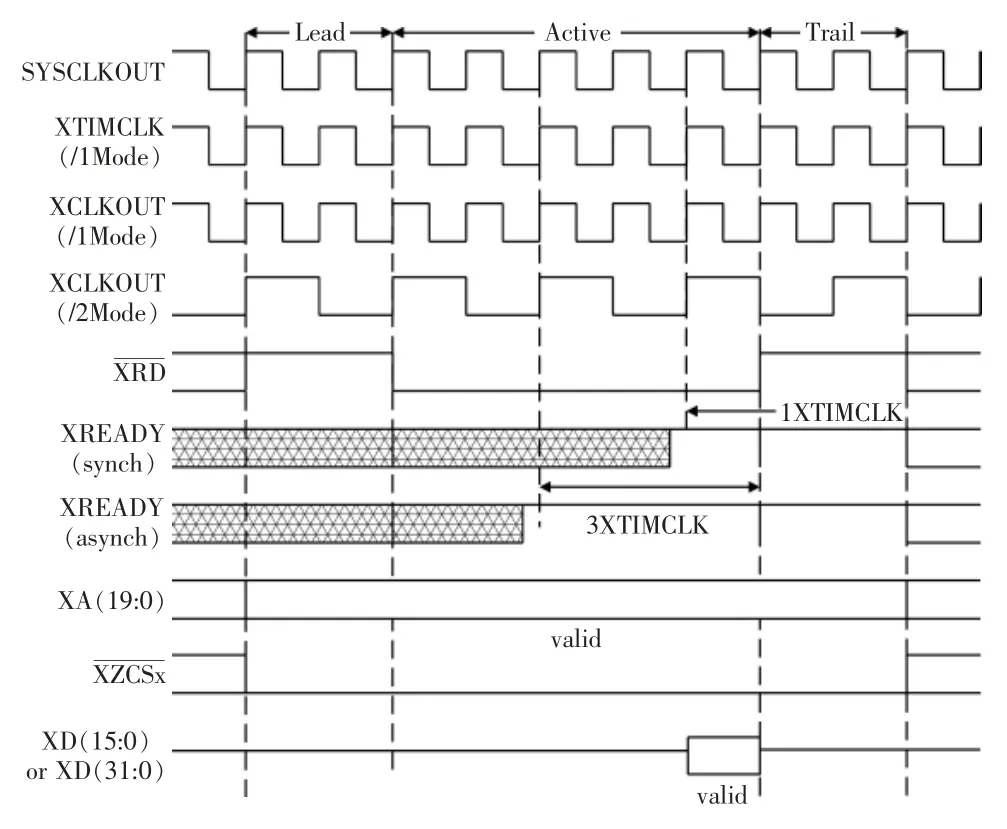

使用BU-61580 芯片开发1553B 总线接口,需掌握其引脚功能及内部操作寄存器。要实现对BU-61580 的读写访问及配置,需要严格按照其数据手册中的读写时序进行。图3给出了16 位缓冲非零等待模式下主处理器读取BU-61580 的RAM时序图。

图3 读取BU-61580 的RAM 时序图Fig.3 Sequence diagram of reading BU-61580 RAM

3 测试系统硬件设计

MIL-STD-1553B 总线测试系统的硬件结构主要用于实现各器件和芯片之间的电气、逻辑连接等,主要分为DSP 处理器、显示模块、电源模块、其他辅助模块等部分。下面分别对各模块的设计思路进行介绍。

3.1 DSP 处理器

为了实现对MIL-STD-1553B 总线协议控制器的访问和读写,并实现相应的测试逻辑,需要选用功能和性能均能满足需求的主处理器。经综合比较与考察,本设计选用了美国德州仪器公司(TI)的TMS320F28335 型号的DSP 处理器作为测试系统的主处理器,其运算速度最高可达150 MHz,并且支持AD 转换、I2C、CAN、SPI 等几乎所有的外设接口功能。

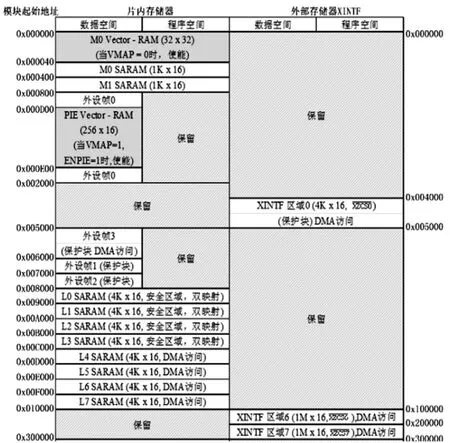

TMS320F28335 处理器使用具有多级流水线特点的哈佛总线结构,该结构允许其并行读写程序和数据存储空间。在TMS320F28335 芯片内部集成了大量不同的存储介质,TMS320F28335 片上有256 K×16 位的FLASH,34 K×16 位的SRAM,8 K×16 位的BOOT ROM,2 K×16 位的OPT ROM。F28335 对以上存储空间进行统一寻址也就是程序、数据和I/O统一寻址,通过这种寻址方式可以提高存储空间的利用率。另外,更重要的是TMS320F28335 DSP 还具备外部并行扩展接口XINTF,可进一步外扩存储空间。

F28335 内核本身并无存储空间,经由数据总线读写芯片内部集成的或者外部扩展的存储器。其总线按照改进哈佛结构,分成32 位的数据读、数据写数据总线,地址读、地址写总线,公用数据总线即程序总线,包括22 位的程序地址总线,其功能是传输程序空间的I/O 地址,32 位读数据程序总线,其功能是读入程序空间的指令或者数据。TMS320F28335通过32 位的数据地址总线和22 位的程序地址总线访问存储器空间和外部设备,最大可寻址4 G×16位的数据空间和4 M×16 位的程序空间。通常写的程序所需存放4 M×16 位空间已足够大,若大于4 M×16 位意味着程序空间不够处理,在实际中采用分页处理的方式,因为实际数据寻址空间为4 G×16位,通过分页机制可以扩展实际寻址的程序空间。要找到对应程序的空间地址与数据的空间地址,就需要对空间地址进行编码,将空间地址进行逻辑编码,也就是映射。F28335 的存储器配置及地址映射如图4所示。

图4 存储器配置及地址映射图Fig.4 Memory configuration and address map

TMS320F28335 的外部并行扩展接口XINTF分别映射到3 个固定的存储器区域,即XINTF ZONE0、ZONE6 和ZONE7。外部并行扩展接口XINTF 的每个区域均包含片选引脚,当对某个区域进行读写访问时,就要将信号线置低。XINTF 的存储器的3 个区域中的任何一个都可通过编程设定独立的等待时间,选通信号建立时间及保持时间,每个区域的读写操作都可以配置成不同的等待时间,另外可以通过XREADY 信号线延长等待时间,XINTF 接口的这些特性允许其方位不同速率的外部存储器设备[6]。

通过XTIMINGx 寄存器可配置每个区域的等待时间及选通信号的建立与保持时间。XINTF 接口的访问时序是以内部时钟XTIMCLK 为基准的,XTIMCLK 信号频率可以配置为系统时钟SYSCLKOUT 的频率或其一半。图5给出了XTIMCLK=SYSCLKOUT 情况下的读访问时序图,其中XINTF配置为XRDLEAD=2,XRDACTIVE=4,XRDTRAIL=2。

对比图3中BU-61580 的读写时序和图5中TMS320F28335 的读写时序可知,可以将F28335 的XINTF 模块的读写时序配置为满足BU-61580 读写的时序波形,从而实现两种器件的互连通讯。

图5 XINTF 读访问时序图Fig.5 XINTF read access sequence diagram

3.2 显示模块

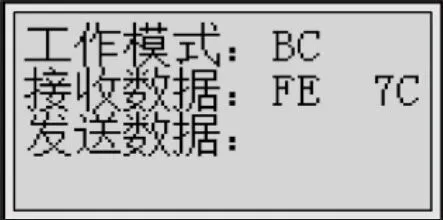

为实现MIL-STD-1553B 总线测试数据的实时显示,在测试系统中配置了LCD 液晶显示屏,选用的型号是LCD12864。本设计选用了带中文字库的LCD12864 液晶显示屏。该液晶显示屏具有多种通信方式,包括并行、串行通信方式。其内部自带国标一级、二级简体中文字库。其显示分辨率为128×64像素,具备8192 个16×16 点汉字以及128 个16×8点ASCII 字符集。通过该模块灵活的接口方式和简洁的控制方式,能够实现全中文人机交互界面,显示8×4 行16×16 点阵的汉字,完成图形文字显示。

利用液晶显示模块LCD12864 的显示功能,将MIL-STD-1553B 总线测试系统的工作模式、接收和发送数据实时的显示出来,能够使用户直观地了解总线测试状态。LCD12864 显示界面如图6所示。

图6 LCD12864 显示界面Fig.6 LCD12864 display interface

3.3 电源模块

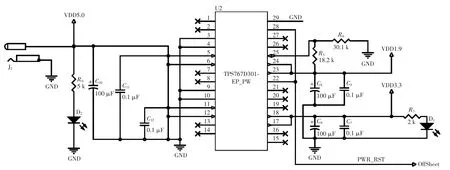

电源模块主要用于为测试系统中的各器件供电,由于各元器件的供电电压不同,因此电源模块需要提供不同的电压。电源电路的设计是硬件系统的核心。

1553B 总线控制器BU-61580 的供电电压和IO口电压是5 V,采用稳压电源的5 V 输出直接供电。

为降低功耗,同时便于DSP 芯片与外围芯片兼容,F28335 DSP 控制器采用双电源供电机制,在F28335 系统中需要提供以下3 种电源。

(1)内核电源VDD。用于为CPU、时钟源模块和大部分外设等内部逻辑电路提供电源。F28335的内核电源为1.8 V 或1.9 V。若CPU 工作频率低于135 MHz,可采用1.8 V 供电; 否则必须采用1.9 V供电。

(2)I/O 供电电源VDDIO。为便于与外围芯片兼容,DSP 控制器采用3.3 V 供电电源与外部接口相连。所有数字量输入引脚电平与3.3 VTTL 电平兼容,所有输出引脚与3.3 VCMOS 电平兼容。因而DSP 控制器与外围低压器件接口相连时,无需额外的电平转换电路。

(3)模拟电源VDDA 和VDDAIO,分别为3.3 V与1.9 V。用于为片内ADC 模块的模拟电路提供电源。

考虑到F28335 采用3.3 V 和1.9 V 双电源供电,本系统采用数字模拟地分离设计,电路如图7所示。设计电源电路时需要特别注意散热和电容匹配问题。本设计使用TPS767D301 电源转换芯片,它带有使能端的3.3 V 和一个可调输出通道,每路输出最大电流可达1 A。

5 V 输入电源经过TPS676D301 后经滤波器输出CPU 内核电源(VDD)1.9 V 和I/O 电源(VDDIO)3.3 V。

图7 电源电路图Fig.7 Power circuit diagram

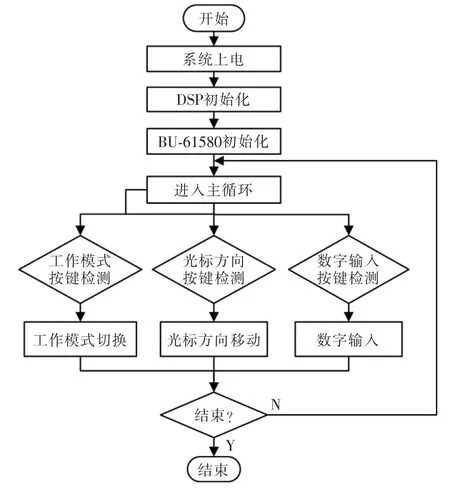

4 测试系统软件设计

软件部分是整个测试系统的核心,用于实现测试流程的逻辑。为使F28335 控制器的CPU 控制片内各功能模块正常工作,必须对其进行软件编程驱动,使系统时钟、片内外设等硬件资源按照各自功能和系统需求运行。进行驱动程序开发的基本思想是:首先通过代码描述片内硬件资源,然后编写程序对硬件资源进行设置。

为便于用户编程,TI 提供了驱动程序开发包和部分源程序。其中最基本的开发包是C/C++头文件和外设示例,可根据DSP 目标系统芯片的不同选择对应的开发包。开发包所提供的示例程序具有代码质量高、内容全面,结构规范、易于掌握,开发周期短、便于实时硬件评测等优点。基于这些代码库,可以方便地进行软件开发。

MIL-STD-1553B 总线测试系统的软件部分基于TI 提供的驱动程序开发包实现。系统上电后,首先初始化各器件,然后进入主循环。在主循环中,程序判断按键状态,包括工作模式切换按键、方向按键以及数字按键。如果检测到按键工作,软件根据按键类型执行相应的操作:工作模式切换按键按下,则软件控制DSP 输出命令使BU-61580 切换到对应的工作状态;方向按键按下,软件移动显示光标到下一位置;数字按键按下,在光标位置处输入对应数字。软件工作流程如图8所示。

5 结语

图8 软件工作流程图Fig.8 Flow chart of software principle

利用TMS320F28335 型DSP 处理器强大的外部并行扩展接口能够实现对BU-61580 总线控制器的读写访问与控制,结合LCD12864 显示模块可以设计出具有良好人机界面的MIL-STD-1553B 总线测试系统。此外该系统具有轻量、便携的特点,适合在外场对MIL-STD-1553B 总线设备进行测试。