基于双环系统的细步进频率合成器

2020-05-10沈文渊唐光庆杨清福穆晓华李庆洪蒋创新

沈文渊,唐光庆,杨清福,穆晓华,李庆洪,蒋创新

(1. 中国电子科技集团公司第二十六研究所,重庆400060;2. 空军装备部驻重庆地区军事代表室,重庆400060)

0 引言

频率合成器是雷达、通信、导航、电子对抗等电子系统的核心部件,其作用是利用高稳的参考信号作为基准,通过一系列的倍频、分频和混频等变频处理产生电子系统所需特定射频信号。频率综合器的频率带宽、跳频步进、相位噪声及杂散抑制等指标直接影响电子系统的功能和性能。现代军事电子系统对频率综合器的综合性能提出了越来越高的要求,宽频带、细步进、低相噪、低杂散、低功耗和小型化成为频率合成器的主要发展趋势。锁相频率合成因具有宽频带、低功耗及易于程控等优势而广泛应用于现代军用电子系统中[1-4]。

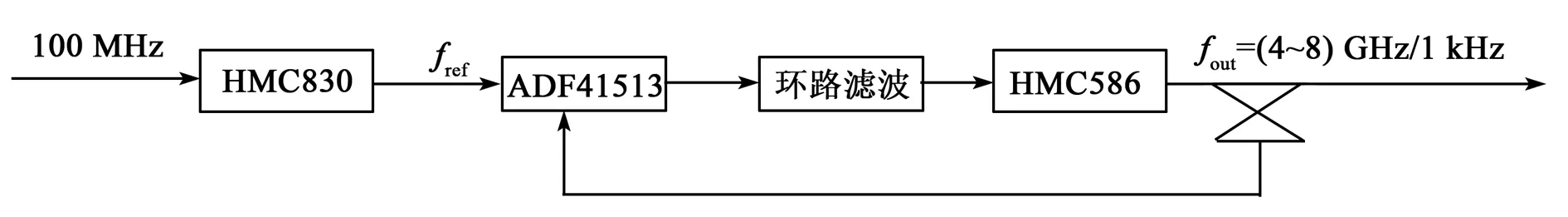

本文研究并设计了一种双环级联的锁相频率合成器,实现了宽带、细步进和低杂散的指标要求。该方案中,第一级锁相环采用HITTITE的集成锁相环芯片HMC830产生频率fref作为第二级锁相环的参考输入,第二级锁相环采用ADF41513+HMC586通过小数分频锁相最终产生4~8 GHz宽带频率信号输出,频率步进1 kHz。通过优化fref的值来消除小数分频锁相所带来的杂散问题,实现全频段范围内杂散指标优于75 dBc。

1 细步进锁相的原理

锁相频率合成作为一种间接频率合成法广泛应用于通信和雷达领域,经典的锁相环(PLL)系统由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)构成,如图1所示。

图1 锁相环结构原理图

PLL通过负反馈的相位控制系统进行输入参考信号与VCO输出反馈信号进行相位比较,然后通过鉴相器给出误差电压或电流经环路滤波器滤波处理后,产生一个稳定电压来控制VCO的频率输出fout。当负反馈环路稳定而进入锁定状态后,VCO输出频率与参考频率完全同步。目前,主流的数字鉴相器集成了参考输入的预分频数R和反馈输入的N分频,通过数字程控R和N的取值而实现PLL输出频率fout的变化,即

(1)

式中:fref=fin/R为鉴相频率;fin为参考频率。

因此,锁相频率合成方式通过选择宽带VCO器件,并控制数字鉴相器R和N的取值,易实现宽带的频率合成输出。

PLL根据分频N值的不同可分为整数分频锁相和小数分频锁相两大类。整数分频的N取值为整数,此时VCO输出的锁定频率为fref的整数倍。一般fref越小,环路滤波器对鉴相泄露杂散抑制能力越弱。fref≥1 MHz时,通过环路滤波器仿真调试及特殊频点陷波处理,可实现70 dBc左右的鉴相泄露抑制。如果鉴相频率再减小,鉴相泄露杂散很难满足工程应用中对杂散指标的要求。因此,一般整数分频的fref≥1 MHz,即频率步进不小于1 MHz。

小数分频锁相即N取值为小数,设N值分为整数部分Nint和小数部分Nfrac之和,即

N=Nint+Nfrac

(2)

此时VCO输出锁定频率为

fout=fref×Nint+fref×Nfrac

(3)

Nfrac的取值与鉴相器的小数分频位数相关。目前市面上主流的小数分频鉴相器如ADI公司的ADF41513,HMC704,以及国产振芯电子的GM4704等芯片均可达24位,换算过来即小数分频的精度小于1 Hz。因此,理论上小数分频可实现VCO频率范围内的任意细步进频率输出[5-6]。

2 小数分频杂散分析及双环锁相方案

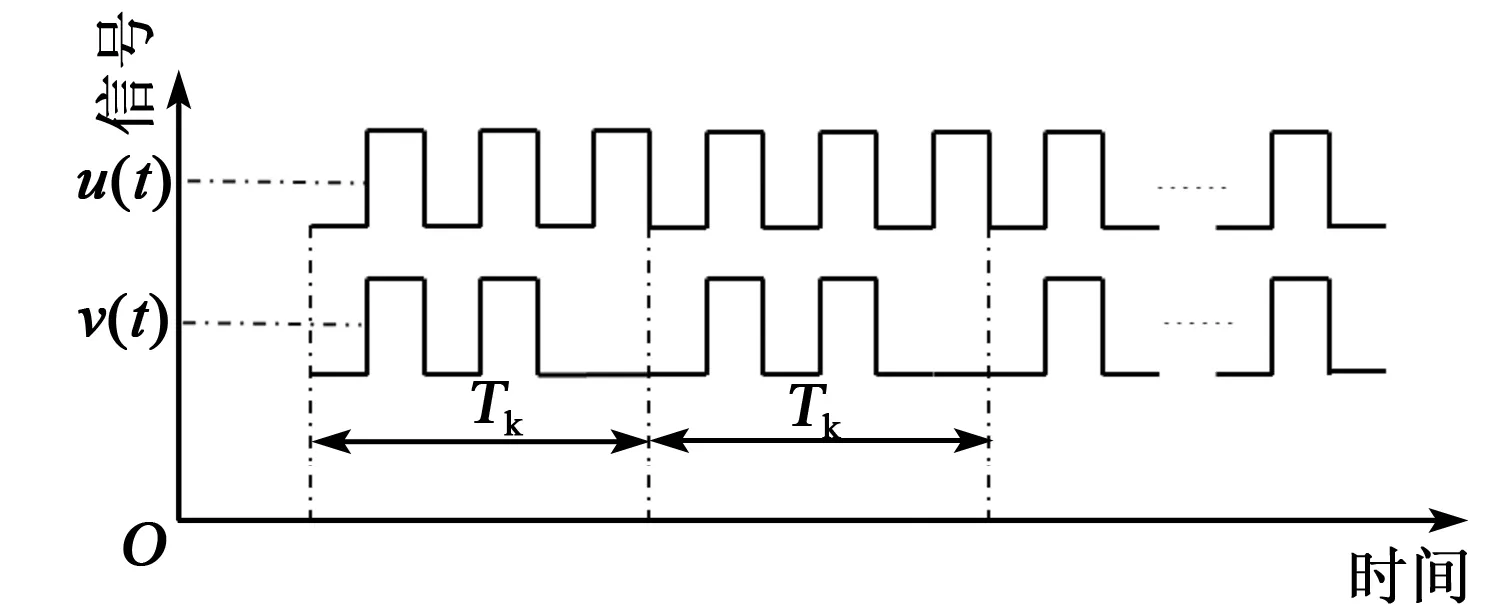

小数分频锁相是基于脉冲移除技术实现的。假设一个频率为fk的信号u(t)每隔Tk的时间移除F个周期,则输出信号v(t)每Tk时间就会输出fk×Tk-F个脉冲,即fout=fk-F/Tk。因此,通过改变F和Tk可实现小数分频。这里Tk可通过对fref的A分频得到,当信号锁定时,鉴相器预分频后输入与输出频率相等,即

fref=(fout-F/Tk)/Nint

(4)

(5)

式中A=Tk/fref。图2为脉冲移除原理。

图2 脉冲移除原理

通过小数分频的原理可发现,小数分频锁相可解决整数分频方式由于fref不能无限制减小而造成频率步进较大的问题,即解决了高频分辨率和fref间的矛盾。

小数分频锁相输出频率由整数部分和小数部分组成,也因此带来了PLL整数边界杂散(Nint×fref)和小数杂散(1×fref/Nfrac,2×fref/Nfrac,…)问题,整数边界杂散和小数杂散离中心频率很近,很难通过外部环路滤波器滤出,严重情况近端小数杂散仅比输出主频率信号电平低10~20 dB,严重影响通信系统的整体性能,直接限制了其在工程中的应用。因此,针对小数分频杂散问题需要新的技术加以解决。

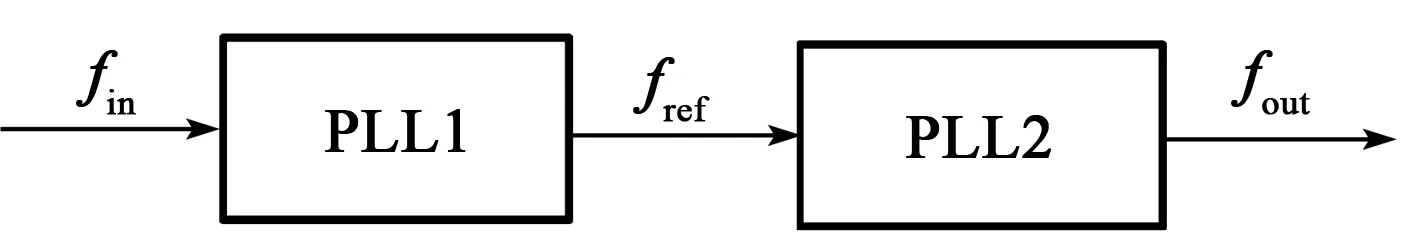

对于小数杂散问题可通过∑-Δ调制技术来解决[7-9],该技术通过对杂散进行整形,将杂散从低频段推到高频段,进而通过环路滤波器进行滤出。目前主流的小数分频鉴相器均集成了∑-Δ调制技术。因此,可较好地解决小数分频带来的小数杂散问题,但对于整数边界杂散∑-Δ调制技术无法有效解决。目前解决方法大多采用数字频率合成器(DDS)作为参考源,用作小数分频锁相环fref的参考输入[10],通过DDS改变小数分频锁相环输入fref,从而避开较近的整数边界杂散点,由于较远处杂散可通过环路滤波器滤除,因此,最终达到消除整数边界杂散的目的。一种典型的DDS参考锁相原理框图如图3所示。

图3 传统DDS+PLL方案

图3方案可解决小数分频锁相的杂散问题,但由于DDS也需参考频率fDDS输入,因此,还需增加额外的DDS参考产生电路,通常采用梳谱倍频滤波或单环锁相实现,该方式在成本、体积和功耗方面均需增加较大的额外开销。由于宽带细步进的小数分频频点数量大, DDS控制程序较复杂,也增加了较大的软件开销。因此,本文设计了一种低成本、低功耗的双环锁相系统,该系统设计思路是采用一级锁相环来代替DDS实现变参考的目的。该方案实现框图如图4所示。第一级PLL(PLL1)采用整数分频方式实现变参考,第二级PLL(PLL2)采用小数分频实现细步进。通过改变PLL1的输出频率,进而实现第二级小数分频锁相环的变参考目的,最终实现第二级小数分频锁相环的整数边界杂散的优化。与图3相比,该方案可节省一半以上的空间体积和功耗,实现了小型化的宽带细步进频率合成。

图4 双环细步进锁相方案

3 双环细步进频率合成器设计

首先根据工程实用的需求提出如下双环细步进频率合成器拟达到的技术指标要求:输入参考信号频率为100 MHz;输出频率为4~8 GHz;输出频率步进为1 kHz;相位噪声≤-95 dBc/Hz@1 kHz;杂波抑制≥70 dBc;跳频时间≤50 μs。

3.1 硬件方案设计

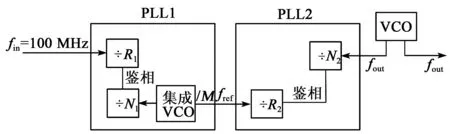

双环系统的细步进频率合成器采用一级整数分频锁相环(PLL1)和一级小数分频锁相环(PLL2)级联实现。PLL1采用HITTITE公司的HMC830集成VCO锁相芯片,该芯片的归一化噪声基底为-227 dBc/Hz,输出频率覆盖25~3 000 MHz,芯片封装尺寸为6 mm×6 mm,通过该集成芯片可实现设计的小型化。第二级小数分频锁相环芯片采用ADI公司的ADF41513鉴相器及HITTITE的HMC586型VCO芯片。ADF41513型鉴相器反馈频率最高可到26.5 GHz,归一化噪声基底优于-234 dBc/Hz。具体设计方案如图5所示。图6为鉴相器内部分频比设置示意图。

图5 细步进双环锁相设计框图

图6 双环锁相分频比设置示意图

双环系统最终输出频率与两级鉴相器的R分频和N分频均有关,即

(6)

式中:fin=100 MHz;N1/R1为第一级整数分频锁相环分频比;M为HMC830的VCO输出的分频数;N2/R2为第二级小数分频锁相环的分频比,其中N2为小数。

在实际设计中,固定R1和R2不变,双环系统输出最终频率确定的情况下,给出一个N1/M值,则可计算出N2。即通过改变N1和M值,可实现小数分频锁相环fref的改变,实现不同fout对应参考信号fref的调整,进而实现消除整数边带杂散的目的。该双环频率合成系统硬件电路实现简单,以最低的成本和功耗实现变参考,从而解决小数分频整数边带杂散的问题。

3.2 软件方案设计

基于双环系统的细步进频率合成器的软件部分设计重点在于:通过N1/R1选择来避开第二级PLL小数分频所带来的整数边带杂散。本方案控制部分采用现场可编程门阵列(FPGA)硬件,基于硬件描述语言最终实现。

首先对全频段4~8 GHz进行分段处理,假设总共分段数为W段,每段频率带宽Δf=4 000/W(MHz)。每段内采用相同的N1/M值,通过给定的N1和M计算对应输出频率的N2值。这里设第一个输出频点值为4 000 MHz,第二个频率点为4 000 MHz+1 kHz,依次类推,那么第k个频点对应频率值为

fk=4 000 MHz+(k-1)×1 kHz

(7)

第k个频点对应的频段数i(1≤i≤W)可表示为

(8)

式中INT表示取整。

第k个频点对应输出频率值的N2值为

(9)

根据计算的N2值,通过FPGA对2个PLL的R1、N1和R2、N2寄存器进行配置,然后测试输出最终频率的杂散,如果杂散指标不满足要求,则调整N1和M值直至满足,通过这种方式找出所有频段杂散满足指标的N1和M值。图7为算法示意图。表1为优化后的输出前6段频率对应取值表。

图7 双环锁相软件设计流程图

表1 1~6段优化后的N1、M及fref

4 双环系统的细步进频率合成器性能分析

按照前文所述设计方案对双环系统的细步进频率合成器进行电路和结构设计,加工实物如图8所示,产品总尺寸为40 mm×40 mm×10 mm,该体积中包含了两级锁相环硬件电路、+12 V电源处理电路和FPGA控制电路,频率合成器总功耗为2.6 W。

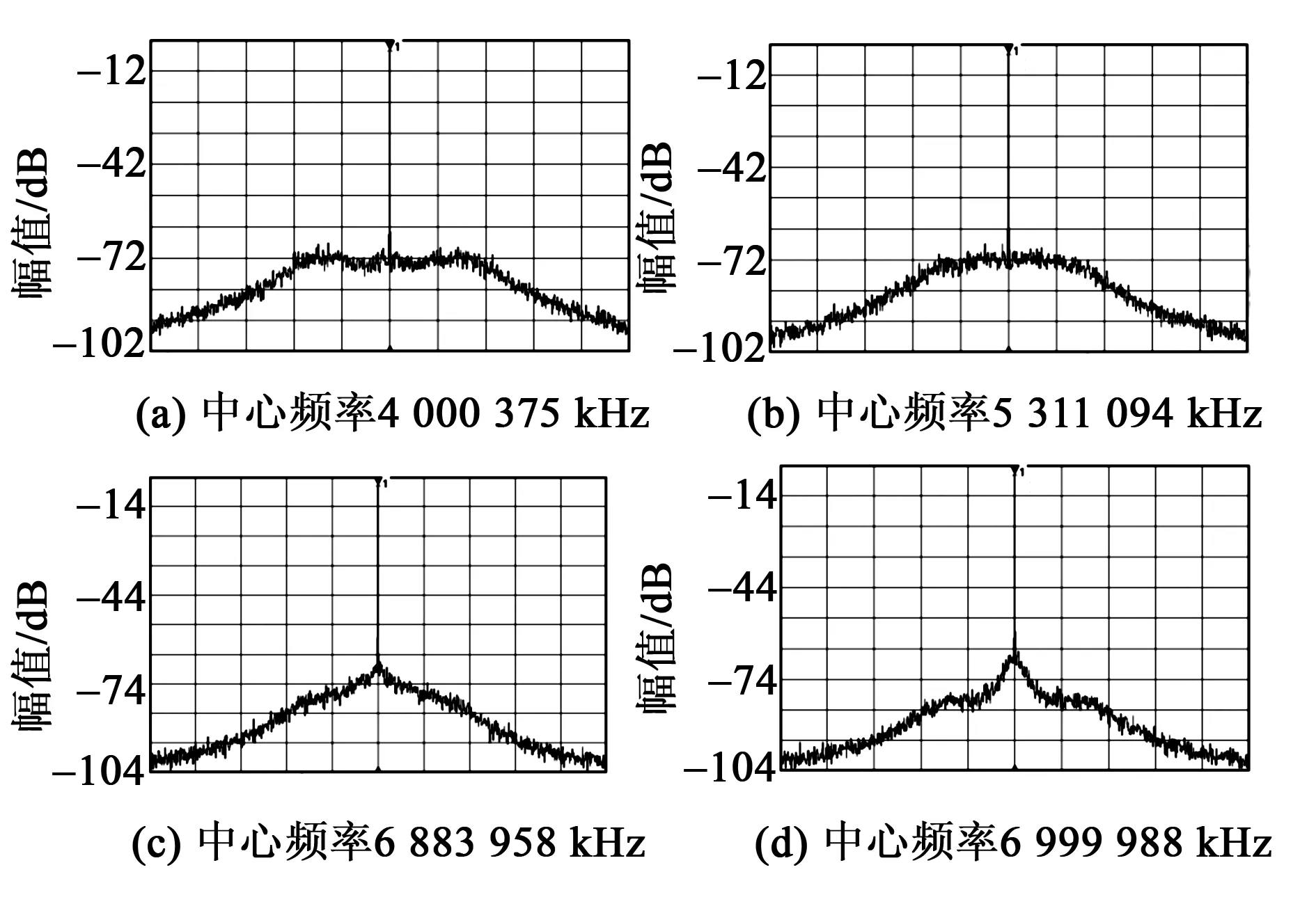

图9、10分别为工作频带内任选4个频点:4 000 375 kHz,5 311 094 kHz,6 883 958 kHz和7 999 988 kHz的频谱图。图9中频谱仪分辨率带宽设为5 MHz,图10中频谱仪频宽设为20 MHz。由图9、10可看出,所测试频率杂散均优于75 dBc。

图9 分辨率带宽为5 MHz频谱测试图

图10 分辨率带宽为20 MHz频谱测试图

图11为中心频率不同、频宽100 MHz时的频谱测试图。综合图9~11可知,本文提出的双环系统细步进锁相方案可消除小数分频锁相所带来的整数边带杂散,实现了宽带、细步进合高杂散抑制的频率合成输出。

图11 分辨率带宽为100 MHz频谱测试图

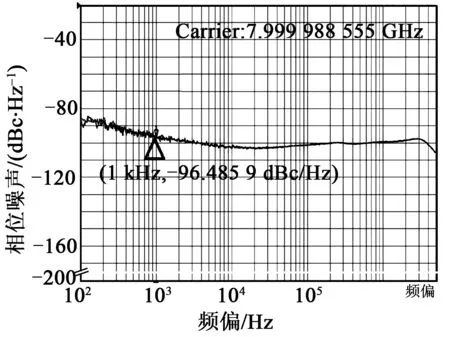

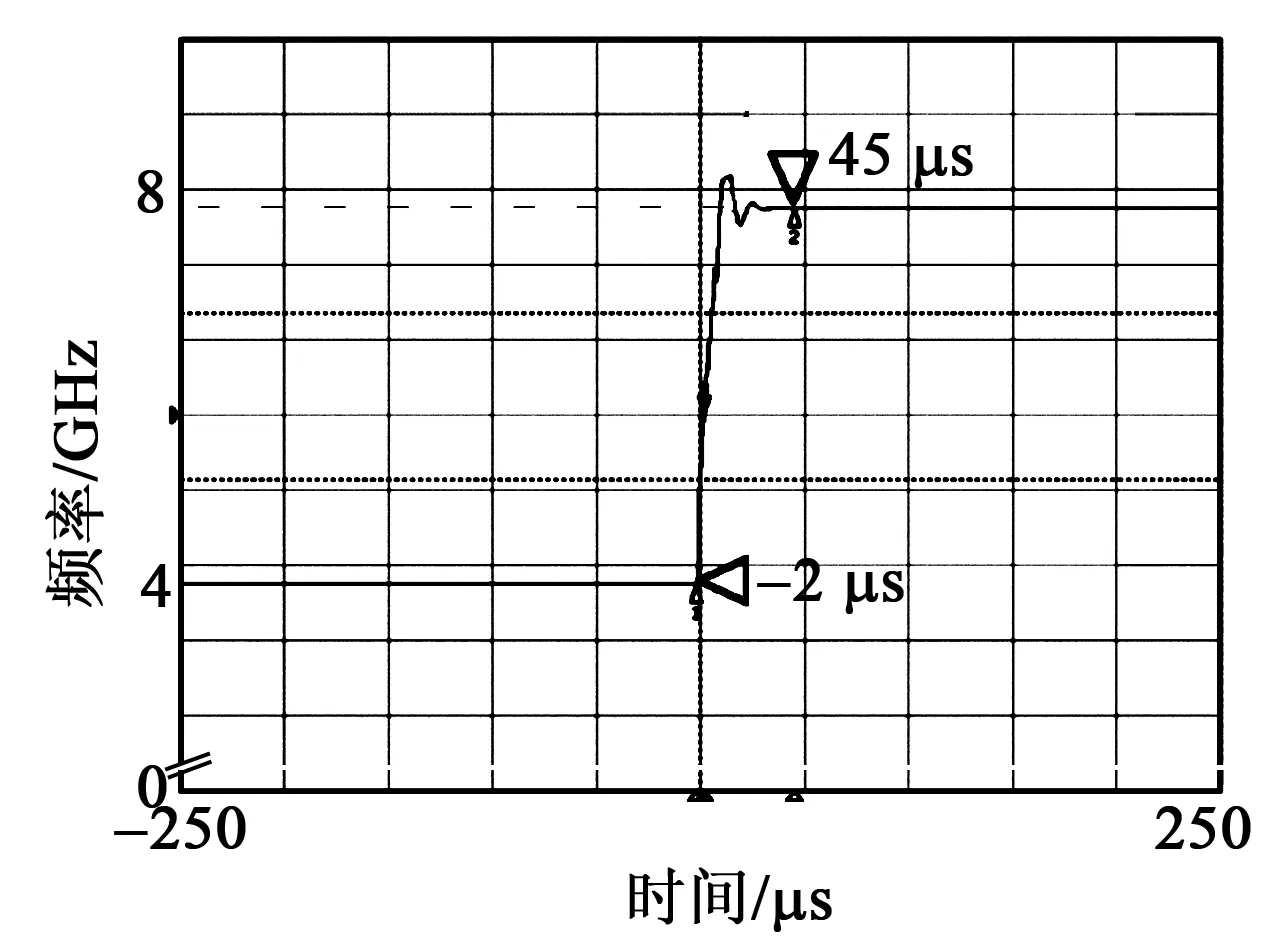

图12、13分别为该频率合成器的相位噪声和跳频时间实测结果。由图12、13可看出,频率合成器相位噪声优于-96 dBc/Hz@1 kHz, 跳频时间小于47 μs;实测指标与拟达到对比如表2所示。由表可知,所有指标均达到预期值。

图12 输出频率8 GHz时相位噪声测试曲线

图13 输出频率4~8 GHz间跳频时间测试图

表2 频率综合器拟达到指标与实测指标对比

5 结束语

本文介绍了一种基于双环系统的宽带细步进频率合成方法,该方法采用两级级联锁相环的方式,解决了在细步进的情况下小数分频锁相所带来的整数边带杂散问题。根据该方法设计的频率合成器模块实测结果表明,4~8 GHz全频段范围内杂散抑制可达75 dBc,相位噪声优于-96 dBc/Hz@1 kHz,跳频时间小于47 μs,满足系统对频率合成信号高质量的要求。此外,该方案还具有小型化、低成本、低功耗、设计简单等优点。通过该方案易对输出频率范围进行拓展,具有极高的实用价值和较好的应用前景。