一种基于FPGA的二维DBF实现方法

2020-05-08刘国浩袁子乔崔向阳

陈 亮 刘国浩 袁子乔 崔向阳 田 欢

(1.西安电子工程研究所 西安 710100;2.陆军装备部驻西安地区军事代表局 西安 710032)

0 引言

本文提出的DBF架构主体内容包括两部分,第一部分是将多路A/D数据写入双口RAM,根据DBF模块工作时钟和A/D数据有效速率的N(N为正整数)倍关系,将每个采样点的A/D数据从双口RAM中读取N次,以保证RAM读写等速率。速率转换的过程[1],将每个采样点的A/D数据读取次数参数化,可兼容雷达系统的不同采样频率;第二部分是基于DSP48构建复数乘法单元,利用DSP48的PCIN/PCOUT端口,对多路A/D间的复乘结果级联累加[2],由于级联端口之间有专用的布线资源,从而保证DBF模块达到更高时钟频率,或者同等资源利用率的情况下,FPGA更容易达到时序收敛。本文所述的阵元间直接加权的DBF方法,虽然比降维DBF方法占用更多DSP48资源,但增加了雷达系统波束形成的灵活性和不同采样频率的兼容性。DBF模块设计充分利用DSP48内部加法器、级联管脚和专用的布线资源,相比于直接使用复乘和累加IP Core,节约资源的同时更加易于时序收敛。

1 A/D数据速率转换

1.1 系统速率分析

假设FPGA收到的M路并行的A/D数据,其中每路有N个通道的串行数据,即单个采样点的数据量K=M×N,单个采样点的回波数据可用式(1)表示

(1)

理论上对N个通道的串行数据si1,si2…siN,其中i=1,2…M,对应N个接收DBF权值wi1,wi2…wiN,这里的接收DBF权值包含了方位维和俯仰维的指向信息[3],则单个采样点的DBF结果可表示为式(2)

(2)

假设雷达系统采样频率为fs,则上述M路A/D数据有效速率为fs×N,则DBF模块时钟频率fdbf可以取值为式(3)

fdbf=I×fs×N

(3)

式(3)中I为正整数,DBF模块时钟频率fdbf可结合需求合理设置I的取值。

1.2 双口RAM读写控制

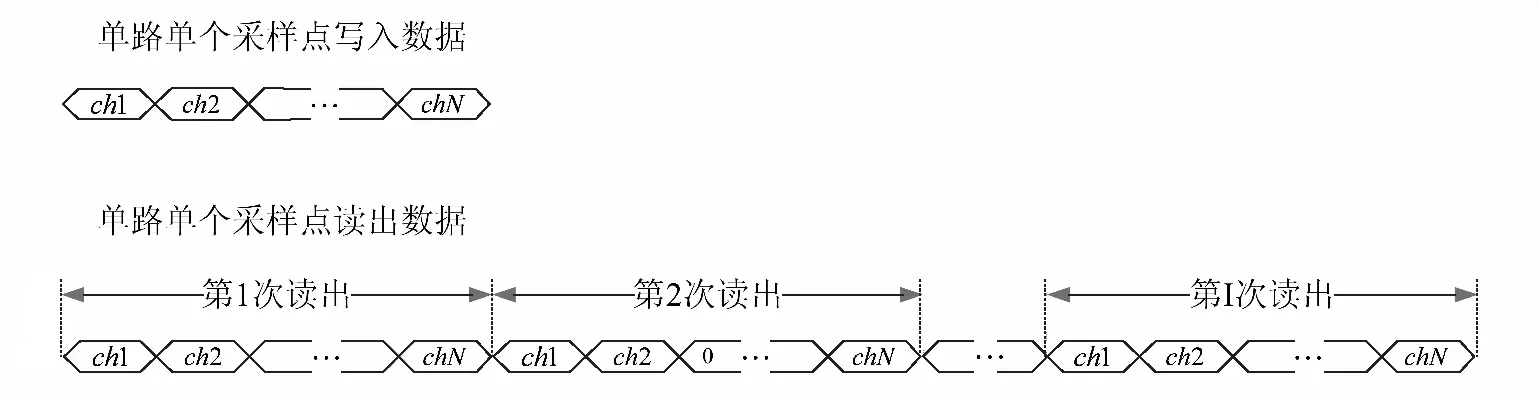

根据式(3)的速率关系,M路A/D数据流分别写入M个双口RAM,写有效速率为fwr=fs×N,RAM的读时钟frd=fdbf,则frd=fwr×I,即读时钟是写有效速率的I倍。通过控制每个RAM的读节奏,保证每个采样点的N个串行数据重复读取I次,可以保证读写的有效速率相等。单路单个采样点的N通道数据的RAM读写数据时序图如图1所示。

图1 RAM读写数据时序

RAM将单路单个采样点的N通道数据重复读取I次,对应I个指向的DBF接收权值,可同时形成I个接收波束,在FPGA资源使用合理的情况下,对RAM读出数据并行使用L次,则最多可同时形成波束个数P为

P=I×L

(4)

若雷达系统有两个基带采样频率fs1和fs2,根据式(3)合理设置DBF模块时钟频率fdbf,保证fdbf与fs1、fs2均是整数倍关系,即

fdbf=I1×fs1×N

fdbf=I2×fs2×N

(5)

根据当前雷达工作的采样频率,参数化控制RAM读出每个采样点的次数I。因此这种RAM转换速率的方式可以兼容雷达系统的两种采样频率,适用于具备搜索、跟踪等多功能的相控阵雷达。

2 级联DSP48的DBF模块设计

对于上述M×N形式的数据下传格式,M路并行数据,每路每个采样点有N个串行通道数据。由式(2)可知,先对第i路(i=1,2…M)的I×N串行数据与对应的DBF权值进行复乘运算,再对M路复乘结果并行求和,最后对求和结果进行N个串行累加,最终得到单个采样点的I个波束数据。本节先基于DSP48构建复乘单元,再利用级联的方式将M个复乘单元级联相加输出,最后构建累加器,将串行数据累加输出波束数据。

2.1 基于DSP48的复乘模块结构

复数乘法运算过程如式(6)所示

(a+jb)×(c+jd)=(ac-bd)+(ad+bc)j

(6)

基于式(6)的复数乘法表示,构建的复乘器结构如图2所示,图2中使用了4个DSP48,进行了4次乘法运算与2次加法运算,称为4M2A架构。

图2 4M2A结构的复乘单元

将式(6)的复乘表示方式转换,其结果也可用式(7)的方式表示。

(a+jb)×(c+jd)=[(a-b)×d+(c-d)×a]+

[(a-b)×d+(c+d)×b]j

(7)

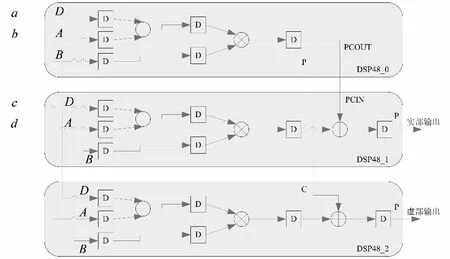

由式(7)可知,实部、虚部有公共项(a-b)×d,因此可通过级联的方式,进行3次乘法和5次加法,只需3个DSP48便可实现复乘运算,称为3M5A结构,其复乘器结构如图3所示。

图3 3M5A结构的复乘单元

对于上述两种复乘结构,单个3M5A结构的复乘单元更节约DSP48资源,但在大型阵列雷达DBF实现过程,多路A/D数据与对应的DBF系数复乘后仍需要并行相加,即将多个复乘单元级联起来,一路的复乘结果作为输入与另一路复乘结果相加,采用复乘单元间级联的方式实现多路复乘结果并行相加。本文针对4M2A复乘结构,详细介绍了多路并行DBF实现方法。

2.2 复乘单元间的级联结构

将图2的复乘单元中DSP48_0与DSP48_1最后一级加法器修改,将复乘单元的实部、虚部结果作为输入,连接到下一个复乘单元,即形成了多个复乘单元的级联,最后一个复乘单元的输出即为多路复乘结果的累加结果。需要注意的是相比于前一级复乘单元输入数据a1,b1,c1,d1,后一级复乘单元输入数据a2,b2,c2,d2应延迟两个时钟节拍,保证复乘单元间级联相加的数据对齐。图4给出了相邻两个复乘单元的级联结构。

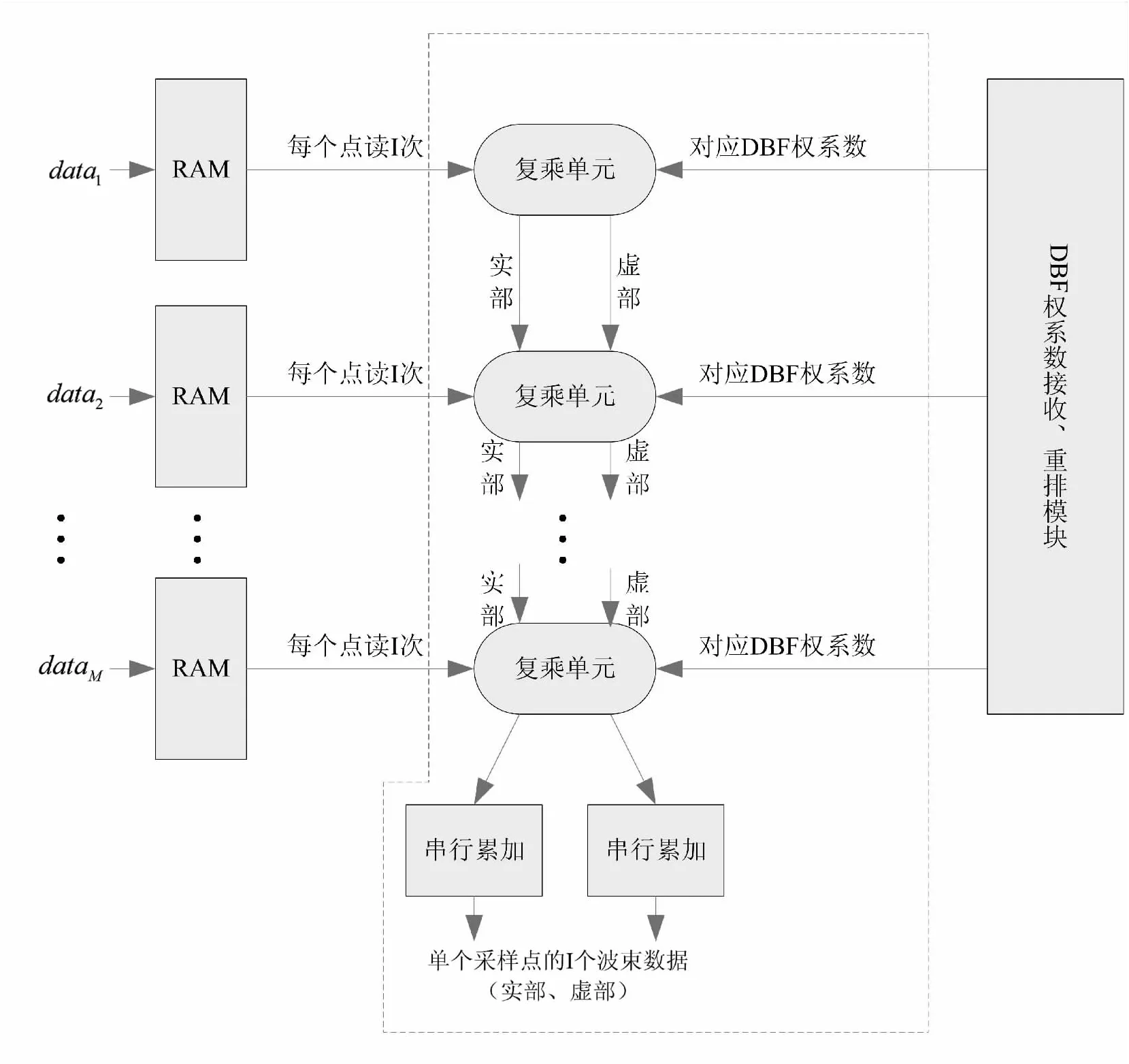

2.3 DBF模块整体流程

基于1.1节假设的M×N的A/D数据格式(M路并行数据,每路N个通道的串行数据),给出了DBF模块的整体设计方法:M路并行数据分别写入RAM,根据写数据有效速率和读时钟频率的倍数关系,逻辑产生读节奏控制,将单路单个采样点的数据重复读I次,并保证RAM读写速率相等。M路RAM读出的数据进入M个复乘单元,与对应DBF权系数复乘,M个级联的复乘单元对复乘结果进行并行相加,最后将并行累加结果进行N个串行累加,输出单个采样点的I个波束数据。DBF模块设计流程如图5所示。

图5所示的DBF设计模块,能将M×N的数据合成I个波束数据,若雷达系统要求最多形成P个波束,且P是I的整数倍,即P=I×L,L为正整数。则可将图5虚线部分重复例化L次。

图4 相邻复乘单元间的级联结构

图5 DBF模块整体流程

2.4 DBF实现结果分析

对于全阵列DBF的实现方式,FPGA内部将二维面阵数据等效于一维线阵来做乘累加处理,只是每个阵元对于的DBF权值包含方位维和俯仰维的复合信息。因此为便于实验的方向图对比,这里假设二维面阵数据对应DBF权值为一维形式,系统的实验参数如下所述。

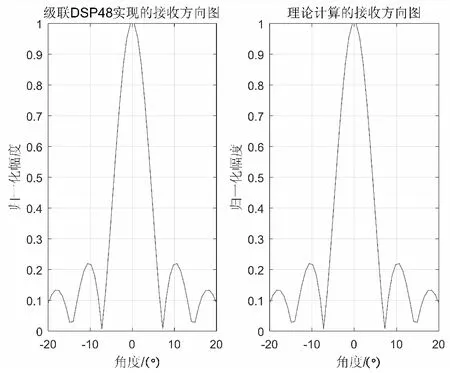

设系统基带采样频率为2.5 MHz,A/D数据格式M×N=4×16,即4路并行数据,每路16个串行通道数据,每路有效数据速率为2.5×16=40 MHz,根据式(3)的时钟频率关系,取DBF模块工作时钟为240 MHz。按图5流程,4路数据分别进入4个双口RAM,每路数据重复读出6次后,分别进入4个复乘单元与对应6个指向的DBF权复乘。最后一个复乘单元输出的实部、虚部数据分别进入累加器进行16个数的串行累加,得到单个采样点的6个DBF数据。并行例化图5虚线部分8次,在-20°~20°方向等间隔同时形成48个接收波束。图6给出了基于DSP48级联的DBF模块仿真方向图和理论方向图。

图6 FPGA仿真方向图与理论方向图对比

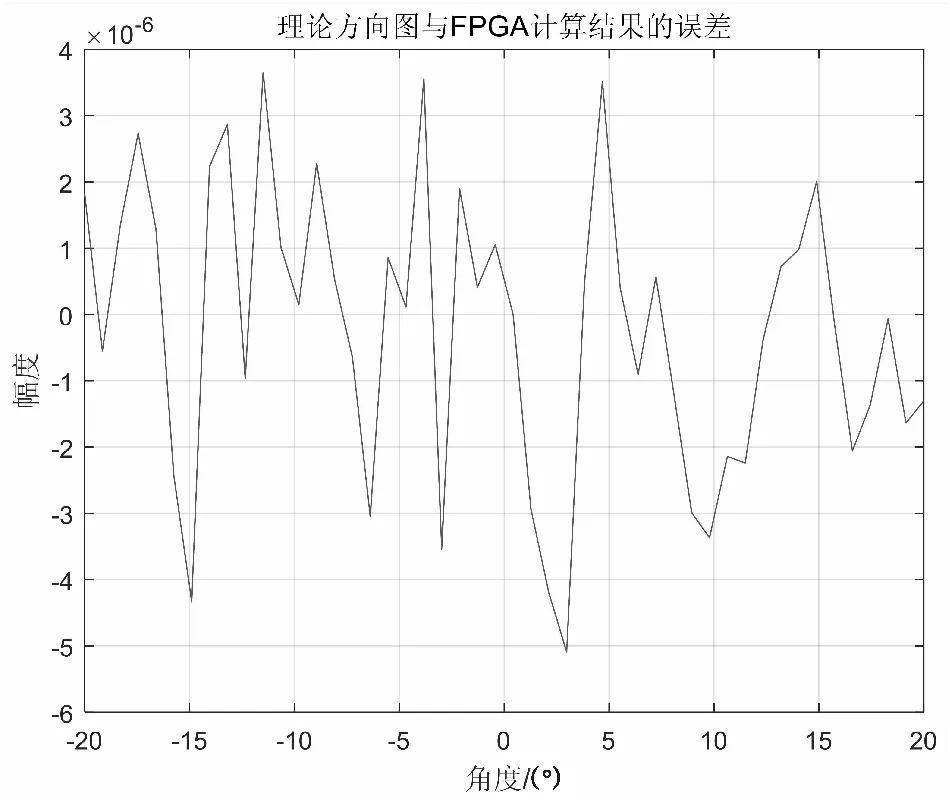

由图6可以看出,归一化后FPGA计算的方向图与理论方向图的归一化结果整体相同,两个方向图幅度相减得到理论值与实际计算值的归一化误差,如图7所示。

图7 方向图实际计算值与理论值误差

由图7可知,归一化方向图的理论值与实际计算结果误差在10-6量级,因此本文所述的级联DSP48的DBF方法具有可实现性。

2.5 DBF模块优点总结

1)FPGA资源与性能优化:图5所示的DBF模块能够同时形成I个波束数据,其中每个复乘单元使用4个DSP48,最终两个串行累加器使用2个DSP48,因此若雷达系统要求最多形成P=I×L个波束,则共使用DSP48个数为

(4×M+2)×L

(8)

使用传统复乘核累加IP Core构建DBF子模块的方法,每个DBF子模块使用5个DSP48(复乘占用3个DSP48,实部、虚部累加占用2个DSP48),则在同等条件下共使用DSP48的个数为

5×M×L

(9)

对比式(8)、式(9),M×L较大时,即A/D数据量大、形成波束个数多的情况。级联DSP48的DBF方法比传统方法的DSP48利用率降低了约20%,且级联DSP48的方式使用了DSP48内部专用布线资源,更有利于FPGA时序收敛,在工程实现上具有突出的优势。

2)雷达系统灵活性提高:本文所述DBF方法,采用对阵元直接加权的方法,每个阵元对应一个包含方位相位、俯仰相位的综合DBF权值[4]。对于二维相控阵雷达,这种阵元级直接加权的DBF方法增加了方位维、俯仰维形成的波束个数灵活程度;对A/D数据写入RAM进行速率转换的模块,可兼容雷达系统多种采样频率,满足雷达系统搜索、跟踪等多功能需求。

3)DBF计算误差降低:FPGA乘法器输出会带来数据位宽的成倍扩展,因此需要对乘法结果进行截位,截位的末位舍弃会对处理结果带来误差。传统DBF方式一般进行两级截位,级联DSP48结构的DBF模块,只需对累加结果进行一级截位,因此级联DSP48的DBF方法能够提高计算精度。

4)具备模块可复用性:本文所述的RAM读写控制模块、图5虚线中DBF子模块均能够满足不同雷达系统DBF功能需求,只需根据系统需求修改相应参数,具备可移植性。

3 结束语

本文根据雷达系统对波束形成灵活性的需求,充分利用FPGA内部DSP48结构和功能,采用DSP48级联的方式构建复乘单元,且对多个复乘单元级联的方式,构建DBF总体模块。同样在大阵面多波束形成条件下,相对于传统基于复乘、累加IP Core的DBF模块方法[5],级联DSP48的DBF实现方法节约了近20%的DSP48资源,且级联使用DSP48专用的布线资源,更利于FPGA时序收敛。本方法兼容雷达系统的不同采样频率,工程上具有一定的复用性。