基于FPGA的多通道数据采集与多速率发送系统设计

2020-04-21郑瑞肖顺文王涌陈韵文罗春梅

郑瑞 肖顺文 王涌 陈韵文 罗春梅

摘要:本文设计了一种多通道数据采集与发送速率可变的系统,采用FPGA芯片EP4CE10F17C8N作为核心控制器件,利用Verilog HDL在QUARTUS II 13.1平台上对数据采集模块、数据存储模块、数据发送模块以及系统控制模块进行描述,并使用Modelsim仿真工具对各个模块进行模拟仿真,最后通过AC620开发板测试,实现了多通道的数据采集和速率可变的串口发送功能。

关键词:数据采集;FPGA;Verilog HDL

中图分类号:TP274.2 文献标识码:A 文章编号:1007-9416(2020)01-0117-02

0 引言

科学技术的蓬勃发展,数据采集系统已广泛应用于各个领域,航天、军事、医疗、工业等尤其是在高精度产品的检测和监控项目中发挥着重要作用。与单片机、ARM相比,FPGA具有内部资源丰富、并行处理能力强、稳定性好、可重配置等优良特点,特适合用于数据采集系统设计。本设计以FPGA芯片作为核心控制器件,实现8通道12位分辨率的A/D数据采集与速率可改变的串口发送系统。为方便在AC620开发板上进行测试,将本系统的采样率设计为6.25MHz,发送速率为1200、2400、9600、19200、115200等,利用RS232串口将数据发送到PC端。与传统的数据采集系统相比,本设计将数据采集系统与数据发送系统相结合,同时发送速率可变,实现了数据采集与发送的一体化。

1 系统设计

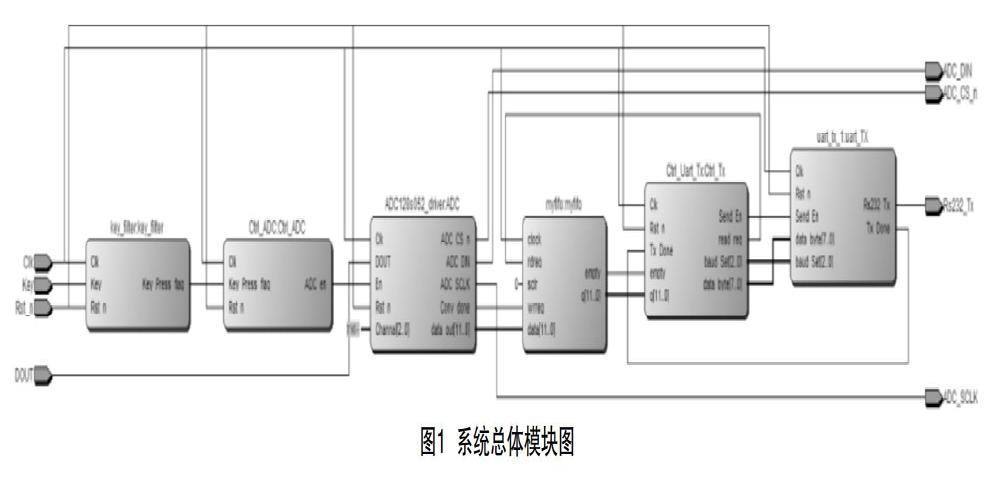

1.1 系统总体电路设计

如图1所示为本系统设计模块图,该系统由按键消抖、控制A/D采样、数据采样、数据存储、控制数据发送、串口发送等六个模块组成。当控制A/D采样模块检测到按键按下,立即产生使能信号启动A/D数据采样模块进行100次的数据采样,因A/D采样的速率与串口发送速率不匹配,为保证数据不丢失,设计将采样数据暂存FIFO存储器中,当控制数据发送模块检测到FIFO中有数据时便启动串口发送数据,一直到FIFO中全部数据发送完为止。

1.2 按键消抖模块设计

物理按键存在一个反作用弹簧,因此当按键按下或者松开时均会产生额外的物理抖动,物理抖动会产生电平的抖动,抖动的次数与时间间隔不可预期。当控制A/D采样模块检测到按键按下时就会启动A/D数据采样模块进行工作,不断启动数据采集与发送,与设计相悖,因此需要滤除抖动。一般情况下,抖动的时间会持续20ms左右,本设计通过软件方式编写状态机进行处理,产生一个按键按下标志信號Key_Flag,当系统检查到按键真正按下,拉高Key_Flag,控制系统开始数据采样。

1.3 A/D数据采样模块设计

设计使用的模/数转换器为逐次逼近型的低功耗芯片ADC128S052,具有8通道以及12位的分辨率,因此1bit代表的电压值即为VA/4096。对于FPGA,按照SPI时序搭建控制电路,以实现对ADC128S052的控制。ADC128S052通过SPI接口与FPGA进行通信。本设计采用的SCLK频率为6.25MHz,利用线性序列机的设计思想,产生一个两倍于采样时钟SCLK的信号SCLK_2,对系统时钟50MHz进行四分频即12.5MHz。对时序图分析,在程序设计中,通过对SCLK_2进行计数,在不同的计数点给CS、SCLK、DIN、DOUT信号不同的值即可产生该时序。

1.4 串口发送模块设计

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,UART)是一种异步收发传输器,其数据发送时将并行数据转换成串行数据来传输,在数据接收时将接收到的串行数据转换成并行数据,可以实现全双工传输和接收。设计采用RS232的接口标准规范,配置是8N1(即8位数据位、无奇偶校验位、1位停止位),根据串口发送一字节的时序图,当bps_clk信号的第1个上升沿到来时,字节发送模块开始发送起始位,接下来的2~9个上升沿,发送8个数据位,第10个上升沿到第11个上升沿为停止位的发送。在程序设计时,利用两个计数器,一个计数器bps_cnt用于计数来产生波特率时钟;另一个计数器则是对bps_clk,也就是每一位信号开始的标志进行计数,利用线性序列机的思想,根据计数值给对应计数点赋值即可。

为实现发送速率可变,保证模块的复用性,设计一个发送速率查找表,当需要不同发送速率时,只需要设置不同的波特率时钟计数器的计数值。同时由于A/D采样数据为12位,而串口一次只能发送8位数据,因此程序设计时通过产生一个Sel信号来控制将待发送的12位数据分成高4位和低8位,然后传给UART串口发送。

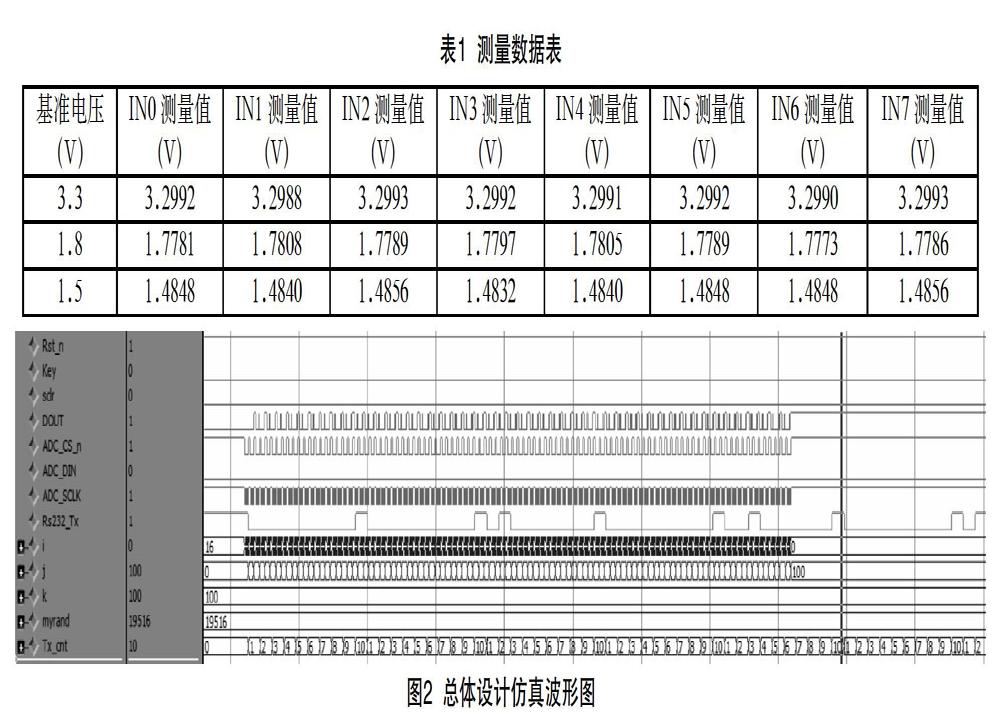

2 系统电路及仿真测试

2.1 程序仿真

编写Testbench测试文件,利用仿真工具Modelsim进行模拟仿真,结果如图2所示。模拟仿真时,设计采样通道为通道0,A/D转换的结果DOUT依次输入0到99,100个数,串口发送速率115200Hz,通过仿真图可以得到采样通道为通道0,采样频率为32.5MHz,串口发送速率为115200Hz,同时能够依次发送0到99,100个数据,满足设计要求。

2.2 采样系统精度测试

通过外加电压与高精度电压表测量比较,ADC128S052实际测量误差在0~3.3V的电压输入范围内最大为0.0219V内。如表1所示为8个通道对3个模拟电压的测试结果。第一列为基准电压,后8列分别为采样结果。根据测试得出,该数据采集系统的测量误差在0.0219V以内,因此将该系统用于多通道的A/D采样与数据传输具有灵活性强,精度高,误差小等特点。

3 结语

利用Verilog HDL设计A/D多通道数据采集与串口发送系统,不仅通过Modelsim仿真软件验证功能,同时经AC620开发板测试,将采样数据与实际电压比较,分析整个系统的性能。结果表明,该系统不仅完成了数据采集和串口发送数据到上位机的功能,而且该系统具有采样误差小、精度高等特点,具有相当大的实用价值。

参考文献

[1] 易志强,韩宾,江虹,等.基于FPGA的多通道同步实时高速数据采集系统设计[J].电子技术应用,2019,45(06):70-74.

[2] 袁玉卓,曾凯锋,梅雪松.FPGA自学笔记:设计与验证[M].北京:北京航空航天大学出版社,2017.

[3] 王永云.基于FPGA的多通道数据采集系统的设计[D].廊坊:北华航天工业学院,2018.

[4] 王华刚,邓志燕,董鹏飞.多功能多通道数据采集系统设计与实现[J].自动化与仪器仪表,2016(09):36-37.

[5] 谈良,纪凌.基于FPGA的多通道数据采集系统设计与实现[J].电子测量技术,2018,41(05):57-63.