基于FPGA图像采集系统的硬件电路设计

2020-03-31王佳超王思懿李党娟吴慎将吴新宇

王佳超,王思懿,李党娟,吴慎将,吴新宇

(1.西安工业大学光电工程学院,陕西 西安 710021; 2.西安高斯激光科技有限公司,陕西 西安 710032)

0 引言

图像采集系统在人工智能、消防安全、工业检测以及安防监控等领域都有广泛的应用,也越来越受到各方关注。常见的图像传感器件有电荷耦合器件(charge-coupled device,CCD)传感器件以及互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)传感器件两大类,它们各有优缺点[1]。CCD器件噪声低、动态范围广、光照灵敏度高。但CCD光敏阵列难以驱动信号处理电路和芯片集成。固态传感器CMOS可直接输出数字图像信号和数据同步参考信号,方便底层数据处理和集成[2]。CMOS图像传感器有质量轻、体积小等特点,大面积应用于嵌入式图像采集处理系统[3]。与传统的高级精简指令集计算机(advanced RISC machines,ARM)和数字信号处理(digital signal processing,DSP)相比,由于现场可编程门阵列(field programmable gate array,FPGA)具有更快的数据处理速率和更高的使用灵活性等优点,适用于单位时间内处理数据多、需要数据处理速率高的图像处理系统。ARM和数字信号处理(digital signal processing,DSP)是基于软件开发语言C或汇编的嵌入式微处理器,容易移植,可增加外部存储器扩展系统的存储容量,并且与各种总线接口协议,例如集成电路总线(inter integrated circuit,I2C)、通用串行总线(universal serial bus,USB)、控制器局域网络(controller area network,CAN)、串行外设接口(serial peripheral interface,SPI)、通用异步收发传输器(universal asynchronous receiver transmitter,UART)等兼容,广泛应用于控制和数据处理等领域。但这两种处理器的电路结构经厂商生产之后就已固定,用户修改空间较小,且采用串行处理的方式不利于数据量较大的时序控制和处理[4]。因此,现场可编程门阵列作为一项越来越成熟的技术,以其并行性以及灵活性,被广泛应用于图像采集、传输以及处理[5]。

1 系统总体设计

1.1 系统结构

采用型号为OV7670的CMOS图像传感器对实时的图像进行采集和传输,其他模块由搭载Spartan6系列的现场可编程门阵列,通过使用Verilog HDL硬件描述语言的编程实现各个控制模块的功能。采集的图像通过双倍数据率同步动态随机存取存储器(double data rate3 synchronous dynamic random access memory,DDR3 SDRAM)进行缓存,并输送到视频图形阵列(video graphics array,VGA),然后在上位机显示。系统结构如图1所示。

图1 系统结构示意图Fig.1 The schematic diagram of system structure

1.2 系统工作流程

系统结构包括CMOS图像传感器、图像传感器驱动模块、图像获取模块、DDR控制模块、DDR3 SDRAM存储器、VGA输出模块以及VGA显示模块。系统上电之后,FPGA通过I2C协议控制CMOS传感器的内部寄存器,对OV7670图像传感器进行初始化并完成对传感器的配置。由OV7670图像传感器配合图像抓取模块进行捕捉视频流图像;把捕捉的图像信息通过DDR3 SDRAM控制模块写入DDR3 SDRAM内部的先进先出队列(first input first output,FIFO)中;最后将图像通过VGA显示模块进行实时显示[6]。

2 系统硬件电路设计

采用Xilinx公司的开发软件ISE Design 14.7搭建开发环境,联合Modelsim对系统的各个模块进行仿真,完成了整个硬件系统的设计。

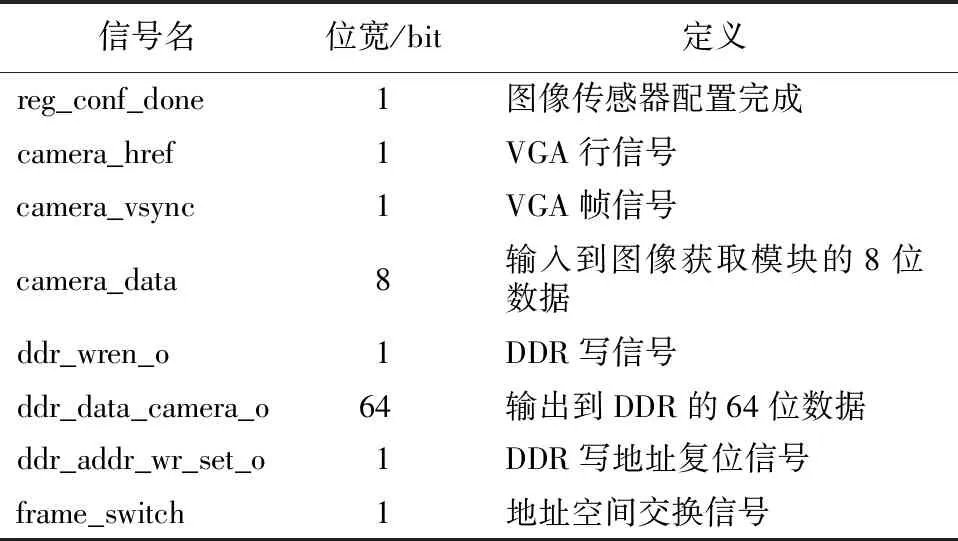

2.1 图像获取模块

图像采集模块由OV7670图像传感器、图像获取模块(camera_capture)、图像传感器驱动模块(i2c_gene)共同组成。其中:OV7670图像传感器可直接写入640×480像素以及16位(红、绿、蓝分别为5位、6位、5位)的图像信息。图像传感器驱动模块通过I2C协议对OV7670的内部寄存器进行写操作,从而完成该传感器的配置[7]。将图像信息存入DDR3 SDRAM的内部寄存器中。由于DDR3 SDRAM的位宽为64位[8],因此要将8位的数据输入转换成64位(8字节)的数据输出。图像获取模块信号定义如表1所示。图像获取模块(camera_capture)产生DDR写入信号(ddr_wren_o)、DDR复位信号(ddr_addr_wr_set_o)、以及地址空间转换信号(frame_switch)。该程序中ddr_data_camera就是由输入的8位转换成输出的64位的像素。当接收到8 B数据时,产生DDR写信号,并把接收到的8 B数据输出给DDR3 SDRAM内部的先进先出(first in first out,FIFO)存储器(FIFO)。如果没有接收到或者接收到的数据不足8 B,那么DDR写信号为低电平且没有数据输出。

表1 图像获取模块信号定义Tab.1 Signal definition of image acquisition module

2.2 DDR控制模块

DDR3 SDRAM内部位宽为64位、深度为64,内部FIFO的容量为512 B。在图像抓取模块(camera_capture)中,产生DDR写地址复位信号(ddr_addr_wr_set)和读写地址空间交换信号(frame_switch),并由这两个信号来控制DDR3 SDRAM的读写。

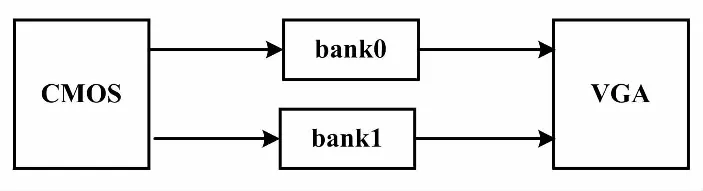

DDR控制模块将从图像抓取模块输入的图像信息先缓存在DDR3 SDRAM内部的存储器中,然后再写入DDR3 SDRAM存储器。如果有输出请求,再把DDR3 SDRAM存储器中的图像信息提取出来,输送给VGA输出模块。DDR控制模块的作用是对DDR存储器进行读写的过程进行控制。在只有一片动态随机存储器的情况下,为了达到显示的实时性和同步性[9],要对该模块中图像数据的传输采用乒乓操作,如图2所示。

图2 乒乓操作示意图Fig.2 Schematic diagram of the Ping-pong operation

关键代码如下:

if(ddr_addr_wr_set) begin

if(frame_switch==1'b0)

c1_p0_cmd_byte_addr<=30'd0;

else

c1_p0_cmd_byte_addr<=30'd1000000;

end

为了确保显示完整的一帧图像,将DDR3 SDRAM内部划分成两个部分(即bank0和bank1)。这两个部分的空间均大于存储一帧图像所需要的字节数。当CMOS OV7670图像传感器初始化完成后,从图像传感器采集到的数据先写入bank0中,同时读取bank1中的数据;读完一帧后,切换到bank0读取数据[10]。这样就可以保证数据的实时性和同步性。

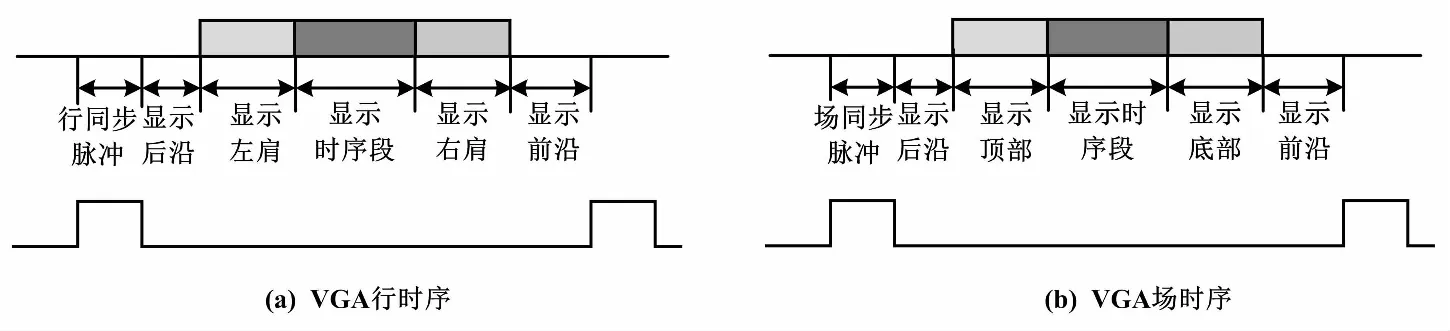

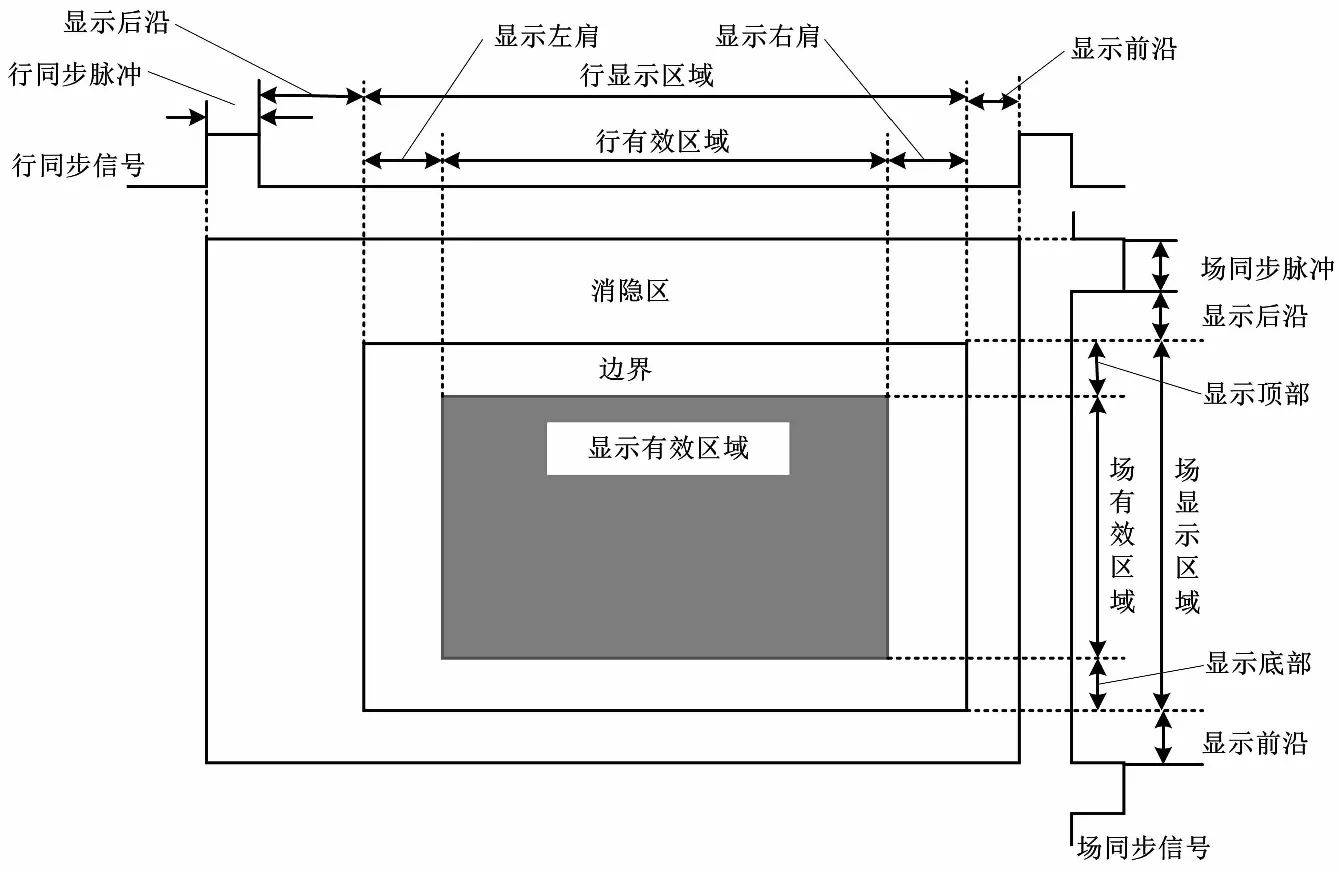

2.3 VGA输出模块

VGA显示共有5个信号:R、G、B三基色信号,行同步信号(HSYNC)和场同步信号(VSYNC)[11]。在本系统中,FPGA产生分辨率为640×480,刷新频率60 Hz的VGA时序,包括行同步、场同步及颜色信号。这些信息经过图像采集模块以及DDR控制模块后,传输到DDR3存储器中。VGA输出模块只需要给DDR发送读命令,就可以将DDR中的图像信息通过VGA显示出来。VGA时序如图3所示,VGA显示如图4所示。

图3 VGA时序Fig.3 Sequence diagram of VGA

图4 VGA显示图Fig.4 The display of VGA

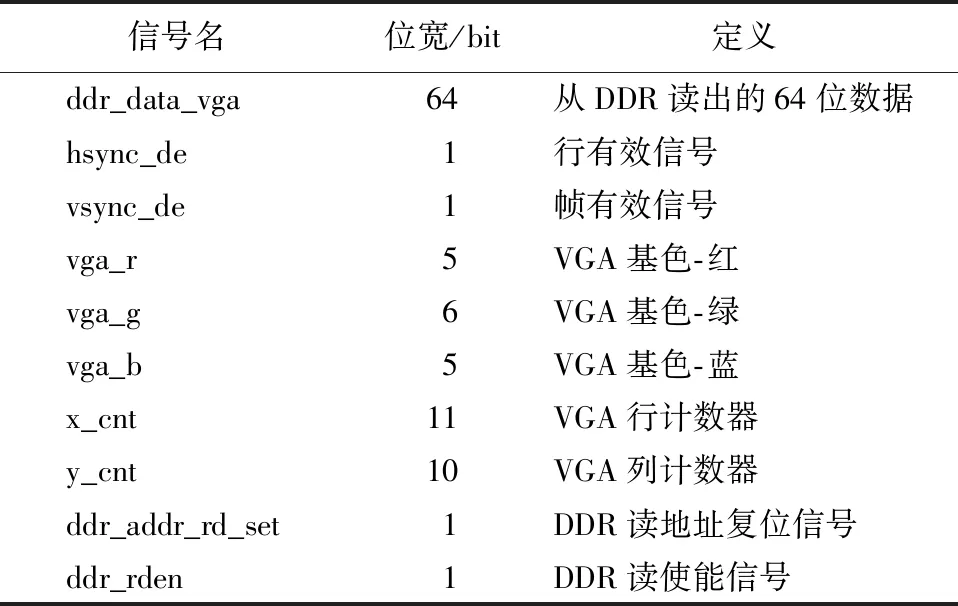

VGA输出模块信号定义如表2所示。该模块产生VGA的帧行信号,行和列的计数,R、G、B三种基色以及读地址复位信号。

表2 VGA输出模块信号定义Tab.2 Signal definition of VGA output module

VGA的显示原理是对每一帧图像的每一行进行逐点扫描。行同步信号标志着扫描一行结束。场同步信号也就是帧信号,它标志着一幅图像的结束。

行、场时序执行如表3所示。

表3 行、场时序执行表Tab.3 Schematic diagram of the line timing execution and field sequential execution

如表3所示,在扫描的过程中需要一定的延时调整,所以出现了消影区,在消影区内没有图像信息。

在VGA显示模块,由于VGA显示16位的像素点,其中RGB分别占有5位、6位、5位。因此要将从DDR内部FIFO的64位数据分四次读入VGA输出模块中。

3 系统功能仿真验证及分析

3.1 图像获取模块仿真分析

CMOS OV7670图像传感器初始化完成(即reg_conf_done信号由低拉高)后,DDR控制模块直接读取DDR中的数据进行VGA显示(此时,VGA显示的第一帧是空白图像)。当检测到camera_vsync延时两拍的上升沿时,frame_switch由低拉高,读写地址空间(bank0和bank1)交换。当camera_href=1且camera_vsync=0时,进行写地址复位。与此同时,图像采集模块开始采集数据,等到camera_vsync再一次由低拉高一帧图像采集完成。检测到camera_vsync信号的上降沿时,地址空间交换信号(frame_switch)拉高一个时钟周期进行地址空间的交换;检测到camera_vsync信号的下降沿时,写地址复位信号ddr_addr_wr_set_o拉高一个时钟周期图像获取模块的程序对DDR写地址进行复位。图像采集模块的主要功能是将输入到该模块8位数据转化成64位数据,并输出给DDR控制模块。

3.2 VGA输出模块仿真分析

VGA输出模块在上电复位之后就进入工作状态,计数器x_cnt和y_cnt分别计行和列的像素个数。由上述两个计数器产生的数据有效信号(hsync_de与vsync_de)控制VGA模块的输出。当hsync_de=1且 vsync_de=1时,VGA输出模块将64位的数据分4次读取到相应的寄存器中,送到上位机由VGA显示。当行数据有效信号(hsync_de)拉低,表示数据传输完成同时将输出给R、G、B 这3个通道的数据全部清零。当帧数据有效信号(vsync_de)拉低,表示一帧图像传输完成。然后,读地址复位信号ddr_addr_rd_set拉高一拍,对读地址进行复位,等待下一帧图像的传输。

4 结论

本文利用FPGA芯片作为逻辑控制的核心器件,采用CMOS OV7670图像传感器进行图像采集,并在上位机由VGA进行实时显示。采用一片DDR3 SDRAM芯片缓存,利用乒乓操作实现图像的写入与读取互不干扰。仿真结果表明,该系统能够较好地满足图像的实时输出的需求。本设计的特点是灵活性高、可移植性强且能够进行实时显示。这将有助于对图像预处理,尤其是图像分析和目标识别的优化,为进一步开发更复杂的图像算法提供借鉴。