基于BEPCⅡ数字束流位置测量系统电子学系统的设计与实现

2020-03-30随艳峰杜垚垚麻惠洲岳军会马宇飞黄玺洋季大恒张醒儿卢艳华王之琢魏书军曹建社

随艳峰,杜垚垚,叶 强,麻惠洲,岳军会,马宇飞,黄玺洋,季大恒,汪 林,张醒儿,卢艳华,刘 芳,王之琢,杨 静,魏书军,曹建社

(1.中国科学院 高能物理研究所,北京 100049;2.中国科学院大学,北京 100049)

BEPCⅡ是2008年建成的“一机两用”的加速器装置,它是粲物理能区的对撞机和高性能同步辐射光源装置。BEPCⅡ稳定运行十余年,在高能物理研究中取得许多重大物理研究成果,并在同步辐射用光等方面发挥重要作用。BEPCⅡ装置的直线、输运线以及储存环中束流位置测量系统(BPM)电子学在建设时采用商用模拟Bergoz产品,由于运行时间已久,故障频发。为保障BEPCⅡ装置未来稳定、可靠运行,需对这些模拟BPM电子学系统进行更新换代[1]。

本文基于该需求开展高性能数字BPM电子学系统研究,开发具有自主知识产权的数字BPM电子学系统,并将其应用于BEPCⅡ装置以及即将建设的国内的其他加速器上。

1 数字BPM电子学系统结构

数字BPM电子学系统,在硬件结构上主要由束流位置探头、射频信号调理模块、数字采样与信号处理器模块、数据服务器等部分构成,而射频信号调理模块和数字采样与信号处理器模块通常被称为BPM信号处理电子学。图1a为BPM系统结构框图,图1b为重心法位置计算说明[2]。其中BPM信号处理电子学是BPM系统的重要组成部分,其性能将直接决定BPM系统设计。

BPM信号处理电子学中射频信号调理模块主要完成BPM信号的增益调整与窄带滤波功能。而数字采样与信号处理器模块则在系统时钟和触发信号控制下完成信号的ADC采样与数字信号处理,并在FPGA数字信号处理模块中获取4通道信号的幅度信息,进而通过重心法计算束流的位置信息。

2 数字BPM电子学设计与实现

本文所设计基于BEPCⅡ的数字BPM电子学系统采用MTCA.4架构。数字BPM的信号处理电子学结构和功能框图如图2所示,主要包括两部分电路,一部分是位于RTM板上的模拟前端电子学(AFE),主要完成信号的幅度调整和频率滤波功能;另一部分电路是位于AMC板上的数字前端电子学(DFE),主要完成信号采集、数据处理与传输等功能。其中,数字BPM算法逻辑在AMC电路的FPGA内实现。

BEPCⅡ的高频频率为499.8 MHz,储存环有对撞模式和同步模式两种工作模式。在对撞模式下工作时,高频谐波数为396个,其回旋频率fr=1.262 1 MHz;在同步模式下工作时,高频谐波数为402个,其回旋频率fr=1.243 3 MHz。设计中将回旋频率作为系统的参考时钟(即机器时钟,MC)输入,用于产生数字BPM处理器的采样时钟和主工作时钟。本文仅以同步模式为例对系统设计进行介绍。

图1 数字BPM原理图Fig.1 Principle of digital BPM

图2 数字BPM信号处理电子学结构和功能框图Fig.2 Frame and function block of signal processing unit in digital BPM

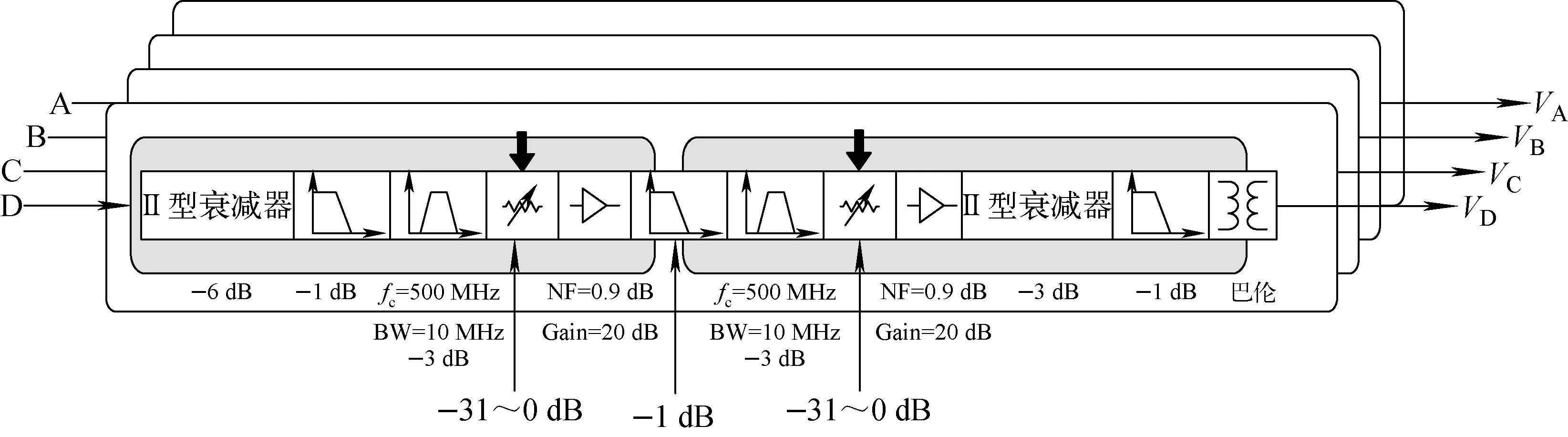

2.1 射频信号调理电子学设计

数字BPM射频信号调理电子学部分位于RTM板上,主要完成信号的滤波和信号的幅度调整功能。信号滤波将滤除(500±10) MHz以外的其他频率成分,而信号幅度调整则实现将(500±10) MHz的载波信号调整到ADC的合适输入范围内,其功能框图如图3所示,图中NF为噪声系数,BW为带宽,Gain为增益。

信号对500 MHz载波信号的固定放大倍数为40 dB;固定衰减为18 dB,固定衰减逻辑包括Π型衰减器、低通滤波器、带通滤波器的衰减;可调衰减为62 dB。该电子学的全部增益可调整范围为-40~22 dB,可接收处理-60~10 dBm的输入信号。

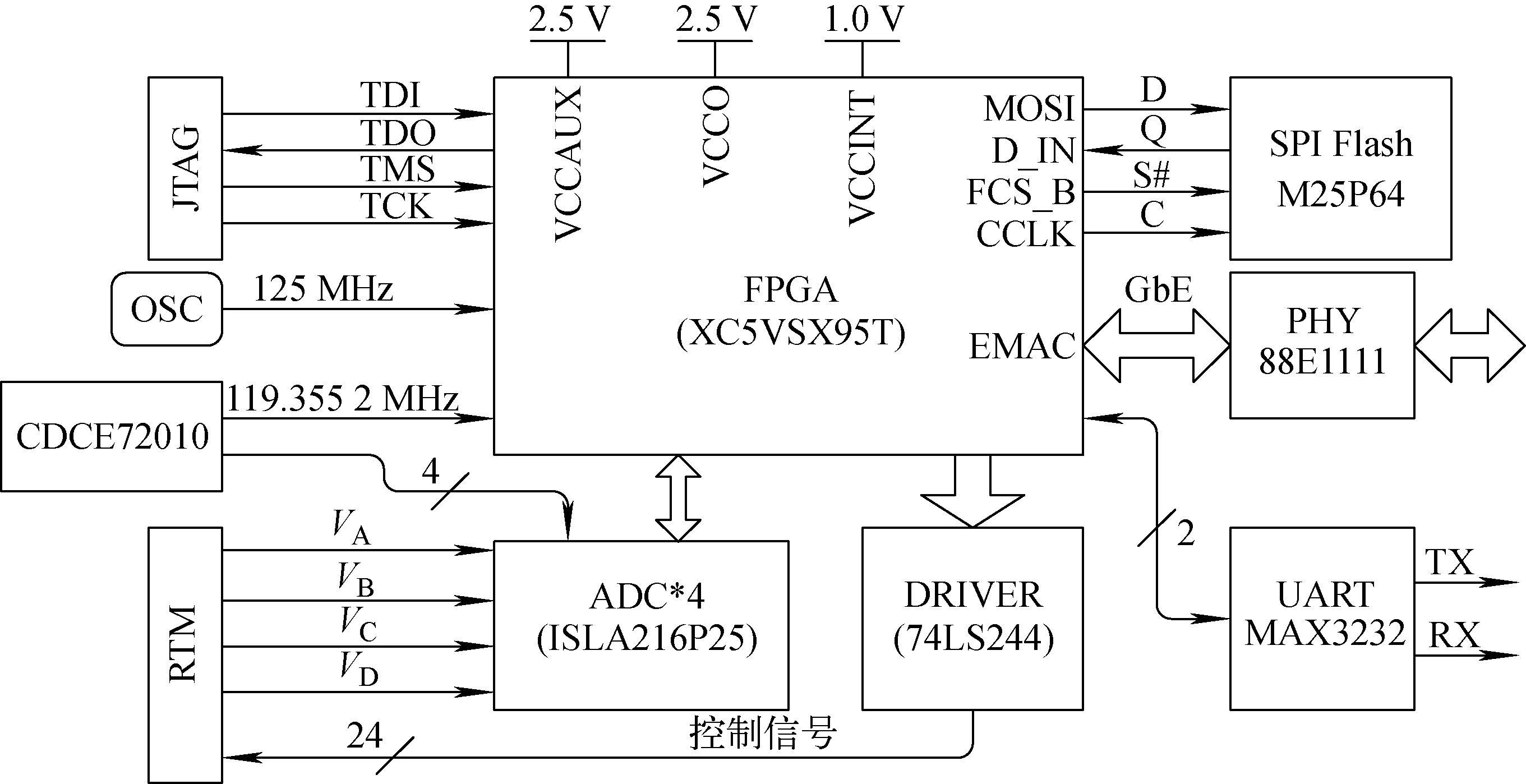

2.2 数字采样与信号处理电子学设计

数字BPM数字采样与信号处理电子学位于AMC板上,主要完成模拟信号的ADC采样、数据处理、数据传输功能。其功能框图如图4所示,该电子学接收来自RTM射频信号调理电子学的差分信号,经巴伦和阻抗匹配电路送入到ADC完成4路BPM信号的模数转换,转换后的数据送至FPGA并在FPGA内实现束流位置的计算,位置信息经千兆网、UDP协议传输至数据服务器。

数字BPM电子学系统的主控制FPGA采用Xilinx公司的Vertex5芯片XC5VSX95T-1FFG1136C,其接口原理框图如图5所示。JTAG接口用于对FPGA和SPI Flash加载程序,同时也用于在调试阶段利用Chipscope工具进行逻辑调试;125 MHz时钟晶振用于RTM控制、主时钟逻辑配置以及网络数据传输控制(EMAC)等功能,CDCE72010为FPGA和ADC提供主工作时钟;ADC接口包括ADC配置接口和数据接收接口,其中数据接收接口为DDR_LVDS标准;对RTM板的控制共有24个信号,实现对RTM上8个数字衰减器的控制。另外,FPGA还设有异步通信接口,用于与计算机数据通信的冗余设计。

图3 数字BPM射频信号调理电子学功能图Fig.3 Schematic of radio frequency singal conditioning electronics in digital BPM

图4 数字BPM数字采样与信号处理电子学功能框图Fig.4 Function block of signal sampling and data processing in digital BPM

图5 数字BPM FPGA接口原理框图Fig.5 FPGA interface scheme of digital BPM

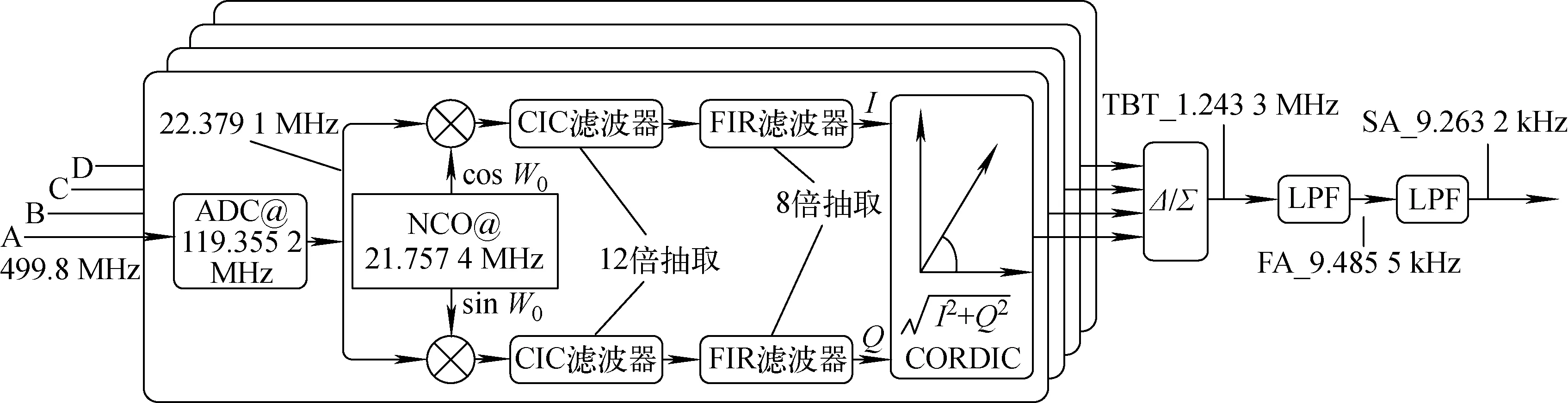

3 数字BPM算法设计

算法逻辑是数字BPM电子学系统设计的核心内容之一,本文设计BPM算法采用传统DDC算法,其结构框图如图6所示。499.8 MHz载波信号经119.355 2 MHz时钟采样后,数据频率变为22.379 1 MHz,该数据与数字本振(numerically controlled oscillator, NCO)产生的21.757 4 MHz两路正交信号混频后得到中心频率为621 kHz数据信息,再经CIC和FIR滤波抽取到回旋频率(1.243 3 MHz)。其中,CIC滤波器采用CIC的IP核实现;FIR滤波器则利用FDATOOL工具设计实现;滤波后的数据经CORDIC计算出信号的幅度。4路幅度信息经差和比计算出束流的逐圈位置(turn by turn, TBT)信息,然后再经滤波抽取获取位置的快信号(FA)和慢信号(SA)。FA位置信息由TBT位置数据经128倍抽取滤波获取;SA位置信息由FA位置数据经1 024倍抽取滤波获取。在BEPCⅡ中,由于无快轨道反馈系统,因此FA数据仅作为系统研究用[3-6]。

4 数字BPM电子学系统测试

BPM电子学测试包括板级测试和系统测试两部分。板级测试内容主要有数字BPM射频信号调理电子学和数字BPM数字采样与信号处理电子学两部分。系统测试则是对数字BPM电子学系统整体进行实验室和在线束流测试。

4.1 数字BPM电子学板级测试

1) 射频信号调理电子学测试

在实验室利用矢量网络分析仪对射频信号调理电子学进行测试,通过测量S21参数测得该电子学在中心频率500 MHz处的带宽为20 MHz。同时对通道的隔离度进行测量,实验方法为在某通道上获取6.5 dBm功率的信号时,测量相邻通道信号方式来获得其隔离度,结果表明通道隔离度大于60 dB。图7a为S21参数测量结果,图7b、c分别为相向方向隔离度测量结果。

图6 数字BPM DDC算法结构框图Fig.6 DDC algorithm function block of digital BPM

图7 射频信号调理电子学带宽和隔离度测量结果Fig.7 Bandwidth and isolation result of RF signal circuit

2) 数字采样与信号处理电子学测试

数字采样与信号处理电子学测试主要通过测试ADC采样数据的性能来完成。原始ADC数据的信噪比,不仅能反映系统采样时钟的抖动,同时也能反映BPM硬件电子学的噪声水平。在对该电路测试时,外部输入时钟频率为1.243 3 MHz,板上VXCO产生的与外部输入时钟同步的ADC采样时钟和主工作时钟,其频率为119.355 2 MHz,被采样信号由信号发生器产生499.8 MHz点频信号。对ADC原始采样数据作FFT处理,其结果如图8所示。测试表明系统ADC在119.355 3 MHz采样频率情况下,其无杂散动态范围(SFDR)约76 dB[7]。

图8 ADC原始采样数据FFT结果Fig.8 FFT result of ADC raw data

4.2 数字BPM电子学系统测试

在完成数字BPM板级功能和性能测试后,在实验室用点频信号、在BEPCⅡ用实际束流对数字BPM系统进行测试。

实验室测试情况为,输入点频频率为499.8 MHz,幅度为0 dBm,BPM位置灵敏度系数Kx、Ky取值为25,在采样点数为500点时(时间长度约40 s),测得系统SA数据的x和y方向位置分辨分别为91 nm和84 nm,测试结果如图9a所示。在时间长度为2 h情况下,测得系统SA数据x和y方向位置分辨约为0.57 μm,测试结果如图9b所示。

图9 实验室位置分辨测试结果Fig.9 Resolution test result in laboratory

图10 BEPCⅡ实际束流位置分辨测试结果Fig.10 Resolution test results of real beam in BEPCⅡ

实际束流测试情况为,BEPCⅡ运行模式为同步-decay模式,流强为250 mA,BPM位置灵敏度系数Kx、Ky取值为25,测试时间为20 h,测得系统SA数据位置结果如图10所示,位置分辨约为3.17 μm。

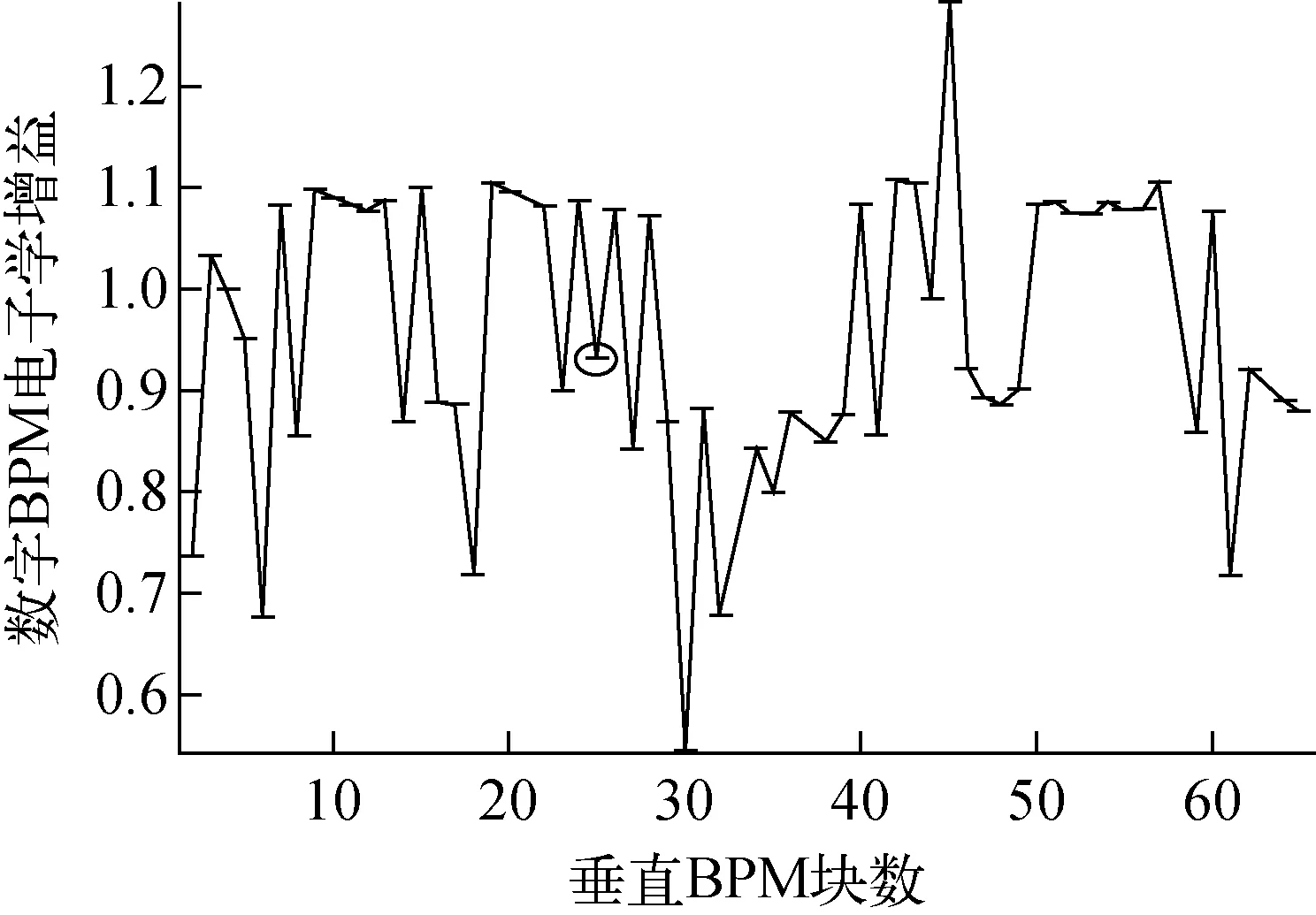

在BEPCⅡ测试中,对实际束流下数字BPM电子学增益进行测量。测试中利用LOCO程序[8],分析实测响应矩阵数据,得到包含数字BPM电子学在内的全环67块BPM的增益(图11),其中数字BPM电子学增益为0.93,误差小于10%,与其他BPM电子学的增益接近,满足BEPCⅡ在线测量和运行的需求。

图11 数字BPM在BEPCⅡ中的响应矩阵Fig.11 Response matrix of digital BPM in BEPCⅡ

5 结论

本文基于BEPCⅡ设计数字BPM电子学系统,包括硬件电路设计、算法程序设计、系统测试等多个内容,为一系统性工程设计。本文所研制的单套数字BPM电子学系统已在BEPCⅡ储存环上试运行半年,其测量分辨由原Bergoz产品的5~10 μm提升至优于100 nm水平[9],其测量分辨和系统稳定性均已达到预期的设计目标。

数字BPM测量电子学系统是束流测量的核心内容之一,设计难度大,指标要求高。数字BPM的成功研制及稳定试运行,一方面为采用自研数字BPM批量更新BEPCⅡ储存环上的BPM电子学系统提供了可能,另一方面,也为未来在高能光源以及在高能环形正负电子对撞机项目中应用自研数字BPM电子学系统创造了条件。