八通道X波段射频数字一体化接收机设计

2020-03-28

(中国电子科技集团公司第三十八研究所, 安徽合肥 230088)

0 引言

有源相控阵雷达在波束扫描、系统损耗以及功率合成等方面具有优势,可以扩展机载雷达的功能,提高雷达性能,从而在机载平台上的重要性日益提高[1]。机载平台在载荷、空间、功耗等方面要求较高,但在很多传统的雷达接收机设计方案中,射频接收通道与ADC采集分为两个模块实现,利用射频电缆互连,形式较为复杂,空间利用率有限。因此,接收机在高集成、低功耗、小型化等方面的改进是有必要的。

本文介绍了一种X波段八通道射频数字采集一体化集成的设计方案。该设计属于机载有源相控阵体制雷达中低功率射频单元的一部分,可将有源天线子阵合成后的多通道窄带回波射频信号在一个基于标准ASAAC结构的插件内部完成模拟变频、数字解调、数据采集和融合处理。设计可将传统方案中的射频、低频电缆简化为板级印制线互联,在降低损耗的同时极大地优化了系统的集成性、重量和体积等性能,并提高了电路制造的可靠性。

1 电路设计实现

1.1 整体设计概述

八通道X波段窄带射频数字采集一体化模块的主要功能是接收子阵合成后的回波射频信号,经过变频、采集和解调之后形成多路窄带I/Q信号,最大带宽模式为80 MHz。其设计要点在于:

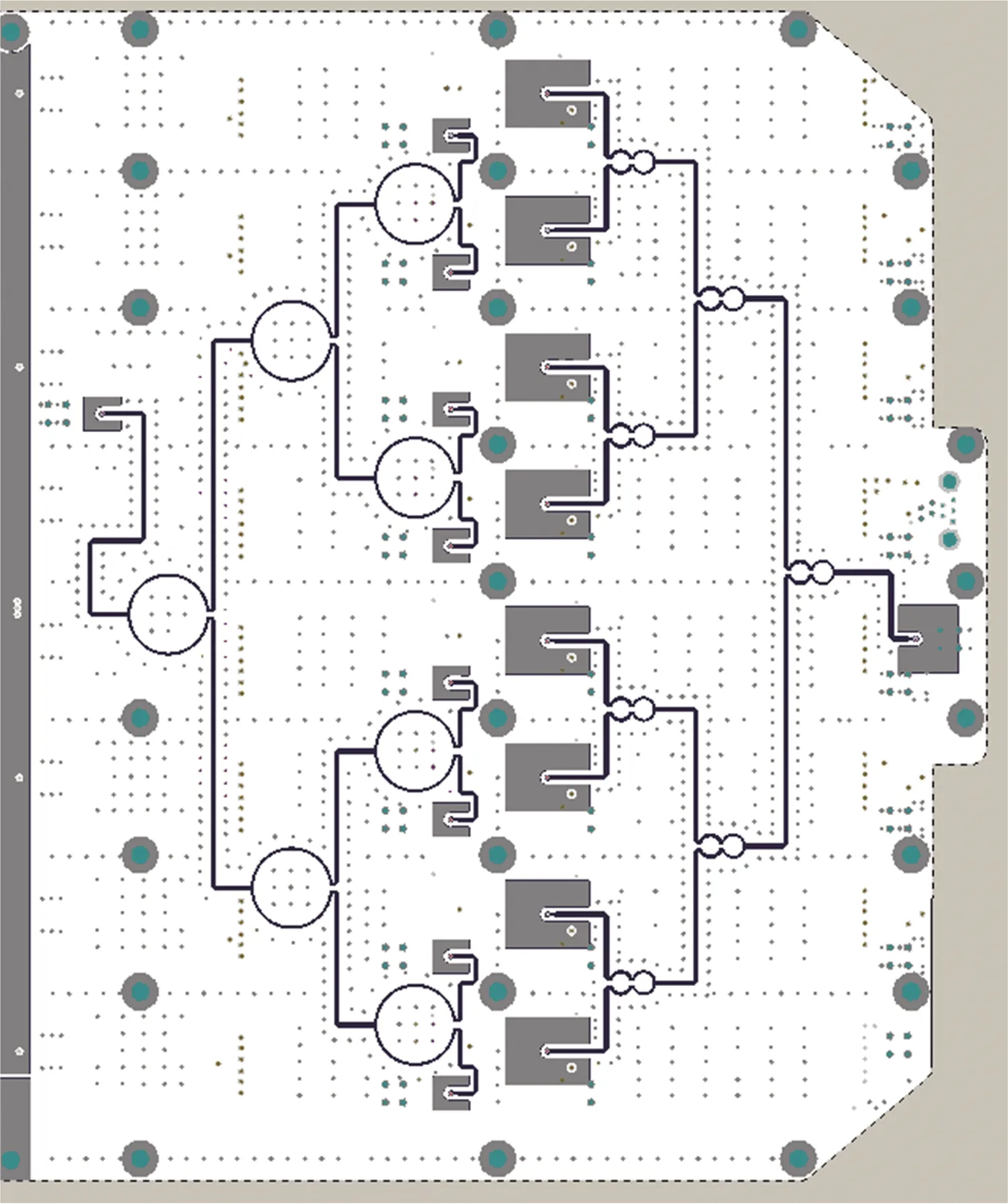

1) 解调体制设计选择。考虑技术成熟性,解调体制采用模拟二次变频加中频数字采样实现。为降低窗口选择的难度、避免低次互调,设计时将X波段划分为等频宽的4个子带进行全频段覆盖,同时每个子带有一定带宽的频率重叠以保证滤波器相位特性。采用二次变频将射频信号混频至中频信号,进行ADC中频采样。其中一本振为X/Ku波段跳频本振,二本振为S波段固定点频本振。

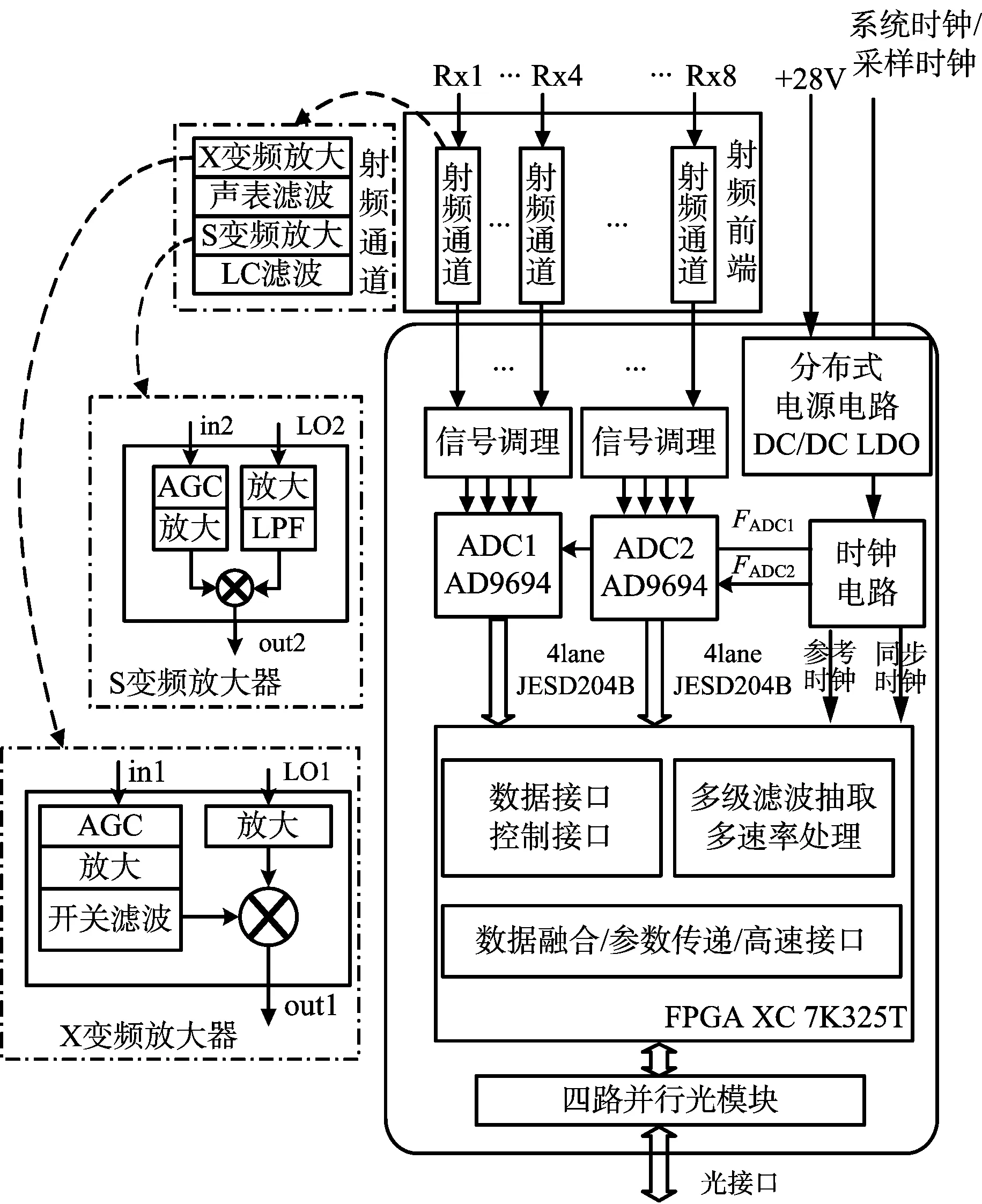

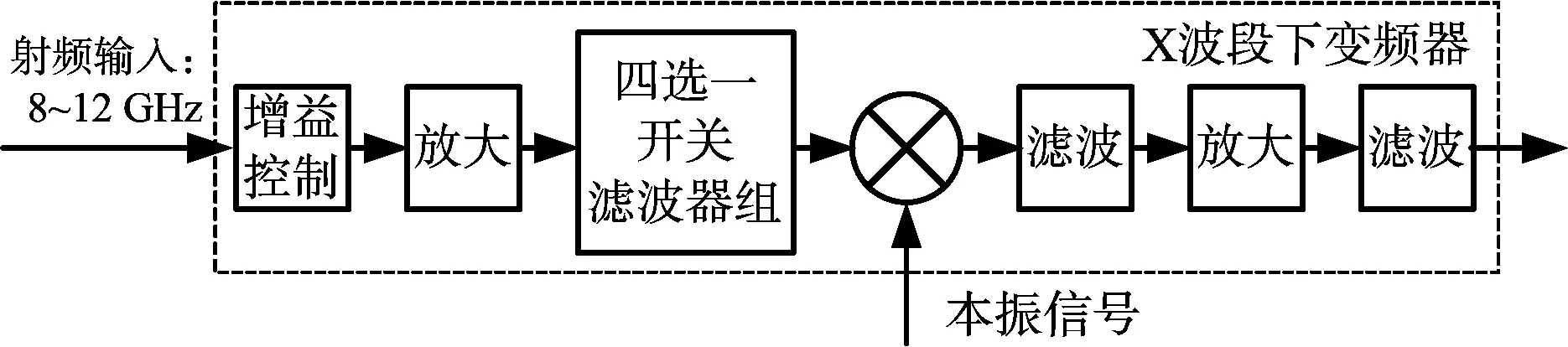

2) 射频、模拟、数字集成设计方案。八通道X波段射频数字一体化模块需要将射频变频接收链路、本振网络和数字接收链路集合在同一个6U ASAAC尺寸的PCB载板内部,其功能框图如图1所示。电路设计在实现方案、系统互联、布局分配等问题上都面临严峻的考验。

图1 射频数字一体化设计功能框图

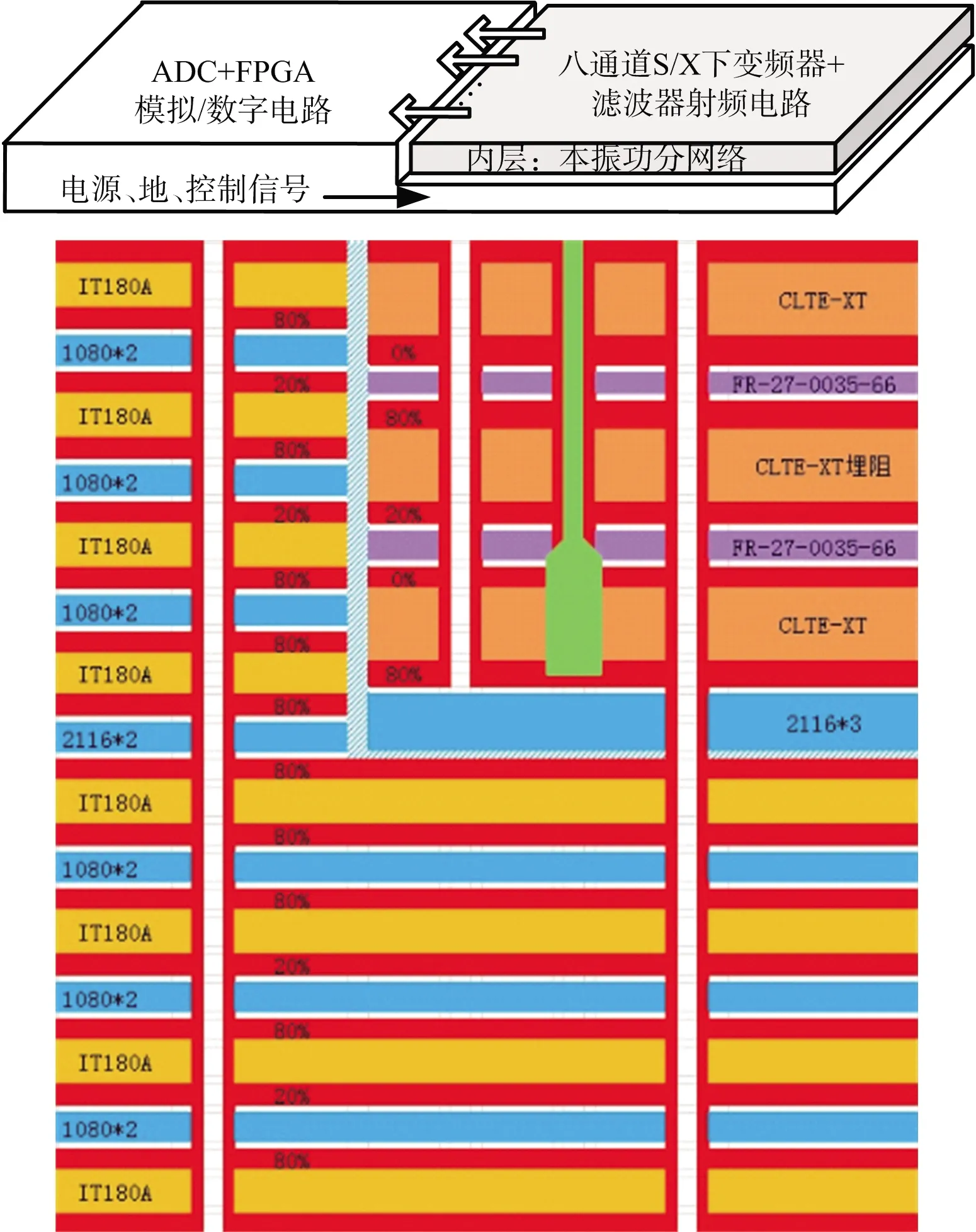

考虑到降低射频、数字电路互连的复杂度,提高集成性,采用如图2的方案进行PCB设计。电路板右侧上方为射频电路部分,表层为射频变频放大通道,内层嵌入本振功分网络,采用CLTE-XT加工;模拟/数字部分(主要包括ADC、FPGA、电源等)设计为台阶形状,并通过靠下的叠层向右边射频部分提供控制信号和电源。射频通道至模拟/数字电路的八通道信号通过表层微带线传输。

图2 射频/模拟/数字一体化设计互连情况

设计的主要考虑包括:

1) 合理规划叠层、分割平面:保证每个信号层的独立地回流平面,保证电源平面与地平面相邻、降低电源平面阻抗。模拟和数字电源/地层合理分区,保证JESD204B链路信号回流完整的情况下弱化数字信号对模拟信号的干扰。

图3 接收通道隔腔结构设计

2) 接收通道分腔设计。通过ASAAC结构设计8个接收通道的金属腔,对通道前后级和通道之间进行隔离,如图3所示。通道间金属隔腔对应的PCB板位置裸露接地金属表面,二者接触部分安装时加注导电胶,有效增强隔离度、降低互耦干扰。

1.2 功分网络设计

很多早期的雷达系统中,多通道接收机的多路本振信号都需要由频率源产生后首先传输给一个独立的本振功分模块,再由其功分输出至各通道接收前端[2]。随着系统集成度的要求逐渐提高,功分网络的设计也需要进行改进。采用多层微带板电路、利用带状线在介质板内部布线形成Wilkinson功分器是一种有效的优化设计方案[3]。Wilkinson功分器的工作原理是在简单功分器中引入隔离电阻,变为有耗网络,从而保证信号链路的匹配和隔离度。

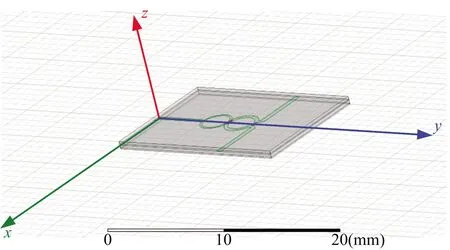

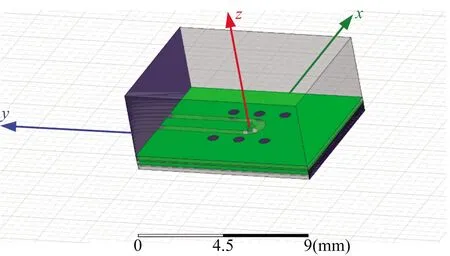

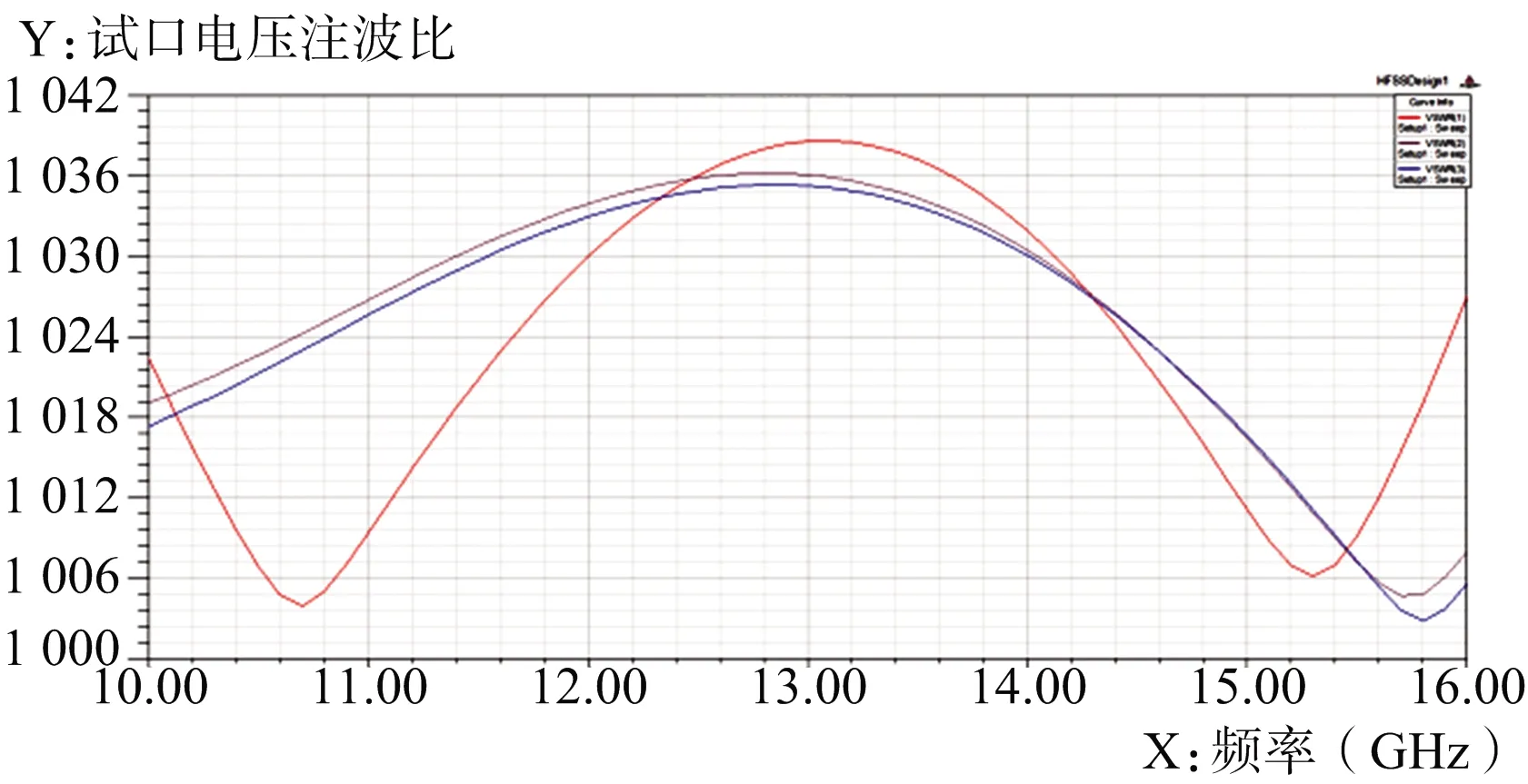

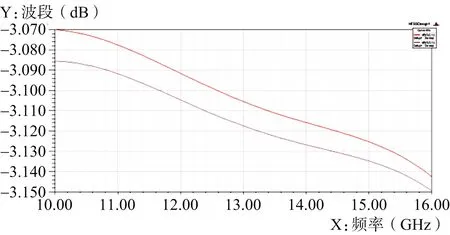

本设计中,二次变频的本振信号分别为X/Ku波段变频信号和S波段点频信号。设计时,首先采用HFSS优化仿真出S波段和X波段的1-2功分器以及本振网络与变频器管脚垂直过渡连接的模型(图4(a)、(b)以X波段模型为例)。1-2功分器的电压驻波比和网络插损仿真结果如图4(c)、(d)所示。

将上述单节功分器仿真的S参数导入至ADS软件中,建立1-8功分器仿真模型并进行仿真和优化,最终得到如图5嵌入PCB内层的S波段(左)和X波段(右)功分网络带状线。

(a) X波段1-2功分器仿真模型

(b) X波段1-2功分器仿真(垂直过渡)

(c) 电压驻波比仿真结果

(d) 网络插损仿真结果图4 功分网络HFSS仿真模型及结果

图5 本振功分网络图形

Wilkinson功分器的隔离电阻采用Ohmega-ply镍合金材料薄膜式埋阻。设计时结合网络仿真结果和材料方阻率,通过特殊的蚀刻工艺将镍合金材料层上的铜箔清除,得到符合要求的埋阻图形。

1.3 模拟接收设计

模拟链路设计包括二次变频和滤波实现。考虑到通道数目灵活性和小体积高集成化需求,二次变频采用基于3DSiP微系统集成方式的通用模块设计。滤波功能由片外独立器件完成。

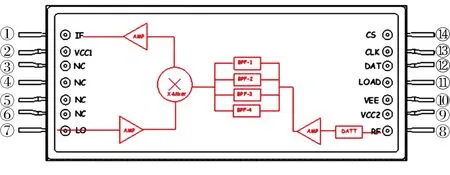

X变频接收模块通过四选一开关滤波器实现4个子带的选择,通过跳频本振将输入频率固定为一中频频率输出,并带有AGC数控功能。其内部链路和实物图片如图6所示。

(a) X波段变频接收内部链路示意图

(b) X波段变频接收模块内部结构框图

(c) X波段变频接收模块实物图图6 X波段变频接收模块内部链路示意及实物图

X变频接收模块内部集成了部分芯片滤波器。考虑到带外抑制指标要求,采用抑制度高的声表滤波器实现一中频滤波,其带宽为100 MHz。声表滤波器满足带外抑制≥40 dB@fc±110 MHz,插损≤3.5 dB,带内起伏≤2.0 dB。

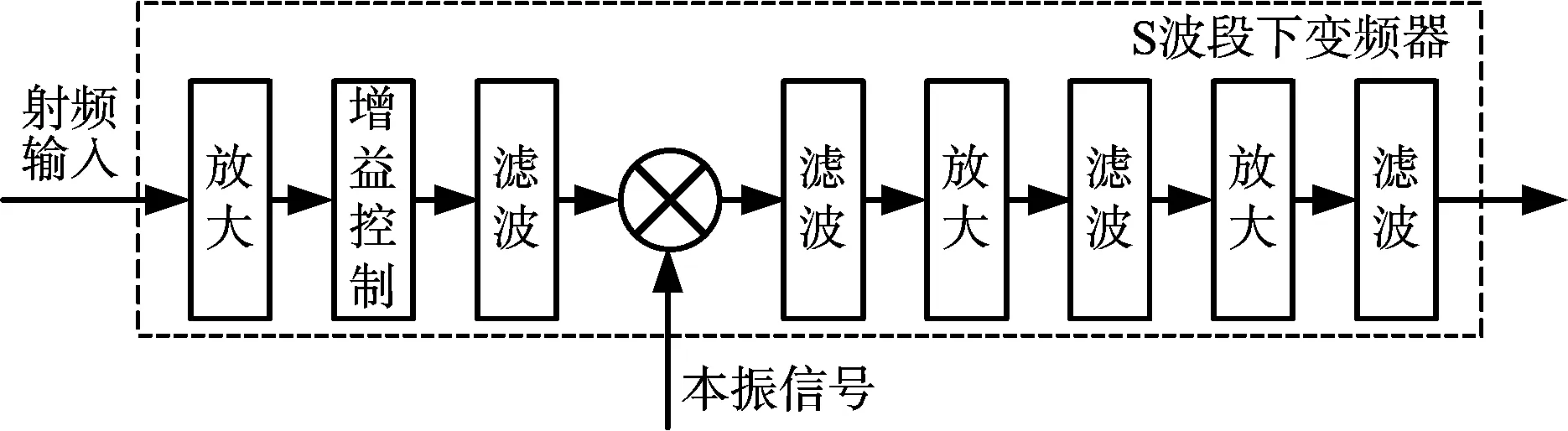

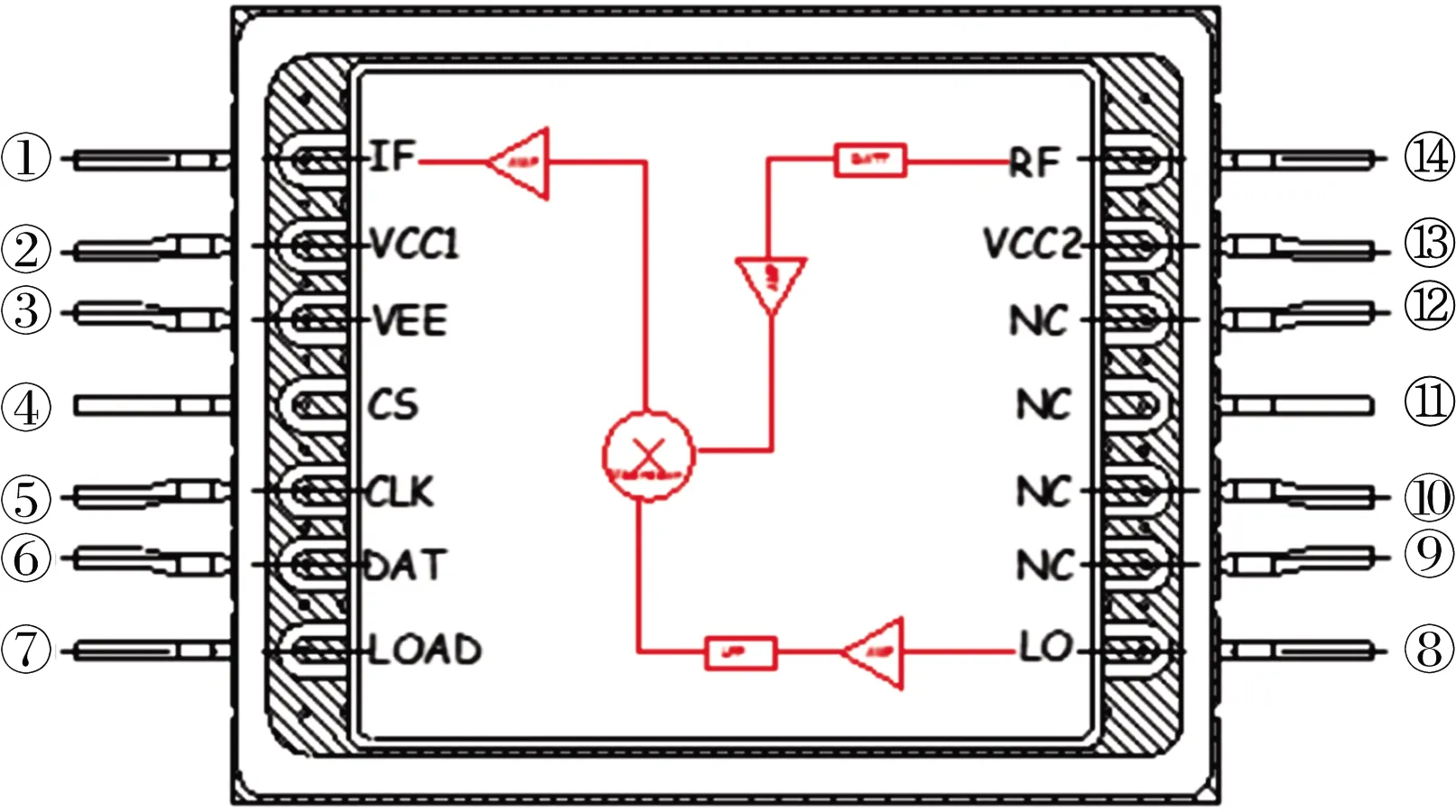

S变频接收模块由固定的二本振频率将输入的一中频变频为确定频率的输出中频。根据带宽、增益和噪声系数需求,得到如图7(a)链路设计方案;功能示意图和实物图如图7(b)、(c)所示。

(a) S波段变频接收内部链路示意图

(b) S波段变频接收模块内部结构框图

(c) S波段变频接收模块实物图图7 S波段变频接收模块内部链路示意及实物图

二中频输出采用3D封装、小体积高可靠性的LC滤波器滤波,可达到≥50 dB@fc±110 MHz的带外抑制指标,并在插损、幅相起伏、一致性、驻波等方面都具有良好的性能,满足链路设计需求。

1.4 数字接收电路设计

数字接收电路以FPGA为核心,控制ADC芯片实现八通道下变频接收,并将基带信号按照不同带宽进行滤波处理、按照协议将回波数据打包传输。根据系统要求的中频信号频率以及带宽要求,结合最佳采样定理,采样率可设置为320 Msps。ADC选择ADI公司的四通道芯片AD9694。AD9694芯片可通过JESD204B接口与FPGA进行通信,由FPGA通过SPI接口进行工作模式配置。根据其典型参数,在满刻度1.8Vp-p模式-3 dBFs输入下,载频610 MHz以下SFDR大于81 dBFs、SNR大于67 dBFs,符合系统需求。JESD204B接口subclass1类需要sysref信号进行同步,为保证两片ADC在每次上电时满足各通道采样点同步,需对FPGA扇出的sysref信号进行处理,设计并约束路径等长,确保采样时钟沿对sysref信号足够的建立和保持时间[4]。

由于系统应用要求信号带宽具有5种模式,需根据不同带宽进行滤波处理。FPGA选型主要基于高速接口资源(包括用于光纤通信的5 Gbps接口以及ADC 6.4 Gbps速率的JESD204B接口)和内部级联滤波器消耗的资源,最终确定为XC7K325T-2系列芯片。

电源系统的处理为采集电路的关键因素,对电路的指标有决定性作用。电源系统采用DC/DC与LDO相结合、分布式逐级稳压输出产生,并在考虑效率、热耗的条件下预留充足裕量,满足数字电路大电流、模拟电路低纹波、无开关频率杂散的需求。

根据上述电路设计思路,电路板实物装配图如图8所示。

图8 电路板实物装配图

2 数字下变频滤波实现

FPGA逻辑功能包含射频前端控制、外部芯片配置控制以及数据滤波处理和传输。其中,采集功能的核心部分是多通道多带宽多速率抽取滤波设计。

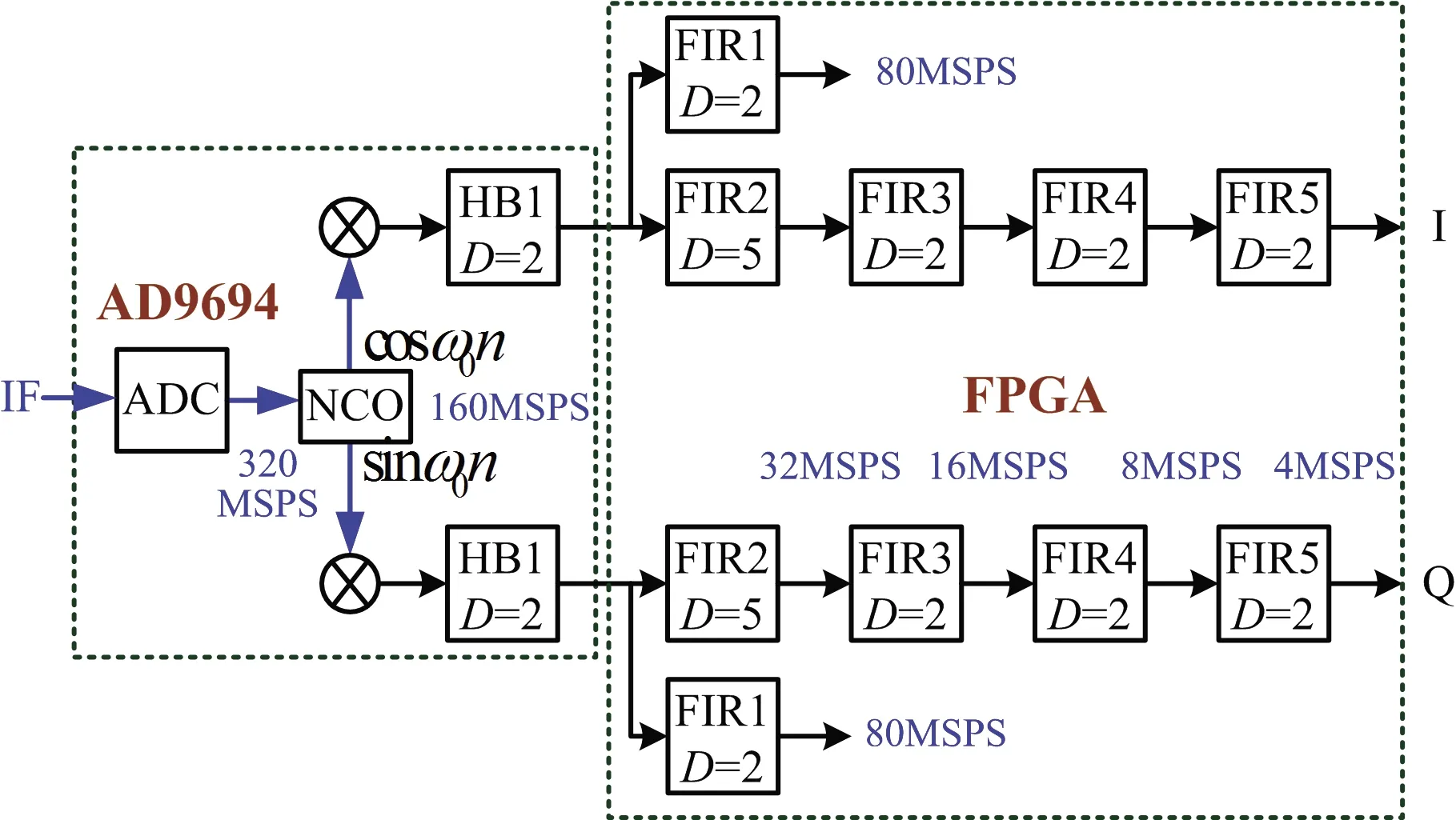

根据设计需求,可利用AD9694内置的fs/4IF DDC模式进行下变频至基带I/Q信号。在320 Msps采样率下,ADC输出等效为I和Q分别为160 Msps采样。该工作模式下调用了ADC内部的半带滤波器抑制带外干扰并进行混频增益补偿[5]。下变频后的I/Q数据通过JESD204B接口送至FPGA,通过系统需求的不同带宽决定级联抽取方式[6]。每级抽取对应的滤波器系数通过Matlab仿真得到,滤波器调用Xilinx K7系列内部的ip core实现。其功能框图如图9所示。

图9 DDC及多速率滤波方案

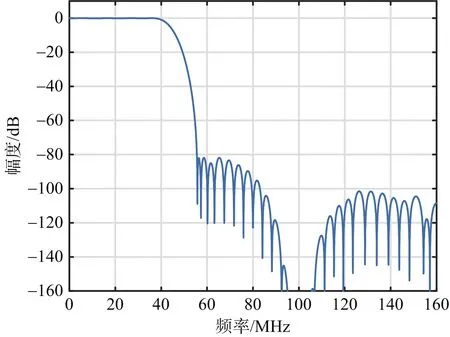

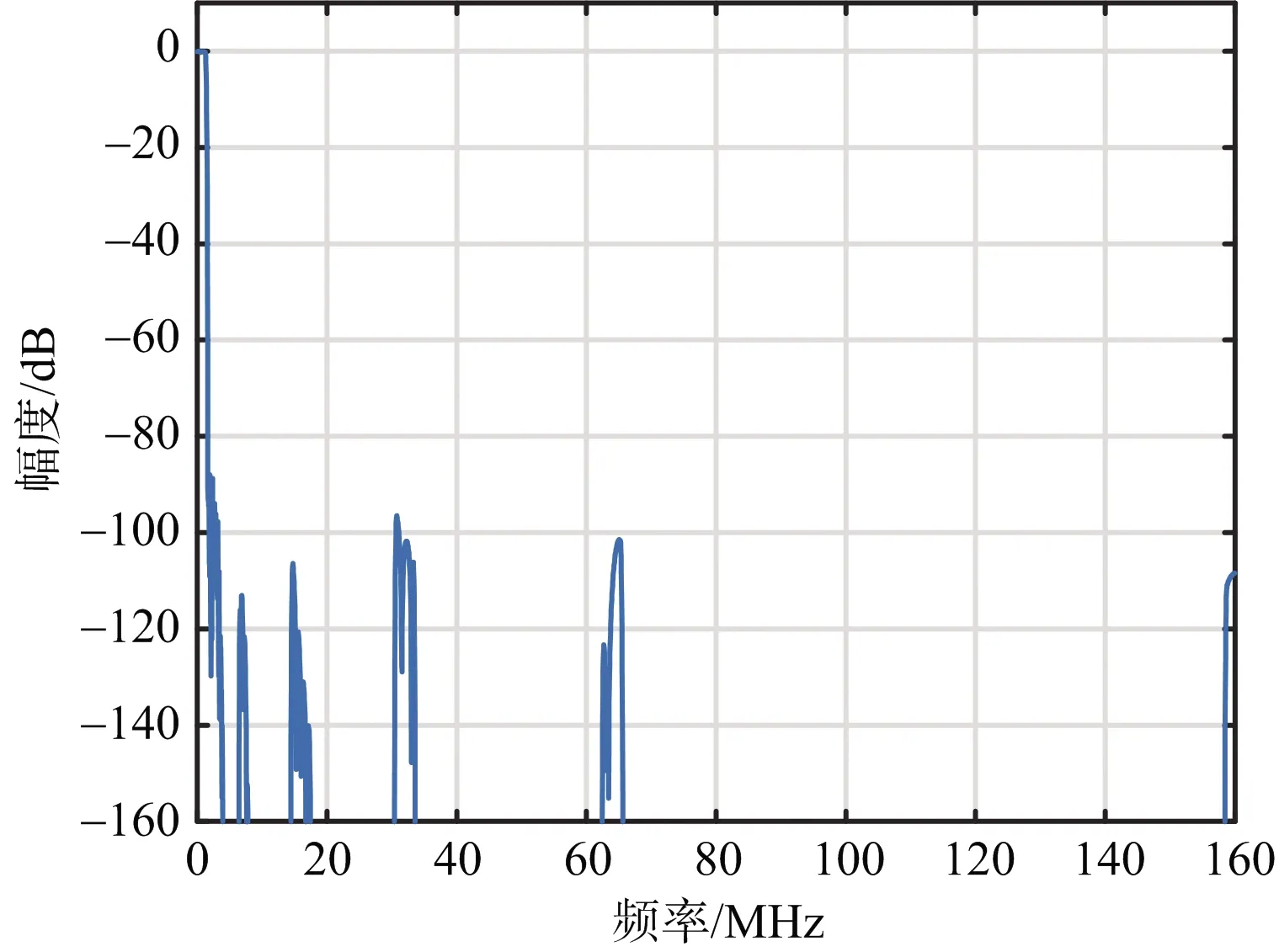

级联滤波器仿真结果示例如图10所示。

进行RTL级代码实现后,编写testbench将理想的点频和线性调频采样数据作为多速率滤波器功能模块的输入,得到各级滤波器输出的RTL仿真结果并导入到Matlab中分析,可同时验证所设计滤波器的性能和代码实现正确性。

(a) 80 MHz带宽级联滤波器仿真

(b) 2.5 MHz带宽级联滤波器仿真图10 80 MHz和2.5 MHz带宽级联滤波器仿真结果

3 测试结果

一体化接收机的测试由信号源提供覆盖X波段范围内的待测点频信号。测试系统中采用一个频率产生模块产生电路板所需的系统时钟、采集时钟和本振信号,并保证各时钟同源。

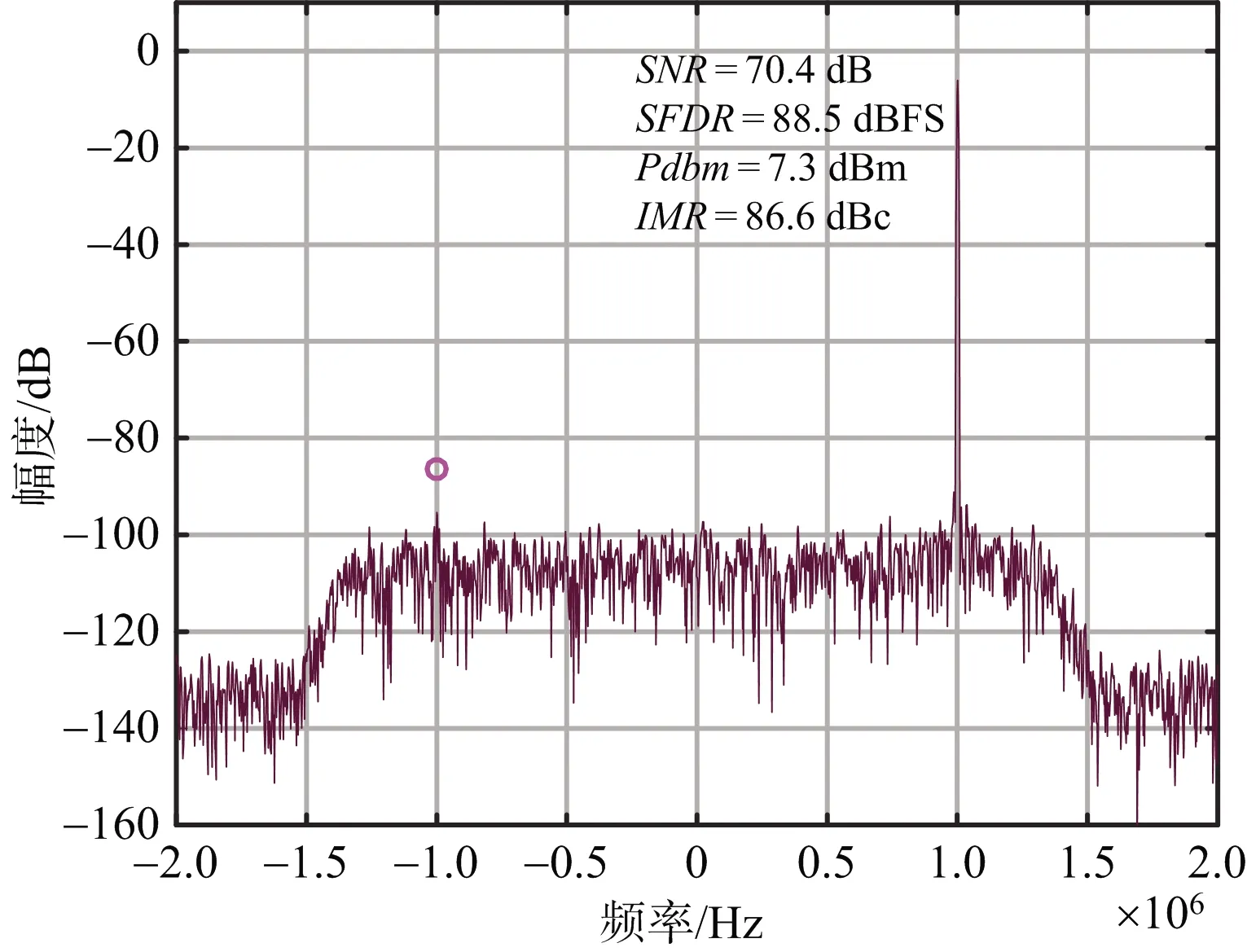

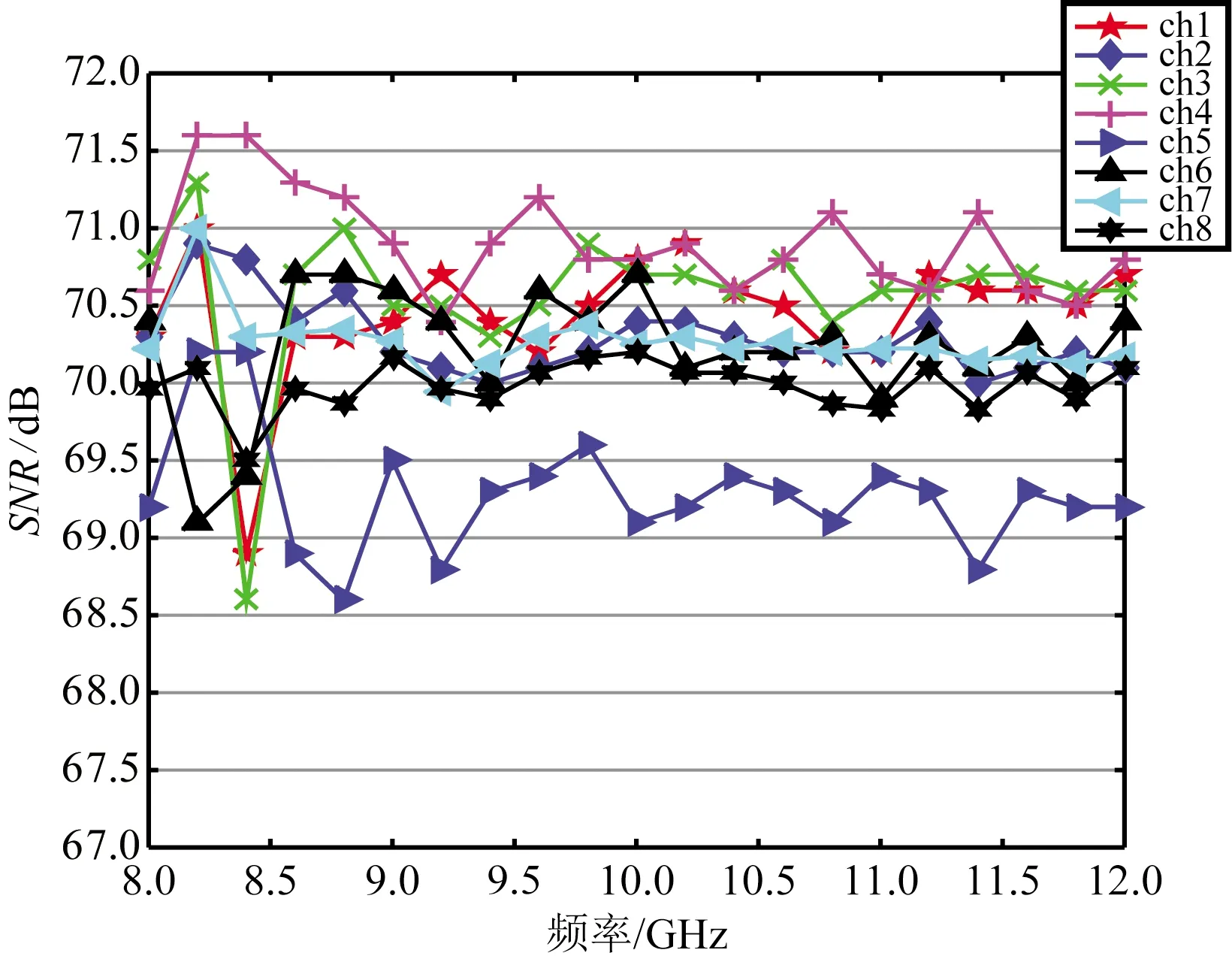

在2.5 MHz带宽下测量通道的瞬时动态范围结果如图11、图12所示,满足瞬时动态范围好于68 dB。

图11 单通道SNR测试结果

图12 多通道全频段范围内SNR结果

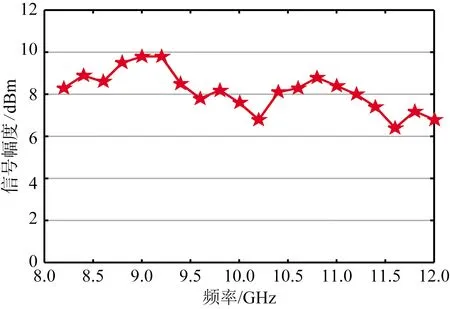

单通道在覆盖X波段范围内的幅度起伏如图13所示,在全段范围幅度起伏小于3.5 dB。

图13 单通道全频段范围内幅度起伏

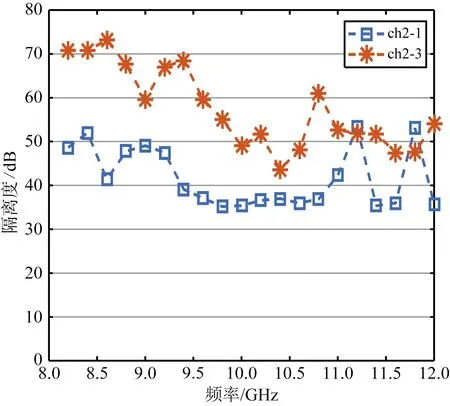

某通道与其临近的两通道在覆盖X波段范围内的隔离度如图14所示,全段好于35 dB。

图14 某通道隔离度测试结果

4 结束语

本文给出了一种机载有源相控阵雷达体制中X波段八通道射频数字一体化集成的设计方案,包括其实现体制和架构、硬件方案设计仿真、DDC及多通道滤波处理设计实现,并给出了实测结果。该设计已应用于多个机载有源相控阵雷达平台,且其实现方式对射频数字一体化设计具有重要的借鉴意义。