基于1553B总线的编解码器设计与实现

2020-03-24柏正兴

柏正兴 邓 晶

(苏州大学 电子信息学院 江苏 苏州 215006)

1553B总线,全称为飞行器内部时分命令/响应式多路数据总线,是美国关于数据总线电气特性和协议规范的一种航空串行总线标准,拥有突出的灵活性及可靠性等性能,在航空航天、舰船等平台上应用时间最早,也最为持久[1].随着国际上对 1553B 总线研究的深入,研制出了1553B 协议专用协议芯片,如 INTEL 公司的 M82553,DDC 公司的ACE 系列产品以及 ACTEL研发的1553BBC等[2].而目前国内使用的1553B芯片绝大多数是从国外进口,但是集成化程度不高,且核心技术受限,价格非常昂贵[3].

对此,国内的一些单位也开展了针对1553B 协议芯片的研究.在研发的过程中,较为关键的部分是对 1553B协议芯片的编解码器的设计[4],本文就在研究了1553B协议规范的基础上,设计了一种基于1553B协议的可靠的编解码器.为后续1553B协议的IP核设计打下坚实的基础.最后对所设计的编解码器进行了仿真测试.

1 1553B数据传输特点

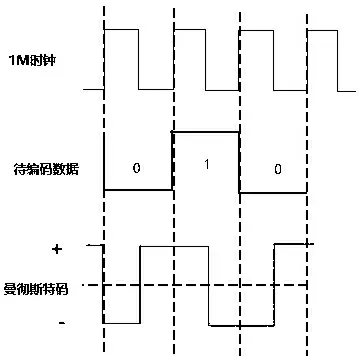

1553B数据总线以异步、命令/响应方式执行数据信息的传输,其通信方式采用半双工方式[5],数据传输速率是1 Mb/s,它遵循曼切斯特Ⅱ型码规则[6].将逻辑0用编码01来表示,其中0和1各占0.5 us,即用一个由低到高的跳变来表示;将逻辑1用编码10来表示,其中1和0各占0.5 us,即用一个由高到低的跳变来表示,它包含了自身的时钟特征,可以直接从数据中分离出定时时钟[7],曼彻斯特Ⅱ型数据编码格式如图1所示.

图1曼彻斯特Ⅱ型数据编码格式

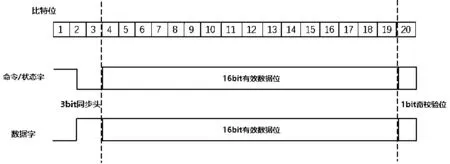

根据1553B总线标准,总线上的传输的消息分为三种类型的字:命令字、 数据字和状态字[8],如图2所示.每一种字类型都对应唯一的格式,但三种字类型的数据结构相同[9].每个字共有20 bit, 起始的3 bit是同步字头,标志新字的开始,同步字头是无效的曼彻斯特码,因为其跳变仅发生在第二比特的正中间[10].接着的16 bit是数据/命令/状态位,三种类型的字有不同的定义[11].最后1 bit是该字对16 bit数据字的奇偶校验位,协议标准规定为奇校验[12].

图2 1553B总线三种消息字类型

2 编解码器设计

编解码模块设计包括曼彻斯特上线编码和下线解码[13].上线编码即对 16 位的命令/状态字或数据字进行处理,包括同步头加载,奇校验位填充,然后对20位的消息字进行曼彻斯特编码再经并串转换发送到总线上;解码即是编码的逆过程,接收数据总线发来的串行数据流,进行串并转换,同步头检测,数据解码及奇校验错误检测[14].

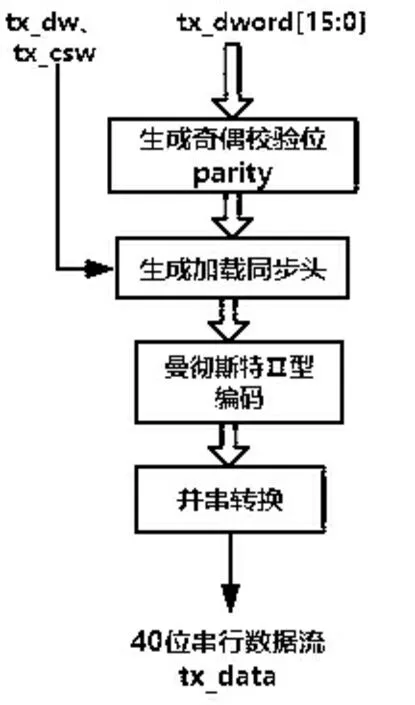

2.1 编码器设计

编码器完成的主要功能有生成加载同步头,产生奇偶校验位,对消息字进行曼彻斯特Ⅱ型编码,并串转换.

编码器设计中采用2 MHz的时钟,根据1553B的数据传输速率是1 Mbit/s这一点,计数2个周期下传输一个比特数据.编码器的具体原理框图如图3所示.对应的编码过程如下:在接收协议层协议处理器发来的16 bit并行数据后,便生成对应的奇偶校验位,接着根据两个同步头控制比特位的高低电平状态来生成对应的3 bit同步头,此时共3 bit+16 bit+1 bit=20 bit的消息字,再经曼彻斯特Ⅱ型编码,并串转换得到40位待发送到数据总线上的串行数据流.编码器设计的原理框图如图3所示.

图3编码器原理框图

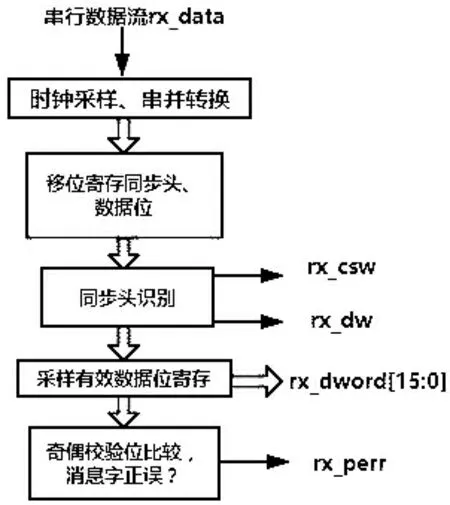

2.2 解码器设计

解码器的主要功能是将1553B总线上的串行输入数据转换为并行数据,并检查数据的奇偶校验位是否正确,为将数据传入1553B的协议处理器做准备.

设计中解码器采用8 MHz时钟进行采样,1553B总线上的数据速率是1 Mbit/s,根据奈奎斯特采样定理,能够保证采样过程的稳定.在时钟的上升沿进行采样,因此,输入的每位串行流对应4 bit的采样值.

解码的具体过程如下:首先是对同步头进行检测,在8 M采样时钟下将前24 bit分离出来,可以作同步头识别,确定消息字的类型是命令/状态字还是数据字.接着进行16 bit数据位和1 bit奇偶检验位的转存,先判断数据的有效性,即通过比较每3/8周期和7/8周期的采样值,只要结果不等,可以认为此比特数据位有效,再根据曼彻斯特Ⅱ型编码的规律,将7/8周期采样值取反,通过移位寄存进相应的寄存器里.最后将解码得的17 bit的数据前16位作为解码结果输出,并通过对原奇偶校验位与解码结果的奇偶校验值进行逻辑比较,如果相等,则结果正确,将结果错误标志位拉低,否则将其拉高,以标志消息字的正确性. 解码器的原理框图如图4所示.

图4解码器的原理框图

3 实验结果仿真验证

在ISE的集成编译环境中,使用Verilog HDL语言[15]完成编解码器设计,编写对应的测试脚本文件[16],首先调用与ISE联合的Modelsim 仿真工具通过Wave窗口观察各设计过程接口信号的测试结果[17],最终下载到目标FPGA开发板上进行验证.

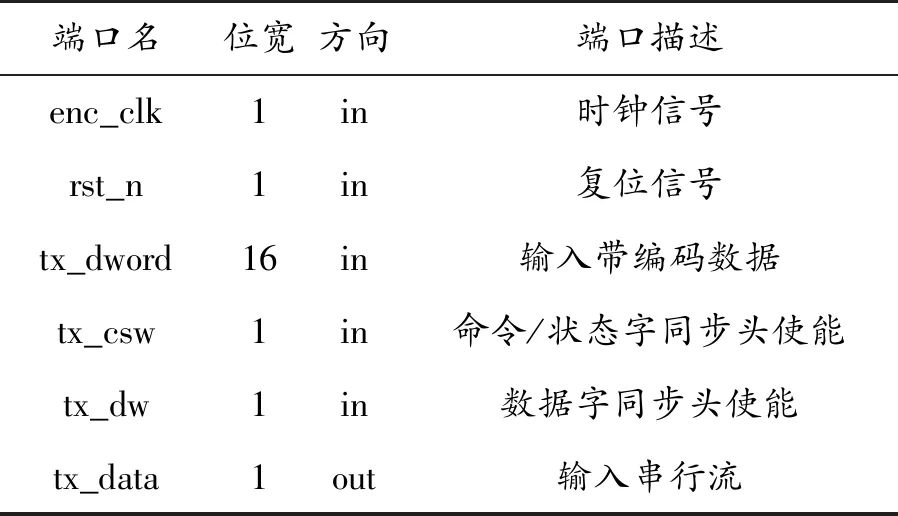

编码器设计中部分主要接口信号如表1所示.

表1 编码器的主要输入输出信号

端口名位宽方向端口描述enc_clk1in时钟信号rst_n1in复位信号tx_dword16in输入带编码数据tx_csw1in命令/状态字同步头使能tx_dw1in数据字同步头使能tx_data1out输入串行流

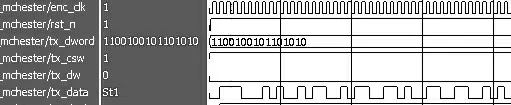

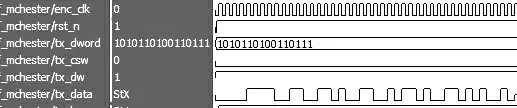

用设计的编码器分别对状态/命令字16’b1100100101101010和数据字16b’1010110100110111进行编码仿真,仿真结果时序图分别如图5、图6所示.

图5编码器时序仿真图(状态/命令字)

图6编码器时序仿真图(数据字)

由图可以看出编码器实现了协议字的曼彻斯特Ⅱ型编码并进行了并串转换.编码结果通过tx_data接口观察,结果显示正确.

解码器设计中主要通过采样和移位操作完成16 bit数据位和1 bit的奇偶校验位的寄存.

解码器设计中部分主要接口信号说明如表2所示.

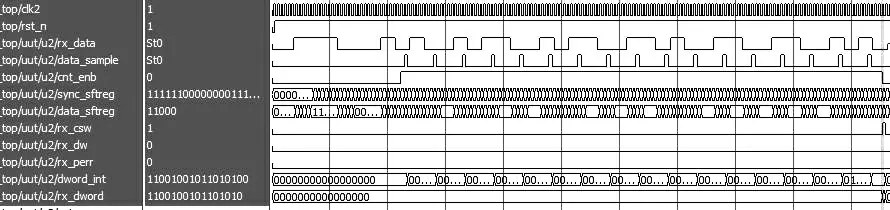

用该解码器分别对数据字16b’0011100110101101和命令/状态字16’b1100100101101010进行解码,仿真结果时序图分别如图7、图8所示.

由仿真结果可知,解码器对命令/状态字,数据字的解码结果正确,功能实现.

表2 解码器的要输入输出信号

端口名位宽方向 端口描述clk21in时钟信号rst_n1in复位信号rx_data1in输入待解码串行流rx_dword16out输出解码数据rx_csw1out解码出的命令/状态字标志位rx_dw1out解码出的数据字标志位rx_perr1out奇偶校验正误标志位

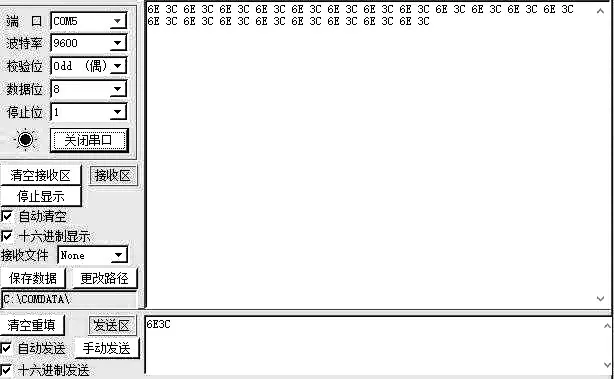

最后将设计程序下载至Spartan6系列的XC6SLX9平台上进行验证.将PC机作为内部数据模拟收发器,借助串口数据收发功能进行简单的闭环验证,设计思路框图如图9所示.串口收发数据测试结果如图10所示.由图10的数据测试结果可知,数据收发结果一致,编解码器的功能设计通过.

图7 解码器时序仿真(命令/状态字)

图8 解码器时序仿真(数据字)

图9硬件验证结构框图

图10串口数据收发验证结果

4 结论

本次设计的编解码器作为1553B总线物理层的主要功能模块,具有同步头加载、检测,奇偶校验,串并/并串转换,错误检测的逻辑接口功能.采用Verilog HDL硬件描述语言在ISE14.7的集成开发环境中进行了逻辑功能设计输入和最终的时序功能仿真,并最终下载到FPGA开发板上且验证通过,完成了1553B总线协议编解码器的数据编码与解码的设计目标,为后续协议层IP核设计及各终端节点通信的实现打下坚实的基础.