基于国产化DSP的雷达信号处理软件设计

2020-02-03喻荣梅李涛吕潇君

喻荣梅 李涛 吕潇君

(南京电子技术研究所 江苏省南京市 210039)

1 引言

近年来,战场环境日趋复杂,雷达信号处理技术飞速发展,对信号处理软、硬件提出了更高要求。同时,随着中美贸易战升级,实现装备自主可控迫在眉睫。由我国全自主研发的高性能华睿2 号DPS 芯片[1-2],具备实时性、灵活性等优点,满足雷达信号处理功能、性能需求。

本文将介绍一种基于华睿2 号国产化平台的雷达信号处理信号处理软件,该软件架构灵活、基础构件跨平台通用、运行效率高。

2 国产化处理平台

华睿2 号DSP 是面向嵌入式高性能计算的处理器,该DSP 内部集成了8 个异构处理器核,包括4 个向量DSP 核和4 个可配置专用处理核,向量DSP 核兼容MIPS64 指令集。华睿2 号信号处理模块包含四片华睿2 号DSP,FPGA、RapidIO 交换芯片、PCIe 交换芯片和网络交换芯片各一片,以及存储器、外围接口电路和电源模块等。模块主要性能指标如下:

(1)最高工作主频为800MHz,峰值运算能力达409.6 GFlops;

(2)每片华睿外接两通道DDR3,DDR 传输率800MT/s,单通道容量4GB,板载内存总容量32GB;

(3)支持x4 模式RapidIO 交换互连,模块对外提供4x4RapidIO接口,单通道速率可达5Gbps;

(4)具备网络交换互连,对外提供4 路x1 SGMII 千兆以太网接口;

(5)提供两路I²C 总线接口。

3 信号处理软件设计

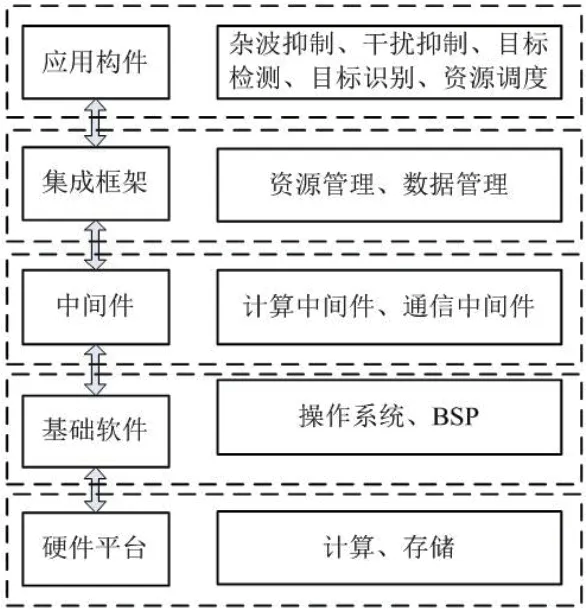

信号处理软件系统基于软件化雷达设计理念[3-5],采用开放式分层架构设计,系统可分为信号处理应用构件、集成框架、中间件、基础软件以及硬件平台,如图1 所示。

3.1 应用构件

应用构件完成本软件的功能处理,可独立部署、加载与运行,雷达信号处理应用构件包括杂波抑制、干扰抑制、目标检测、目标识别、数据处理等算法功能模块。以数据按通道、脉冲、距离段拆分进行并行处理原则,综合处理效率、算法升级、产品跨领域通用的需求,采用灵活可控的构件颗粒度划分,支持即插即用。

图1:信号处理软件分层架构

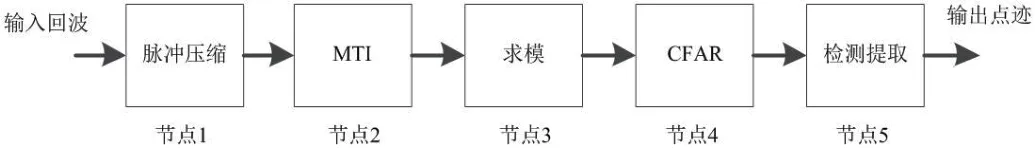

图2:串行处理架构示意图

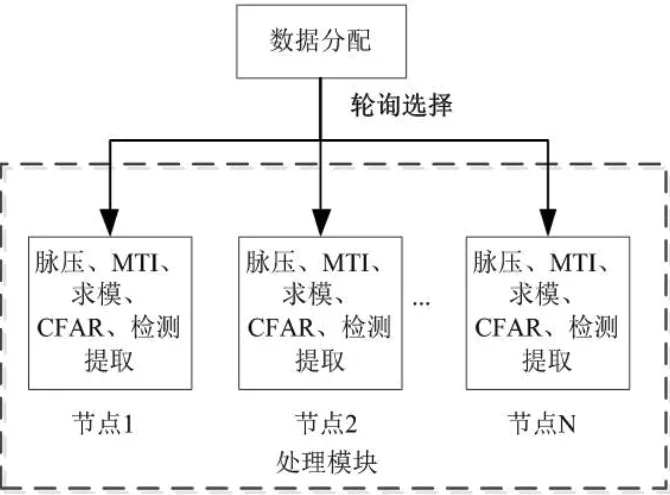

图3:轮询处理架构示意图

3.2 集成框架

集成框架上承信号处理应用构件,下接跨操作系统跨平台中间件,其主要功能包括:

(1)硬件资源管理、各处理节点资源配置;

(2)软件资源管理,包括软件任务资源配置、数据管理、状态监测等。

本文从两方面进行集成框架并行设计:

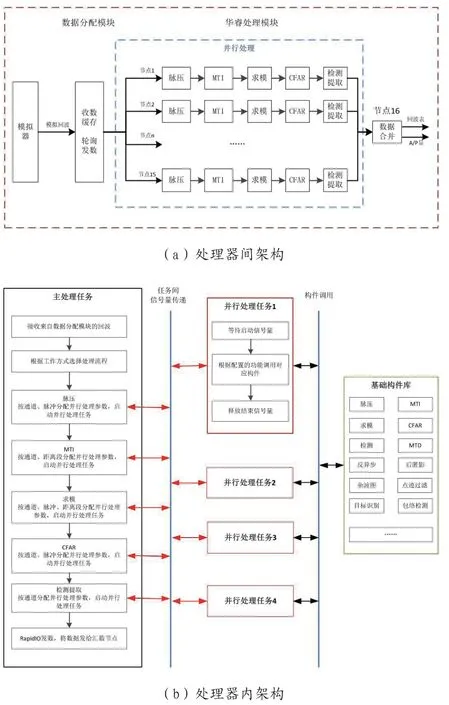

(1)处理器间并行设计。

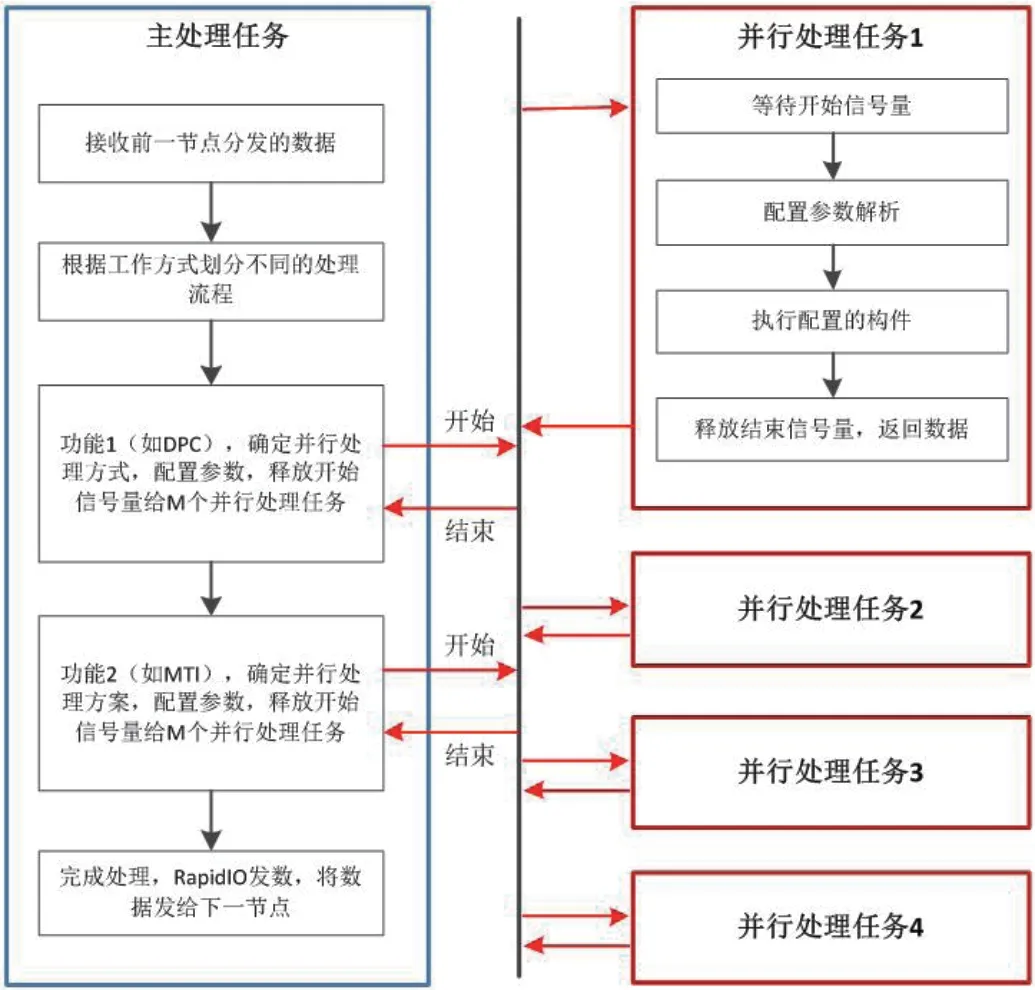

图4:处理器内并流处理流程图

图5:信号处理系统平台组成

传统实时信号处理架构采用处理节点间串行处理架构,如图2所示,其中每个DSP 处理器为一个处理节点。该架构制约了信号处理功能升级、软件重构,且难以保证各处理节点均匀的执行效率加大了系统处理延时,而随着系统复杂度提升,串行节点随之增加,导致系统稳定性大大降低。本文采用基于处理节点轮询机制的并行处理架构,如图3 所示,由数据分配模块完成数据分发,所有处理节点独立执行相同的信号处理任务,该方案满足系统可重构、易升级、易维护的应用需求。

(2)处理器内并行设计。

信号处理平台正向着多核趋势发展,因此需考虑充分利用多核资源,有效提高系统运行效率。华睿2 号具备4 个向量核,核间可采用以下方式处理:

①任务级串行,即每个核绑定一个不同的处理任务,每个任务完成一个或多个信号处理功能,任务间以数据流为驱动串行执行,类似于处理节点串行方式,该方法受制于处理时间不均匀增大处理延时,且不利于系统重构、升级;

②任务级并行,每个核绑定一个相同的处理任务,任务间并行处理不同通道、脉冲数据,该方法优于①,但在功能升级方面不够灵活;

图6:信号处理软件架构

③构件级并行,每个核绑定一个相同的处理任务,每个任务执行多个信号处理功能,由主处理任务针对当前数据特点,将数据按通道、脉冲或距离段尽可能均匀地进行划分,分配给各任务执行。

本文采用第三种方法完成处理器内多核并行处理。创建主处理任务和并行处理任务,其中主处理任务完成数据管理等功能,根据数据特点划分并行处理颗粒度,按需选择并唤醒相应数量并行处理任务执行功能处理;并行处理任务为通用处理任务,绑定在不同的核上独立运行,通过解析主任务输入的参数,从基础构件库选择当前配置的构件完成功能处理,随后将结果返回主任务;主任务与并行处理任务间通过信号量实时通信。核间并行处理流程如图4 所示。

3.3 中间件

中间件通过标准软件接口向集成框架和应用构件提供服务,屏蔽硬件底层环境,实现软硬件解耦。采用基于国际标准VSIPL(Vector Signal Image Processing Library)的计算中间件[6],形成了跨平台通用的基础构件库。

3.4 基础软件

表1:实测结果

基础软件为应用提供软件运行环境,主要包括实时操作系统、驱动/BSP 等。华睿2 号支持国外WindRiver 公司的vxWorks,国内中电32 所的ReWorks、翼辉公司的SylixOS 等操作系统,本文基于SylixOS 操作系统[7-8]完成设计。

4 基于华睿2号处理平台的信号处理软件实现

4.1 信号处理系统平台搭建

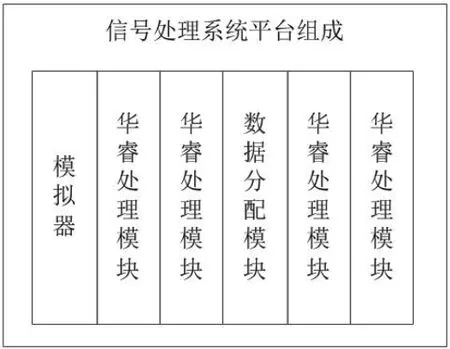

基于华睿2 号模块搭建信号处理系统平台,硬件组成如下:

(1)4 块华睿2 号处理模块;

(2)1 块数据分配模块;

(3)1 套回波产生模拟器;

(4)1 个调试插箱。

信号处理系统组成如图5 所示。

4.2 信号处理软件实现

雷达信号处理主要完成杂波抑制、干扰抑制、目标检测、目标识别等功能[9],本文设计信号处理流程包括脉冲压缩、MTI、求模、CFAR、检测提取。处理架构如图6 所示,4 块华睿处理模块共16个DSP 处理器,其中15 个DSP 用于并行处理,1 一个DSP 用于数据合并。模拟器产生模拟雷达回波,数据输入数据分配模块,数据分配模块根据各处理节点的忙闲状态,完成数据的轮询分发,各并行处理节点完成功能处理后将数据发送到合并节点,合并节点完成视频、回波发送。

4.3 实测结果分析

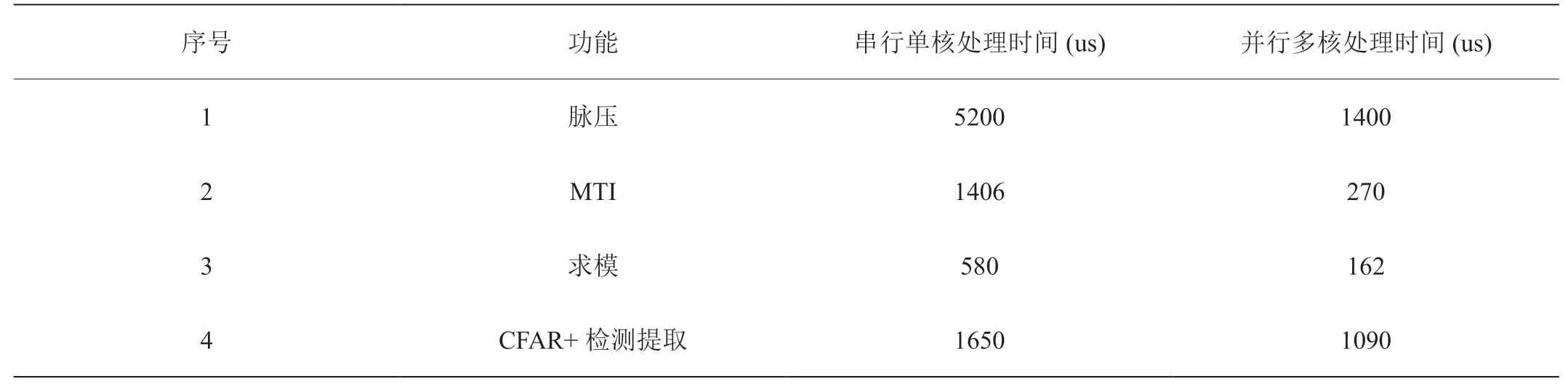

设定模拟器产生MTI 工作方式模拟回波。处理器内架构分别采用串行和构件并行方式,以4 核处理为例,测试结果如表1 所示。

实测结果显示,多核并行处理总处理延时为2922us,而核间串行处理方式总延时达8886us,多核并行处理延时较串行处理提高了67%。同时可以看出,由于脉压、MTI、求模功能颗粒度划分较细,充分利用了4 核资源,检测提取功能受功能限制颗粒度较大因而导致存在空核运行情况,未能完全发挥多核并行处理优势,但对于实际的雷达系统而言,信号处理功能更为丰富,大颗粒度构件占少数,多核并行处理架构具备明显优势。

5 结束语

本文介绍了国产化华睿2 号处理平台,分析了不同处理架构的优劣,设计了一种雷达实时信号处理软件,并搭建系统平台进行验证。结果表明,该软件满足架构与构件跨平台通用、支持软硬件灵活重构、系统延时短。目前该软件已应用于某雷达产品,具备开阔的应用前景。