一种基于TTE端系统的时钟同步算法

2020-02-02王乐

王乐

(北方自动控制技术研究所 山西省太原市 030006)

以太网开放性以及万物互联的特性使其成为近几十年最为流行的网络,以太网一个非常显著的特点就是该网络是事件触发机制。而时间触发机制就意味着网络中难以避免就存在时延的问题。如何升级以太网,使其适应航空电子等高可靠性和安全性的应用场景学术界和工业界都是非期待的问题。基于此,时间触发以太网(Time-Triggered Ethernet)[1-3]应运而生。

在TTE 中,在实时信息、控制信息、图像视频音频等不同类别信息之间进行时钟同步和任务调度是至关重要的环节[4-5]。由于任务调度是在保证全网各个设备间本地时钟与全局时钟同步的基础上进行的,所以时钟同步的确立从根本上影响着整个网络的通信速率[6-10]。因此,开展针对TTE 端系统的时间同步算法研究就具有非常重要的意义。

基于上述情况,结合航空电子系统通信的实际需求,文章提出一种适合于TTE 终端系统之间进行时钟同步的算法。具体地,文章首先对TTE 的同步过程进行了介绍,然后详细阐述了文章所提的TTE 端系统同步算法,进一步利用Verilog-HDL 语言建立一定的算法模型,可以满足各个端系统与客户端实现通信同步功能,从而通过建立好的离线调度表进行数据任务调度。最后文章通过仿真验证了分析的正确性。

1 TTE同步过程

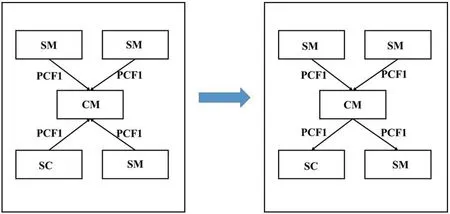

典型的TTE 协议同步主要分为三种角色,首先是同步控制器(Synchronization Master,SM)[11];其次是同步客户端(Synchronization Client,SC)[11],部分文献中也将其称为端系统;最后就是压缩控制器(Compression Master,CM)[11]。典型的TTE 同步过程如图1所示。全局时钟的建立是时钟同步算法的核心,在整个TTE 网络中需要有一个介质能够与网络内各个终端之间的时钟联系在一起,协议控制帧(PCF)就是这么出现的。利用协议控制帧中Payload 字段中所携带的信息可以得知各个终端的本地时钟以及时间差,进而得到新的同一时钟,并建立新的PCF 帧,将新的时钟信息放入其中,并送回各个终端系统中实现各自本地时钟的自我修正。

总体来讲,TTE 时钟同步可以分为两大步骤。第一步为同步控制器发起同步过程,同步控制器向TTE 网络中发送自身的本地时钟信息。第二步为压缩控制器收到同步控制器发送的消息之后,压缩控制器计算同步控制器的时钟信息,之后将计算之后的平均时钟信息向整个网络广播。最后,网络中所有的端系统和交换机收到平均时钟信息之后,以该时钟为基准对本地的时钟进行调节,从而实现网络中所有设备的同步。

图1:TTE 同步过程示意图

图2:TTE 端系统时序保持矫正同步算法

需要指出的是,图1中同步控制器是整个TTE 同步过程的发起者,整个TTE 的同步就是从同步控制器发送PCF 开始的。如果同步控制器有关时间的数值满足之前预定的数值后,PCF 就会被激活发送。如果同步客户端收到PCF,他会将该信息直接中继给压缩控制器。压缩控制器的主要任务就是负责对各个终端发送过来的PCF 进行收集,进一步结合PCF 到达的时间以及PCF 中包含的同步信息计算出同步控制器和同步客户端之间的时间差,由该差值可以得到TTE 网络的全网基准时间。

关于最后的同步过程。压缩控制器在同一时间内向同步控制器发送控制帧,此时如果同步客户端接收来自压缩控制器的特殊帧,他会将该特殊帧透明转发给同步控制器。同时同步客户端会利用该特殊帧完成自身的同步。同步控制器在接收到此特殊帧之后,同样也会更新自身的时间,通过上述步骤便实现了同步控制器、压缩控制器以及同步客户端三者的时钟同步。

图3:冷启动原理图

图4:TTE 端系统时钟同步精度图

2 TTE端系统同步算法

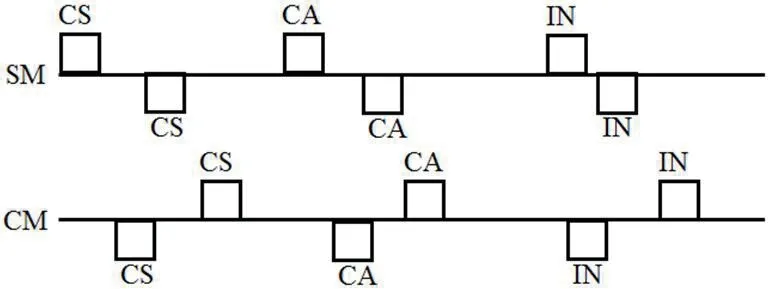

基于上述的分析,文章提出一种TTE 端系统时序保持矫正同步算法,算法的流程结构图如2 所示。该TTE 网络采用SAE AS6802 协议建立全局时钟实现全网时钟同步[12-13]。观察图2不难发现,在TTE 端系统中,三个模块主要的就是同步控制器(SM),同步客户端(SC)以及压缩控制器(CM)。要在网络中完成上述三个模块同步的关键就是特殊控制帧PCF[14-15]。PCF 控制帧将三个之间的时间联系起来,利用文章所提的算法便可以实现整个TTE网络的同步。

该算法的核心思想为:首先同步控制器向网络中传播PCF,压缩控制器接收到PCF 之后利用时序保持算法消除网络中不确定因素引起的时间偏差问题。然后压缩控制器利用集中压缩算法对网络中不能进行同步的节点进行集中处理,之后会通过时钟矫正算法对PCF 帧的信道进行选择,从而得到最优的信道发送PCF 帧。进一步压缩控制器在网络中发送新的PCF 帧,同步控制器和同步客户端在接收到新的PCF 帧之后进行同/异步检测,成功的话将会更新本地的时间,失败的话将会进行时钟的矫正。不满足时钟条件的,将会重复上述的步骤,进行重新同步,直到同/异步检测通过为止。

首先,对文章所提的TTE 时序保持算法进行介绍。TTE 时序保持算法主要是为了解决网络中不同节点的时钟抖动性问题以及PCF 帧透明时域值之间的差异问题。具体地,TTE 网络中不同的终端上的时钟是有不同程度的抖动性的,进一步网络中不同的通信发起者到达接收者之间的网络时间延迟也是不同的。因此,不同接受者在接收到PCF 帧的时间序列和发送PCF 帧的时间序列就会不同。TTE 时序保持算法主要就是为了解决该问题。

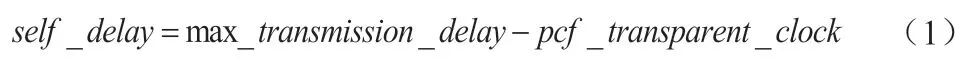

文章定义接收者在获取特殊PCF 帧的时刻为接收时间点用receive_pit 表示,根据该时间点就可以利用时序保持算法对该点进行计算,计算的结果用result_pit 表示。TTE 端系统为了维持时序所要设置的自身时延用self_dely 表示。首先,TTE 端系统网络中的同步控制器(SM),同步客户端(SC)以及压缩控制器(CM)在接收到PCF 特殊帧的时候,获取本地的时钟信息,也就是receive_pit,然后激活文章所提的时序保持算法。然后,获取特殊帧PCF中的透明时钟,也就是pcf_clock,该值表示的是该特殊帧PCF 在整个网络中的真实的总体时延。进一步,我们计算self_dely,计算公式如下:

进一步,计算,计算公式如下

值得注意的是,该算法的精确度是和特殊透明帧的精确度密切相关的。特殊透明帧的精确度对同步时钟的影响是致命的,并且与算法的关系不是很大。故若要进一步提高TTE时序保持算法的精度,需要较高的特殊透明帧精确度支撑。

然后,对文章所提的TTE 时序修正算法进行介绍。TTE 端系统中的同步控制器(SM)和同步客户端(SC)会对接收到的PCF的信道进行选择,进而选择最优的的信道。文章定义某信道接收到的PCF 帧的个数为k 个,因此,便可以计算得到对应的时钟矫正参数,计算公式如下:

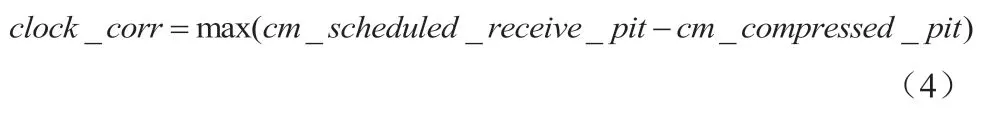

同理,TTE 端系统中的压缩控制器(CM)同样会对接收到的PCF 的信道进行选择,因此,同样可以计算得到其对应的时钟矫正参数,计算公式如下:

3 TTE端系统建模

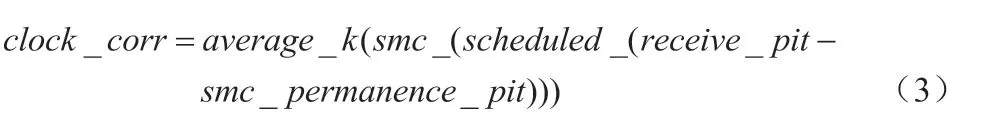

首先对TTE 端系统的启动以及重新启动原理进行介绍。TTE端系统的启动以及重启动都是要遵循严格的协议状态机[16]。具体来说,用到的协议状态机可以分为两种,第一种是工程中使用较多的同步操作态,另一种则是工程中使用较少的异步操作态。一种标准的冷启动原理图如图3所示。观察图3不难发现,同步控制器(SM)以及压缩控制器(CM)之间会交换冷启动帧(Cold Start Frame,CS),确认帧(Cold Start Acknowledge Frame,CA),在此过程中,同步控制器(SM)和压缩控制器(CM)还会完成握手协议。最后,同步控制器(SM)会进入到同步状态,进而启动合成帧的发送。

然后对TTE 端系统的数据处理模型进行介绍。数据处理模块的功能主要是涉及PCF 数据帧的产生、发送、接收、固化等。根据字面意思可以知道,产生主要是构建满足这个协议的PCF 数据帧。再者就是发送和接收,这个功能主要是对PCF 数据帧进行首发处理。固化则是基于PCF 数据帧的时间序列以及相应的算法,计算得到该PCF 数据战的固化时间点。

最后对TTE 端系统的时钟修正模型进行介绍。时钟修正模型的功能主要是完成对PCF 数据帧的筛选、修正以及执行。首先是对数据帧的筛选,该功能主要是对最优信道的选择。再者是修正,修正主要是对当前周期的时钟修正值进行计算。执行则是将上一步计算得到的修正值应用到修正环节。

表1:TTE 端系统同步仿真结果

4 仿真验证与结果分析

为验证文章理论分析的正确性与有效性,文章进行了仿真。文章利用Verilog-HDL 进行仿真,Verilog-HDL 集成了各种函数,通过该软件可以大大提高学者的仿真效率。如果没有特殊说明,文章的仿真参数如下:对于图3中的同步控制器(SM),同步客户端(SC)以及压缩控制器(CM),其数量分别设置为3 个,1 个,1 个。网络带宽十分丰富,达到了百兆的级别。数据在传输过程中的延时按照微秒级别。

文章首先仿真集成周期的长度对同步时间精度,建立、维持同步的时间以及设备时钟偏差进行了分析,仿真结果如表1所示。

在表1中,所有的长度,精度以及时间长度的单位均为微秒。观察表1不难发现,当集成周期的长度小于等于2000 的时候,其时钟同步精度是没有变化的,而建立同步的时间随着集成周期的变大而不断变大,三者的维持同步时间是相同的,但是设备的时钟偏差是随着集成周期长度的增长而增长的。进一步,当集成周期长度为10000 以及100000 的时候,TTE 端系统没有进入到稳定的同步状态,这两种情况可以归为极端性问题。

文章进一步仿真时钟同步精度以及其收敛的速度问题,仿真结果如图4所示。

观察图4不难发现,TTE 端系统的本地时钟是向着标准时钟进行收敛的。

5 结论

文章提出一种基于TTE 端系统的时间同步算法。首先对TTE同步过程进行了介绍,然后详细阐述了文章所提的TTE 端系统的同步算法,再者对TTE 端系统进行了建模,最后理论分析和仿真都验证了文章分析的正确性。