基于虚拟机内省的Intel PT多进程监控技术研究

2020-01-07朱俊虎

◆李 贺 张 超 杨 鑫 朱俊虎

基于虚拟机内省的Intel PT多进程监控技术研究

◆李 贺1,2张 超2杨 鑫1,2朱俊虎1

(1.战略支援部队信息工程大学 河南 450002;2.清华大学网络科学与网络空间研究院 北京 100083)

以Intel Processor Trace(PT)为代表的片上动态跟踪技术有着低开销、低感知的优良特性,在程序行为记录和监控领域得到了越来越广泛的应用。然而,由于片上动态跟踪技术依赖CPU特性实现,对于操作系统内核监控、恶意代码分析等需要在虚拟化平台上运行程序的场景支持还存在一些困难。本文通过对Intel PT片上动态跟踪技术的研究,提出了一套基于虚拟机内省的Intel-PT多进程监控技术,通过将Intel-PT嵌入到硬件虚拟化平台上,实现了对硬件辅助虚拟化客户机中的多个进程并行进行监控。实验结果表明,该技术可以有效监控硬件虚拟机中并行多个进程。

虚拟化;多进程监控;非侵入调试

片上动态跟踪技术因其低开销、被监控程序无感的优良特性,在控制流完整性保护、恶意代码分析检测、执行路径记录等领域得到了越来越广泛的应用。片上动态跟踪技术主要原理是使用CPU内部专用的硬件非侵入式地实时记录程序执行的信息[1]。片上动态跟踪技术早期是为了解决嵌入式设备调试困难问题而发明的,随着Intel在其第五代CPU上添加了Intel Processor Trace (Intel PT)特性,使得在X86平台下也可以使用在Intel CPU中内嵌的片上动态跟踪技术对程序进行非侵入调试。目前,Intel PT已经被应用于程序行为记录[2][3]、模糊测试代码覆盖率生成[4][5]、软件安全防护[6]、控制流图完整性保护[7]等领域。

然而,由于Intel PT技术主要依赖CPU硬件才能发挥作用,对于虚拟化平台支持的存在一定的困难。对于需要运行在虚拟化平台上的操作系统内核执行路径记录、恶意代码分析等场景不能提供较好支持。

本文通过对Intel Virtualization Technology(VT)硬件辅助虚拟化技术以及操作系统实现原理的分析,在Linux 4.19.34 KVM模块上实现了一套针对硬件辅助虚拟机中运行的多个目标进程使用Intel PT进行监控的方法。

1 Intel PT与Intel VT联合使用原理

在Intel处理器手册[8]第三卷36章5节对Intel PT监控硬件虚拟机进行了说明。Intel PT技术可以和Intel VT硬件虚拟化技术相结合,对运行在虚拟机中的程序进行记录。在进入VMX硬件虚拟化模式时,虚拟机是运行在真实的物理CPU上,所以可以直接根据用于配置Intel PT的MSR(Model Specific Registers)寄存器的相应字段监控虚拟机中目标进程活动。

通过配置MSR寄存器Intel PT使能位(TraceEn位),在虚拟机执行非特权指令陷入时,启动Intel PT监控。当虚拟机中执行到特权指令,导致虚拟机陷出行时关闭Intel PT监控。在Intel PT监控硬件虚拟化状态转换时,还可以生成VMCS包来标识虚拟机动作,同时可以通过MSR对虚拟机陷入和虚拟机陷出动作是否产生对应PT数据包进行配置。

需要说明的是,虚拟机陷出后的处理程序确实会对于PT控制流记录产生一定影响,本文在不对这些影响进行特殊处理,解码器会在解码时不对由于内存空间转换产生的数据包进行处理,故而忽略虚拟机陷出带来的大部分影响。

2 基于虚拟机内省的Intel-PT技术设计和实现

在X86平台上,操作系统切换进程上下文的过程中,需要对虚拟内存空间进行切换。以Linux为例,在用户进程发生切换时,需要切换CPU运行的地址空间,作为保存全局页表目录(Page Global Directory,PGD)的页表基地址寄存器(CR3寄存器)内容也需要切换。另外,为了实现进程空间的隔离,每个进程的全局页表目录内容都是不同的,这样就可以通过全局页表目录来区分进程。

虚拟机内省(virtual machine introspection,VMI)指的是在虚拟机运行过程中获取其内部运行程序的状态。在Intel VT硬件虚拟化中,可以将设置为在写页表基址寄存器时执行虚拟机陷出动作,退出虚拟化状态(VMX Non-root模式)。在虚拟机启动时将虚拟机行为控制域中对应写页表基址寄存器的位设置为监控模式,就可以对虚拟机切换进程动作进行监控。这样就具备了使用虚拟机内省技术监控虚拟机进程切换状态的能力。

图1 多进程监控示意图

通过监控页表基址寄存器的切换,内核虚拟化模块就具备了在虚拟机外部监控特定进程运行状态的能力。如图1所示,首先需要将目标进程页表基址寄存器的值告知外部监控程序。而后任何虚拟机陷出行为都会让PT监控停止,这时就可以修改PT监控的各项配置。在目标进程通过上下文切换从就绪状态进入执行状态时,可以通过硬件虚拟化捕获CR3寄存器的值,通过比较,如果是目标进程就可以启动PT对该进程进行监控,如不是就将虚拟机的页表目录寄存器改为指令要修改目标值,而后跳过这一条指令返回虚拟化模式继续执行。对于多个目标进程,可以在内核中构造一个表来记录这写进程的页表目录寄存器值,在进程进入执行状态前查询是否在这个表中。为了提高查询效率,可以利用内核中比较常见的哈希链表来存放全局页表目录。

由于使用Intel PT需要对MSR寄存器进行直接操作,所以在内核模块中实现Intel PT的配置管理模块。在文献[4]实现的基础上,本文利用Linux 4.19.34 KVM硬件虚拟化内核模块进行修改,配合QEMU 2.9.0用户态虚拟机管理器以及在QEMU附加定制的PT解码器模块,实现了上述多进程监控方案。在KVM虚拟机初始化过程中,用setup_vmcs_config函数对虚拟机行为控制数据结构部分内容进行初始化。在扩展页表功能开启的情况下,负责标识监控页表基址寄存器写操作的CPU_BASED_CR3 _LOAD_EXITING位会被置为关闭。因此通过简单地将代码中置位的操作去掉,就可以在扩展页表功能开启的情况下启用CR3寄存器写操作监控,所有写入CR3寄存器的指令都会引发虚拟机陷出动作,提高被测程序执行效率。

3 实验

为了能够有效验证多进程监控技术,本文选择Windows系统中VirtualAlloc函数对应内核函数作为测试目标。本文基于文献[4]专门在Linux 4.19.34上实现了一个单进程监控的Intel PT动态监控平台进行工作对比,并实现了一个简单的测试程序。测试程序的主要作用是,开启PT监控,并将最后生成的覆盖率数据保存下来。通过比较程序并发时生成的控制流数据,查看有无多进程PT监控能否在并发的情况下记录内核活动。在虚拟机中通过脚本并发执行10个测试程序,记录其对应的内核代码执行路径。生成的跟踪记录数据主要是跳转指令地址(基本块尾部,省略前32位地址),采用IDA生成控制流图,并将PT记录的地址标为黄色,为了方便理解,本文将路径中经过但没有记录基本块也进行染色。便于比较两者之间的区别。首先针对本文实现的多进程监控进行测试,其次针对专门实现的单进程PT监控平台进行对比。

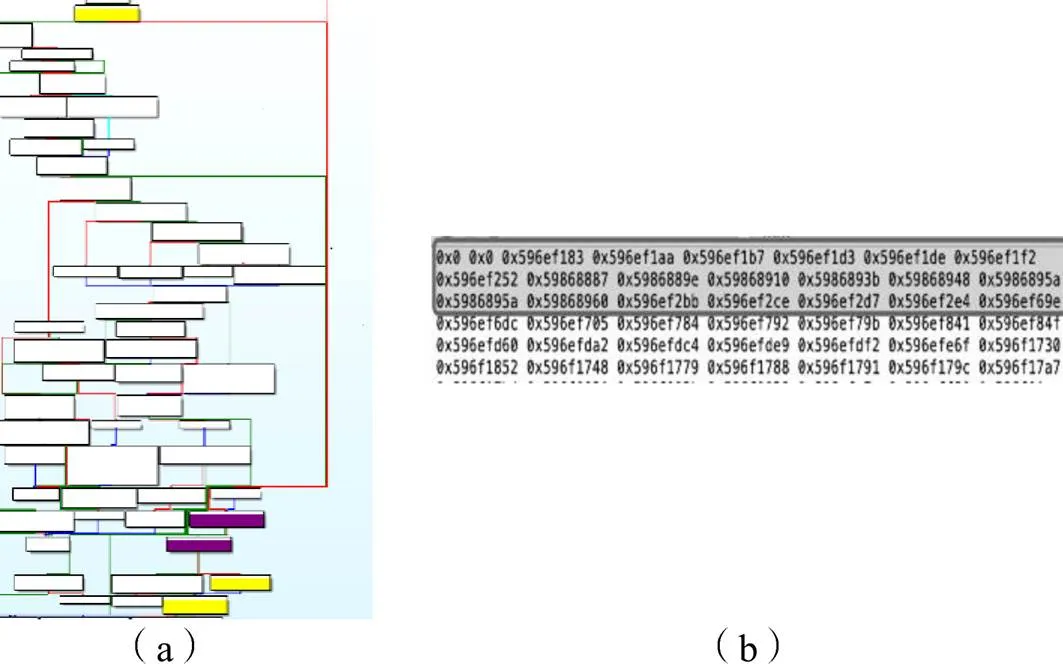

图2 PT多进程监控记录并发进程的结果

本次测试选取Windows 10(1809英文版)ntoskrnl.exe中sub_FFFFF80469EED480函数做展示,ntoskrnl.exe内存地址为0xfffff80469e97000到0xfffff8046a888000。如图2所示,可以看出图2(b)所示的控制流图完整地记录了内核代码正确的执行路径,将sub_FFFFF80469EED480函数中内核执行路径上的所有条件跳转都进行了正确的记录。

如图3所示,单进程PT监控测试结果记录的前几个地址都在sub_FFFFF800596EECF0函数中,此时ntoskrnl.exe映射在从0xfffff800596a5000到0xfffff8005a096000的内存,从图3(b)可以看出,红框中记录的地址不仅前两个是无效的零地址,第三个地址0x596ef183到第四个地址0x596ef1aa中间路径上存在基本块缺失,如图3(a)图所示,最短路径上缺少两个条件跳转分支的记录(紫色基本块)。另外,如图4所示在第五个地址0x596ef1d3出现了偏移错误,地址指向了指令的内部字节。

图3 PT单进程监控记录并发进程的结果

图4 错误的跳转指令地址

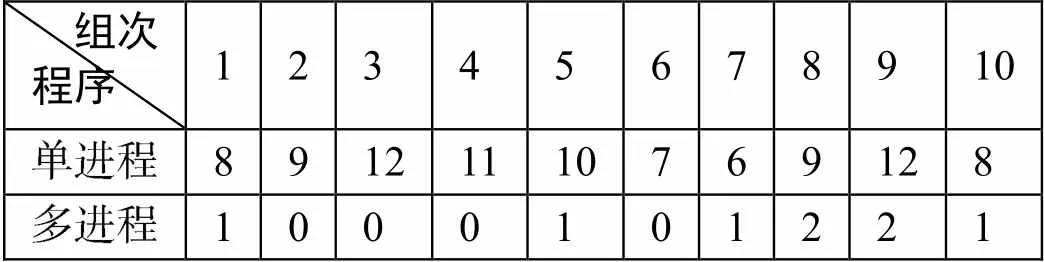

为了进一步证明多进程记录有效性,分别对12个进程进行监控,通过10组的实验进行对比,出现没有任何PT基本块地址记录的次数如表1所示:

表1 记录地址数量为零的PT记录

从表1中可以看出,PT多进程监控虽然也存在获取地址不稳定的问题,但相对于单进程监控而言,已经又了质的提升,具备实用价值。PT多进程监控针对Linux内核也可以获得比较好的效果。

4 结束语

本文研究了Intel PT在监控虚拟化平台程序中存在的不足,设计和实现了基于虚拟机内省的Intel PT多进程监控技术,通过捕获虚拟机进程切换过程,并利用Intel PT监控硬件虚拟机的特性,有效实现了对于虚拟机中多个进程进行并行监控。

[1]扈啸,陈书明,李杰,等.片上 trace:嵌入式处理器的有效调试和优化技术[J].国防科技大学学报,2008(2):46-50.

[2]Linux. Perf [EB/OL]. https://perf.wiki.kernel.org/index.php/Main_Page.

[3]Cui W,Ge X, Kasikci B,et al. {REPT}:ReverseDebugging of Failures in Deployed Software[C]//13th {USENIX} Symposium on Operating Systems Design and Implementation({OSDI} 18).2018:17-32.

[4]Schumilo S,Aschermann C,Gawlik R,et al. kAFL: Hardware-Assisted Feedback Fuzzing for {OS} Kernels[C]//26th {USENIX} Security Symposium ({USENIX} Security 17).2017:167-182.

[5]Zhang G,Zhou X,Luo Y,et al. Ptfuzz:Guided fuzzing with processor trace feedback[J].IEEE Access,2018(6):37302-37313.

[6]王心然,刘宇涛,陈海波.基于 IPT 硬件的内核模块 ROP 透明保护机制[J].软件学报,2018,29(5):1333-1347.

[7]Ge X,Cui W,Jaeger T. GRIFFIN: Guarding Control Flows Using Intel Processor Trace[J]. Acm Sigarch Computer Architecture News,2017,45(4):585-598.

[8]Intel. Developer Manuals [EB/OL]. https://software.intel.com/en-us/articles/intel-sdm.

国家自然科学基金联合基金项目(U1736209)资助。