星载同步NANDFlash的研究与应用

2019-12-24张俊杰沈霞宏徐瑞瑞王冠雄

张俊杰,沈霞宏,徐瑞瑞,王 盛,王冠雄

(上海航天电子技术研究所,上海 201109)

0 引言

随着载荷技术的飞速发展,新研卫星对存储系统的读写速率、存储容量等指标也提出了更高的要求,而传统的异步星载存储方案具有速率低、集成度低等特点,若继续延用此方案则会造成单机体积功耗重量的倍增,无法适应星上有限的资源限制,因此迫切需要开展新型星载存储技术研究[1]。

文献[2]中宋琪等人采用了3Dplus公司封装的异步NANDFlash芯片,并结合流水线管理技术设计了一款宇航固态存储器,其单芯片吞吐速率仅能达到500 Mbps。镁光MT29F系列SLC型NANDFlash芯片提供了一种新的同步Flash控制方式,其数据传输采用DDR方式(时钟上下沿同时采样),支持更高的时钟频率,其接口吞吐率为传统异步Flash控制方式的4倍,并且符合ONFI2.2标准。此外,该同步存储芯片还提升了集成度,每个芯片包含8个LUN单元,每个LUN包含4 096个块,每块包含128页,每页能够存储8 640 Byte数据,单芯片总容量可达256 GB。

文献[3]中李袁鑫等人设计了一款支持ONFI2.1同步模式的NANDFlash控制器,但是其应用平台为SOC芯片并且只做了功能仿真,缺少对基于XILINX FPGA平台的NANDFlash控制器设计和相关外围电路的硬件设计指南。

因此,本文针对该同步NANDFlash芯片的外围电路设计进行信号完整性分析与优化,设计了一款支持同步操作的NANDFlash控制器,用Modelsim对所设计的控制器进行了仿真并进行了板级验证。

1 控制器结构

设计的同步NANDFlash控制器是存储控制单元的一部分,能够接收来自FPGA内部上级管理单元的各种命令、操作地址和写数据并返回读数据和操作状态,实现了对底层Flash器件的直接控制。控制器具体包括2个FIFO缓存模块、主控模块、数据转换模块、ECC模块和时钟管理模块等,其结构框图如图1所示。

图1 控制器结构

图1中FIFO缓存模块主要负责缓存读写数据并把数据同步到本地时钟域;主控模块主要负责所有状态机的跳转与各模块控制信号的切换;数据转换模块主要用于单边沿数据和双边沿数据的切换;ECC模块主要用于数据的信道编码和译码纠错;时钟管理模块负责产生各模块所需的时钟资源。

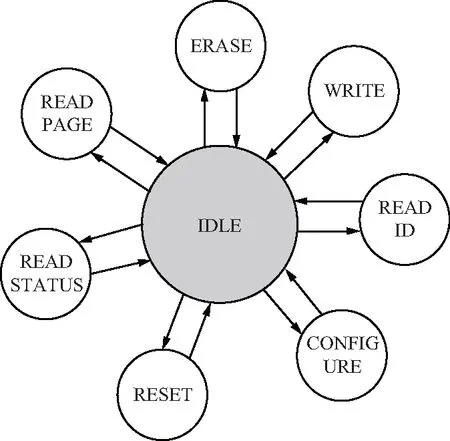

主控模块是整个控制器的核心控制模块,由1个主状态机和多个子状态机构成。主状态机有1个空闲状态和7个工作状态,分别对应擦除操作、读数据操作、写数据操作、读ID操作、读状态操作、重置操作和配置操作,其状态转换如图2所示。每个工作状态又对应1个子状态机,负责每个操作的具体细节[4]。

图2 主控状态机

2 信号完整性分析

由于该NANDFlash芯片数据传输频率高达200 MHz,在设计器件外围电路时,为了在高速环境下获得更好的信号质量,本设计基于Hyperlynx对厂家提供的芯片IBIS模型进行了仿真以选择合适的终端匹配电阻[5]。

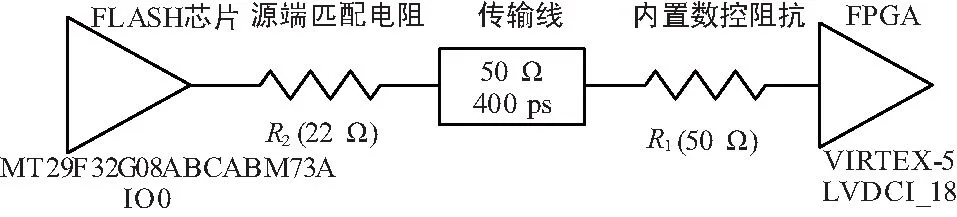

该款NANDFlash芯片传输电平标准为LVCOMS1V8。根据XLINX V5用户指南,这种电平标准采用源端串联阻抗匹配方式较为合理,且对于FPGA端可以使用V5 FPGA内置的数控阻抗(LVDCI)以减小印制板布局布线的困难[6]。NANDFlash双向IO管脚在无匹配电阻和匹配电阻为22 Ω的情况下做了时域仿真,如图3所示。

图3 Free-form仿真原理

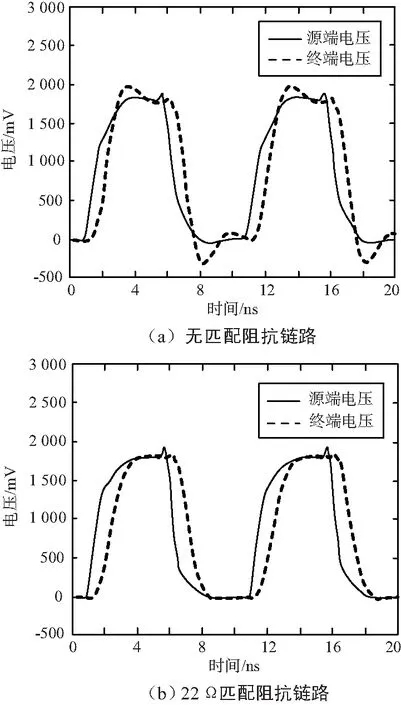

由测量工具测得,在接入22 Ω阻抗匹配电阻后上升沿仅变缓了250 ps,对于Flash的操作时序的影响几乎可以忽略,如图4所示。

图4 阻抗匹配仿真对比

无阻抗匹配时的Flash芯片端口的电压过冲量达到300 mV以上,超过了芯片手册中的推荐DC标准,无法保证器件工作的可靠性。而在接入22 Ω阻抗匹配电阻后原来存在的振铃现象得到了明显的改善。若采用33 Ω匹配电阻,则对于振铃现象并无更多改善,并且会使上升沿变得更缓,显然是没有必要的[7]。

3 控制器设计要点

要实现对NANDFlash的同步控制,需考虑诸多设计因素,限于篇幅有限,本文将针对在设计过程中遇到的主要问题展开讨论。

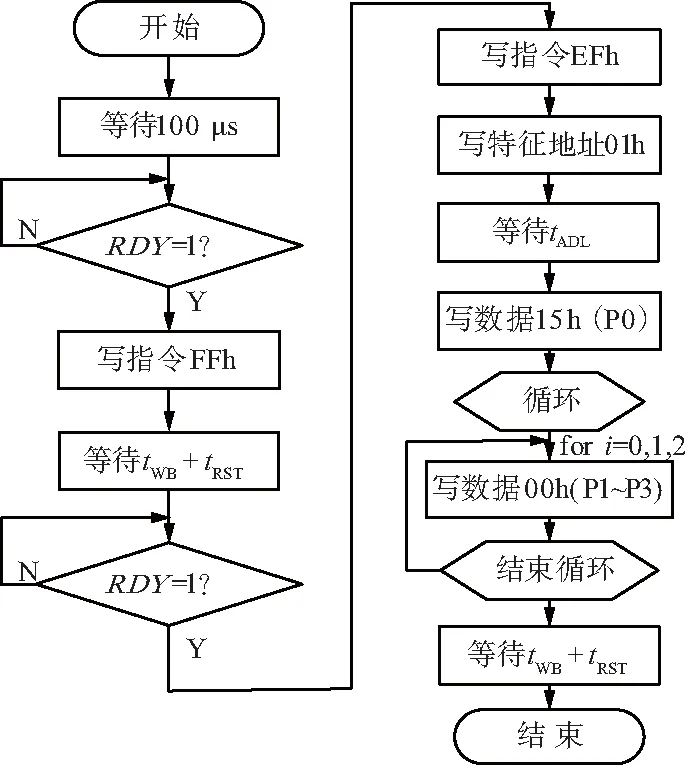

3.1 上电复位及模式配置

NANDFlash在上电后需等待100 μs直至R/B信号拉高,之后Flash芯片会自动进入异步Standby模式。在接收其他指令前,首先需要对芯片进行复位(RESET指令)[8]。复位结束后需要通过配置指令对芯片进行配置使之切换到同步模式5(工作时钟100 MHz)空闲状态,此后可以通过其他指令控制芯片的工作模式。需要注意在配置成功之前指令与地址的输入时序均为异步模式,而配置成功之后所有操作均为同步模式。本文所设计的该模块状态机流程图如图5所示。

图5 上电复位及模式配置流程

其中,异步模式下的WE信号即为同步模式下的CLK信号(信号复用),CLK信号为同步模式下的100 MHz工作时钟,因此在此时钟切换时需要格外注意,应尽量避免产生毛刺或组合逻辑电路[9]。若使用assign语句对该时钟信号切换,在实际测试中仍发现有毛刺的存在。为了实现时钟的无缝切换,设计中本文调用了XILINX MUX原句并使芯片在时钟切换时处于非工作状态。

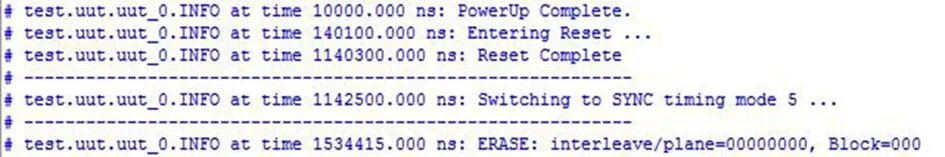

本设计所有指令、地址、数据读写时序均严格遵守芯片手册中的时序要求。为了更好地检验设计的正确性,本设计采用Micron科技提供的Verilog仿真模型对各模块进行了功能仿真[10]。仿真的部分截图如图6所示,从图6中可以看出本文所设计的上电复位及配置等模块通过了仿真模型的检验。

图6 上电复位及配置仿真结果

3.2 写操作设计

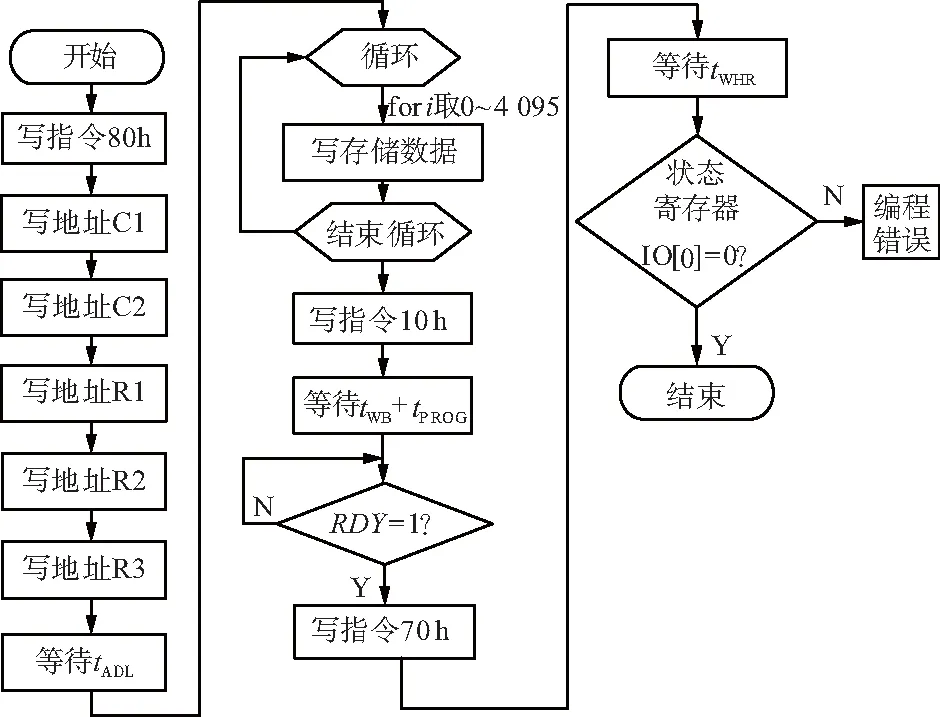

本文根据MT29F256G08AUCAB芯片手册所设计的写操作流程图如图7所示。

图7 写操作流程

主要可分为以下几个阶段:

① 写入80h指令和5个周期的地址,指定编程的块地址和页地址,每周期输入的指令或地址需间隔tCAD并满足同步时序。

② 将需要编程的数据通过8位数据总线以同步方式传送至NANDFlash内部寄存器中。

③ 写入10h指令,即启动编程,等待tPROG编程时间直至编程结束,可通过查询RDY信号判断编程是否结束。

④ 编程结束后可通过查询指令70h读取状态,检测此次操作是否成功;若操作成功,则进行下次操作,否则重新进行编程。

在进入DDR数据输入模式之前,必须满足以下条件:① CLK时钟稳定运行;② CE信号拉低;③ W/R信号拉高;④ 满足tCAD时间间隔;⑤ ALE和CLE在CLK上升沿拉高。

在进入DDR数据输入模式tDQSS时间之后,用户控制器需要在DQS的上升沿和下降沿将待写入的数据输出到DQ[7∶0]寄存器端口,同时为了使芯片采数更加稳定并满足芯片的时序要求,本设计通过采样时钟与DQS信号间的相位差来控制DQS的沿口对准写入数据的中心。此外,写入的数据为双边沿DDR形式,而在FPGA内部处理的数据形式一般为单边沿SDR形式,因此需要调用XILINX ODDR基元将SDR数据转换为DDR数据。

在写完一个页之后,如果需要退出DDR数据输入模式,则需要满足以下条件:① CLK时钟稳定运行并且DQS到CLK偏移量满足tDSH和tDSS;② CE信号拉低;③ W/R信号拉高;④ ALE和CLE在CLK上升沿拉低。具体的时序要求可参考芯片手册。

3.3 读操作设计

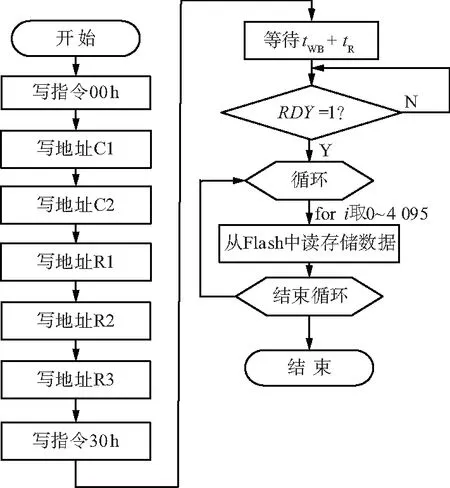

本文根据MT29F256G08AUCAB芯片手册所设计的读操作流程图如图8所示。

图8 读操作流程

主要可分为以下几个阶段:

① 写入00h指令、5个周期的地址和30h指令,指定回读的块地址和页地址并启动读操作,每周期输入的指令或地址需间隔tCAD并满足同步时序。

② 等待tR读操作等待时间,对从NANDFlash内部寄存器中读出的数据进行采样并把双边沿数据(DDR)转换为单边沿数据(SDR)写入到FPGA FIFO中。

在芯片响应读操作之后数据即可从NANDFlash阵列中输出。在进入DDR数据输入模式之前,必须满足以下条件:① CLK时钟稳定运行;② CE信号拉低;③ 用户控制器必须释放DQ[7∶0]和DQS给芯片控制;④ 为了使选定的LUN在tWRCK时间内取得DQ总线和DQS的控制权,W/R在CLK上升沿必须拉低;⑤ 满足tCAD时间间隔;⑥ ALE和CLE在CLK上升沿拉高。

在进入DDR数据输出模式之后,DQS信号会在距CLK上升沿tDQSCK时间之后开始翻转,其具体时间以芯片实测为准。此后,NANDFlash会在DQS的双边沿从DQ[7∶0]端口输出读出的数据。

在读完一个页之后,如果需要退出DDR数据输出模式,则需要满足以下条件:① CLK时钟稳定运行;② CE信号拉低;③ W/R信号拉低;④ ALE和CLE在CLK上升沿拉低。

由于读出的数据是与DQS信号的边沿对齐的,所以需要对接收到的DQS信号进行90°相移使之与DQ信号的中心对齐,以采到准确的数据。一般来说移相有2种方法:DCM时钟管理单元;IODELAY延迟单元[11]。而NANDFlash中DQS信号并非真正的时钟信号,有时该信号是拉低的,因此无法使用DCM进行移相。本设计调用了XILINK IODELAY原句来进行移相[12]。

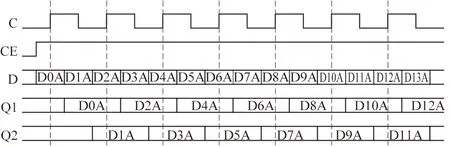

此外,读出的数据为DDR形式,而在FPGA内部处理的数据形式一般为单边沿SDR形式,因此需要将DDR数据转换为SDR数据。若使用移相后DQS信号的上升沿和下降沿同时采样,则相当于电平触发,在高速时易受到干扰。因此,本文采用了XILINX FPGA自带的IDDR基元来实现对DDR数据的采样,在OPP OSITE_EDGE模式下其时序图如图9所示。

图9 数据转换时序图

最后可以通过一组上升沿触发的寄存器将这2组8 bit数据合并成16 bit数据,再通过一级FIFO缓存将数据同步到本地时钟域就可以对读出的数据进行下一级处理了。

4 实验结果与分析

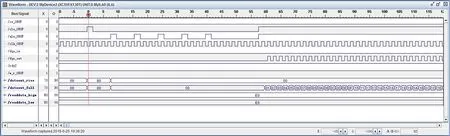

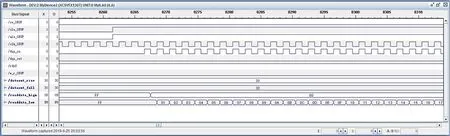

本文实现了NANDFlash在同步模式下的应用,在用Modelsim对本文所设计的控制器进行仿真验证之后,可以用EDA工具综合并布局布线后下载到所设计的存储板中进行测试[13]。为了测试方便,本文采用了累加数作为码源进行测试。在同步模式下写一页操作的Chipscope采样波形如图10所示,在同步模式下读一页操作的Chipscope采样波形如图11所示。

图10 同步Flash写操作采样图

图11 同步Flash读操作采样图

可以看到在擦除操作过后,控制器往NANDFlash中以同步方式写入一串累加数并成功读出,没有误码。连续的读写测试结果表明,在同步模式下,本文设计的控制器的功能和时序都工作正常。

5 结束语

本文以航天任务为背景,在对同步NANDFlash芯片存储机理和时序逻辑进行仔细研究的基础上,分析并优化了其外围硬件电路的设计,并根据操作流程和数据流设计了一款支持ONFI2.2的同步NANDFlash控制器[14]。最后分别在仿真环境和真实环境下,对所设计的控制器进行了时序测试,全面验证了控制器的设计功能[15]。实验结果表明,控制器工作正常,能够以同步方式进行读写等操作,将传统异步方式的单芯片读写速率由399/375 Mbps提升至1 598/1 340 Mbps,实现了预期的设计目标,为下一代星载高速固态存储系统的研制提供了技术支持。