基于UVM的CPRI接口的验证*

2019-12-04王燕

王 燕

(上海诺基亚贝尔股份有限公司,江苏 南京 210037)

0 引 言

随着集成电路规模的日益增长,芯片设计的难度逐步提升,对芯片验证也提出了更高的要求。统计表明,芯片验证占据了整个开发周期的70%以上,如何能快速高效地在前期就尽可能地挖掘出所有故障,是迫在眉睫的需求。UVM验证方法学[1]应运而生,综合了其他方法学的优点,成为业界的主流。

通用公共无线接口(Common Public Radio Interface)[3]是一种标准化协议,定义了无线基础设施基站的射频设备控制(REC)和射频设备(RE)之间的数字接口。这实现了不同供应商设备的互操作性,保护了无线服务提供商的软件投入。CPRI协议涉及同步流程、用户面数据、控制管理面的传输机制,用传统的verilog语言搭建测试平台、编写BFM模型会非常地艰巨。

本文将采用UVM验证方法学对CPRI接口进行验证,利用其sequence级联的方式构建超帧激励,高效全面地覆盖所有功能点。

1 UVM验证平台

UVM(Universal Verification Methodology)即通用验证方法学,是一个以SystemVerilog[2]类库为主体的验证平台开发框架,验证工程师利用其可重用组件可以构建具有标准化层次结构和接口的功能验证环境。UVM有效结合了测试激励随机生成、自测试平台和随机化约束等方法,采用最佳框架以实现覆盖率驱动的验证,使验证工程师通过采用高级验证技术来降低风险,满足缩短产品上市时间的迫切需求。

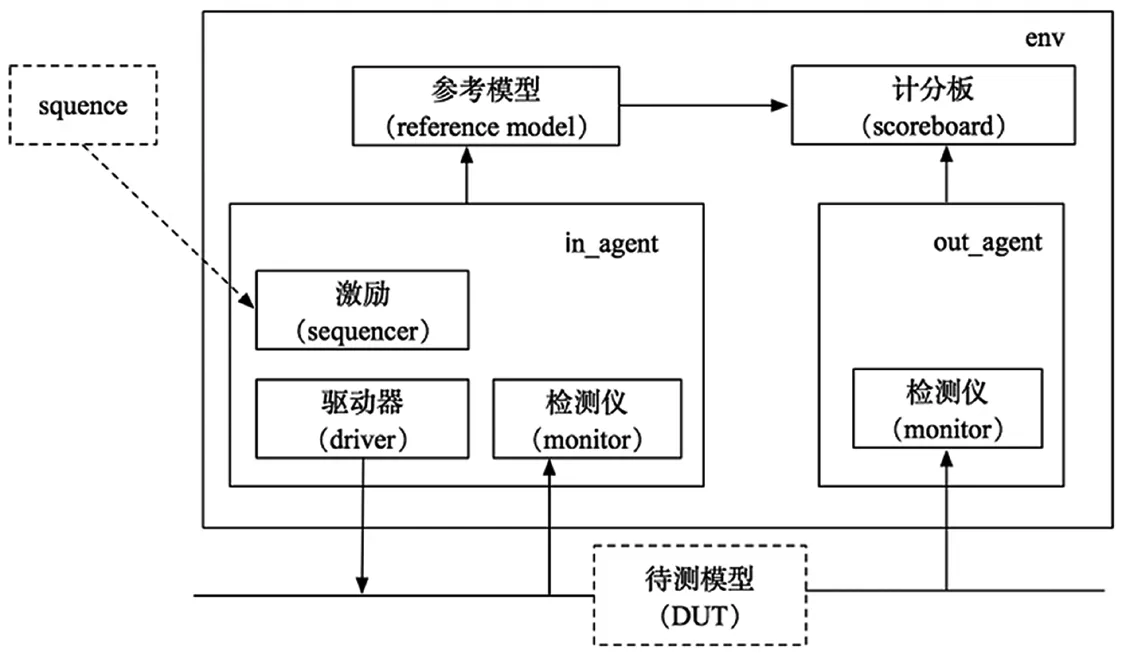

典型的UVM验证平台如图1所示,这是一种层次化的验证架构。

图1 典型的UVM验证平台框图

验证平台主要包含了下列组件:

driver:driver是验证平台最基本的组件,是数据流的源泉,它负责将transaction驱动至DUT的接口。

monitor:monitor负责采集DUT接口的输出,将其转化成transaction之后送入scoreboard进行比对。

sequencer:sequencer 只有在 sequence 出现的情况下才能体现它的价值,这两者是相辅相成的,共同负责产生 driver 所需的 transaction 激励。

agent:agent 负责对 driver 、 monitor和 sequencer进行封装。driver和sequencer之间需要通过connect函数进行连接,从而实现数据的传递。driver和 monitor 负责的工作是相对的,但都是在做transaction 级和 DUT 端口级的数据之间的转换,其本质可以被定义为一种协议,因而使用 agent 对这两者进行封装,再在 env 中直接实例化 agent,每一个 agent 都分别代表不同的协议。

reference model:reference model采用 system verilog简洁高效的task/function进行编写,是设计的预计输出,其结果传输至 scoreboard,用于 DUT 实际结果的比对。

scoreboard:scoreboard 是验证平台的计分板,验证平台将通过这个组件比对来源于reference model 的输出标准和源于 monitor 收集到的实际输出,比较结果是否一致。

env:由于验证平台的组件扩展越来越丰富,为了在保证代码结构层次清晰的前提下,又能方便地对这些组件的实例化,验证平台中引入了一个env 容器类,当使用 run_test 函数时,传递的参数就是这个容器类,使得 UVM 能够自动地创建组件实例,大大地减少了代码的冗余。

sequence机制、factory机制和phase机制是UVM的三大法宝。引入sequence机制的好处是将激励从driver中剥离出来,有利于测试平台的重用。通过编写不同的sequence,实现不同的测试用例。factory机制实现了方便的重载,在不改变测试层次和结构的前提下,灵活地进行组件的扩展。phase是使各验证组件能够按需自动化执行的一种机制,增加了验证平台在各个阶段的可控性和复用性。按仿真前后可以分为仿真前的build_phase(细分为4个phase),仿真中的 run_phase (细分为12个phase)以及仿真后的 cleanup_phase(细分为4个phase)。

2 CPRI接口模块

CPRI接口模块包含接收通路模块和发送通路模块两大部分,支持CPRI协议中的rate6和rate8。CPRI接口模块架构如图2所示。

在接收方向,根据40bit并口上的数据和控制位,进行超帧同步头的提取,解析控制字段的信息,结合protocol版本、p_pointer值的匹配进行同步。待完成同步流程之后,对fast_cm控制字进行5b/4b解码,从而还原出其承载的以太报文并通过GMII接口发出,同时解析I/Q数据,根据unpack配置,通过axc接口送出。

在发送方向,GMII接口接收以太报文,进行4b/5b编码,axc接口接收I/Q数据,根据pack配置,iq交织之后存放进32bit位宽的数据RAM,cpri_tx_core将各类控制信息、I/Q数据组帧之后在40bit的并行数据口发出。

图2 CPRI接口模块架构图

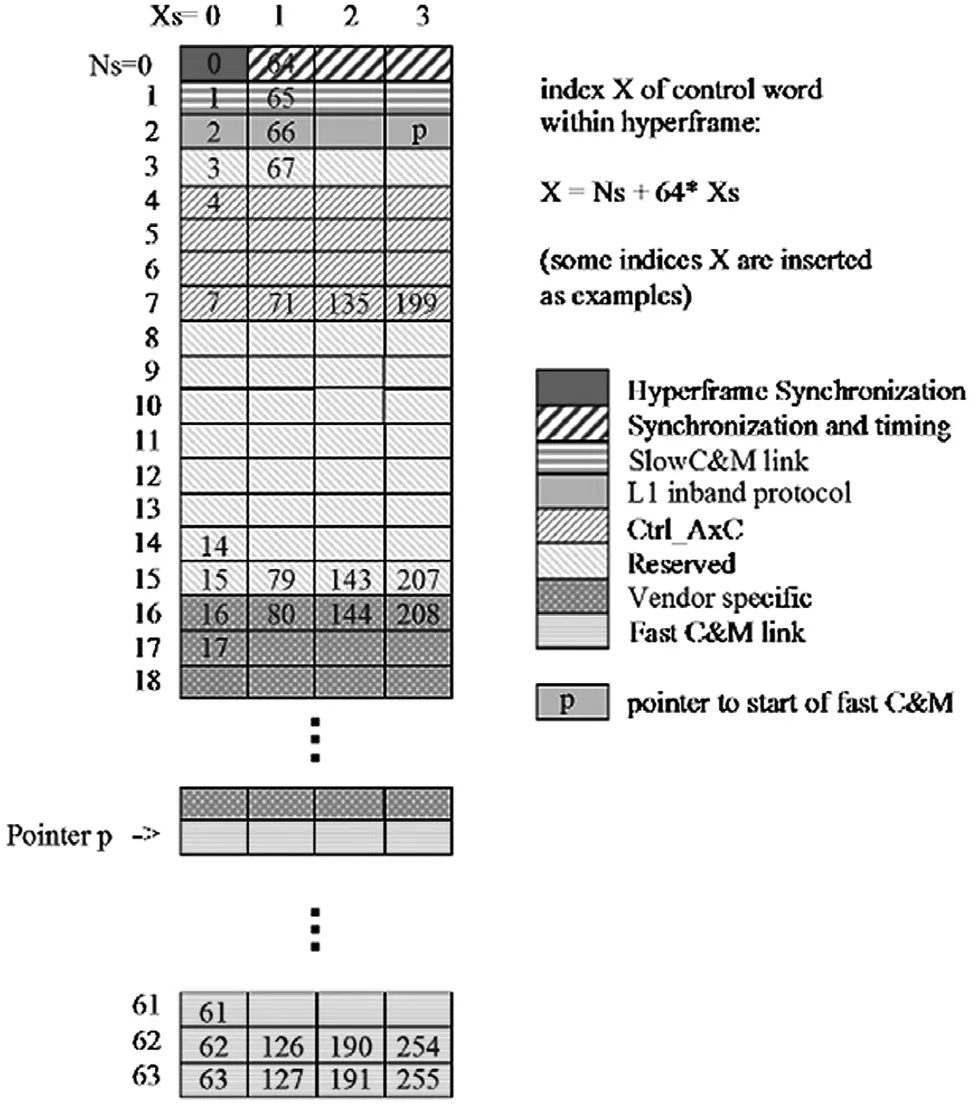

CPRI协议定义了10ms内包含150个超帧,每个超帧由256个基本帧组成,每个基本帧分为16个W(W的字节数根据不同的CPRI速率而定),第1个W为控制字,其余15个W用于传输I/Q。因此每个超帧包含256个控制字,用途如3所示,这是整个接口实现的难点。

图3 CPRI控制字图解

对于一个超帧,控制字0固定用作同步头,可以根据它来定位超帧的起始;控制字64/128/192用作超帧计数和BFN(10ms帧)计数。Ns=1对应的控制字用于承载Slow C&M即HDLC协议;Ns=2对应的控制字用于层1的带内协议;Ns=4~7对应的是AxC的控制字;p指针定义了fast C&M的起始Ns,p指针开始一直到Ns=63都是fast C&M的传输范围,因此p指针可以根据传输能力的需求而定;Ns=16直到p指针-1,用户可以自定义用途。另外还有一些保留字段用于日后的扩展。

3 搭建基于UVM 的CPRI接口模块验证平台

3.1 CPRI接口模块验证平台

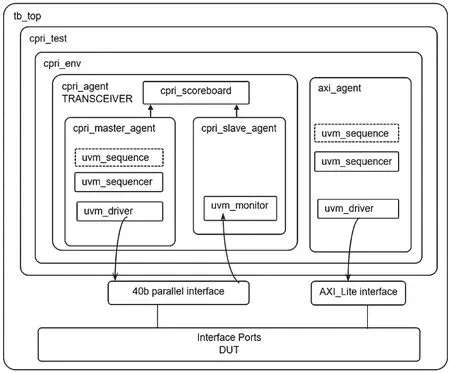

CPRI 接口模块验证平台如图4所示。

tb_top是整个测试的顶层,例化了DUT,将其端口与指定的interface进行连接,并通过uvm_config_db语句将interface下发到cpri_test下逐层的对应接口,从而实现了DUT与各BFM之间的连接。测试采用以40b并口为主,其他接口为辅的策略,因此GMII接口和AxC接口采用环回方式,40b并口侧进行数据的激励和环回之后的比对。

cpri_test是测试用例集,base_test中实例化cpri_env,并对cpri_config进行约束化的随机。各测试用例基于base_test进行扩展,可对cpri_config改写约束,可对底层的sequence进行override,从而实现不同功能点的覆盖。

图4 CPRI接口模块验证平台

cpri_env主 要 包 含 两 个agent:cpri_agent和axi_agent,分别对应两个接口。cpri_agent工作在TRANSCEIVER模式,下层的cpri_master_agent产生cpri超帧,通过自定义的40b并口总线机制对CPRI接口模块进行激励,同时发送一份给计分板。cpri_slave_agent在模块发送方向的40b并口总线进行数据的采集,并进行超帧分解和控制字段/数据的解析,然后送往计分板跟预期数值进行比对。axi_agent负责对AXI_Lite接口的激励,完成模块寄存器的配置,并进行相关状态寄存器的读取分析。

3.2 cpri_agent的实现

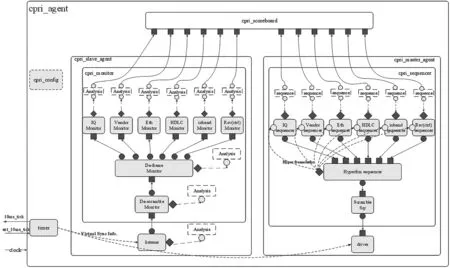

cpri_agent是整个验证平台的关键,由cpri_master_agent、cpri_slave_agent两大主体组成,另外还配备了cpri_config、timer、cpri_scoreboard等辅助功能模块,实现框图如图5所示。

图5 cpri_agent实现框图

对cpri协议的控制字进行梳理,按功能划分有(1)带内控制字即inband,包括超帧号、p指针、协议版本、远程复位和告警等,主要用于同步和层1的管理;(2)slow C&M控制字即HDLC,通过HDLC协议承载层2的管理信息,因为占据的控制字个数少,所以只能用于慢速的信息传递;(3)fast C&M控制字即Eth,通过以太网协议承载层2的管理信息,是标准的以太网封装格式,并且进行了4b/5b的编码,配置的p指针可以在合法范围内数值越小,fast C&M的传输带宽越大;(4)用户自定义控制字即Vendor,这个通常由各厂商自己实现特定用途;(5)保留字段,用于日后的协议扩展。

因此底层的sequencer和monitor就考虑分成六大块,即上述五类控制字再加上IQ数据。

在master_agent中,控制字sequence的产生以超帧为单位,而IQ数据的产生以基本帧为单位,通过sequence级联,汇聚到Hyperfrm sequencer组成超帧格式,再经过scramble sqr进行加扰处理,传递到driver,转换成40b并口的接口方式驱动DUT。各sequence将产生的transction复制一份通过analysis_port发往cpri_scoreboard。

在 slave_agent中,listener负责从interface上采集DUT输出的数据,从同步头开始缓存1个超帧,然后转化为内部的transaction格式传递给Descramble monitor进行解扰处理,De-frame monitor将超帧分解为五类控制字以及IQ数据,分别送往对应的monitor进行分析,之后通过analysis_port发往cpri_scoreboard与预期值进行比对。

timer模块产生内部组帧/解帧的时间信息。外部输入的clock应与cpri的线速相匹配,同时外部输入10ms脉冲标记,依据clock和10ms标签而产生内部的cnt_z(超帧计数,0~149循环)、cnt_x(基本帧计数,0~255循环)、cnt_y(每个W内的字节计数,最大值由cpri的线速决定)、cnt_w(每个基本帧内的W计数,0~15循环)。根据这些计数器可以清晰地定位出超帧中的任意一个位置,从而保证组帧/解帧时的正确性。

cpri_config模块作用于整个cpri_agent,定义并约束了各sequence和monitor需要的变量,罗列了部分如表1所示。

表1 约束项目变量

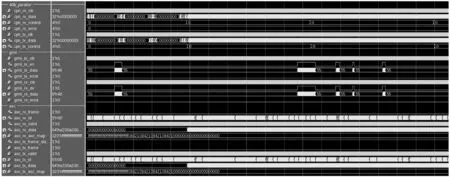

激励成功发送,cpri模块完成同步后,接口上产生正确的数据交互,时序信息如图6所示。

图6 cpri模块接口时序图

3.3 验证结果

本次验证针对rate6和rate8两种速率的cpri接口,参照协议和设计spec进行功能点的测试,对各个功能点对应的功能覆盖率进行统计,得到功能覆盖率为100%,并针对RTL进行代码覆盖率的统计,语句覆盖率可以达到99.3%,状态机覆盖率达到100%。通过UVM验证,计分板对实际报文和预期报文进行实时比对,数据比对的一致性为100%。相关数据可以表明cpri接口的功能需求正确实现。

4 结 语

UVM 作为IC 验证最前沿的方法学,虽然前端仿真搭建平台的周期较长,但是可移植性和扩展性强,用例的编写效率高,可以明显缩短整个研发的验证时间。本文利用sequence级联的方式搭建基于UVM 的CPRI接口模块验证平台,充分验证了CPRI接口模块的功能,为芯片的研发质量保驾护航。这种验证架构可以移植到其他项目中,使得验证平台发挥重要的指导作用,在数字接口的设计中具有重要的应用价值。