浅析PLC中定时器与计数器的设计与应用

2019-11-30丁国明

丁国明

摘 要:该文在对PLC定时器和计数器进行功能需求分析后,对定时器、计数器和高速计数器的控制模块整体结构进行设计,并对其与中央控制器之间进行通信的接口与读写时序进行设计。最终的时序仿真结果表明,该文所研究的PLC定时器和计数器模块工作正常,并充分利用了FPGA的并行执行特点,改进了PLC的定时器和计数器执行效率。

关键词:PLC 定时器 计数器 高速计数器

中图分类号:TM571.61 文献标识码:A 文章编号:1672-3791(2019)09(a)-0042-03

定时器与计数器是PLC(Programmable Logic Controller,可编程逻辑控制器)中最重要的资源之一。PLC内部有众多定时器和计数器资源,而在具体应用过程中,仅有一部分定时器和计数器资源被利用到,造成资源的浪费。为此,该文以西门子PLC S7-30为例,对PLC的定时器和计数器模块进行重构,充分利用FPGA的并行执行特点,将PLC内的定时器和计数器资源划分为多个并行执行的模块,以改进PLC的定时器和计数器执行效率。

1 总体结构设计

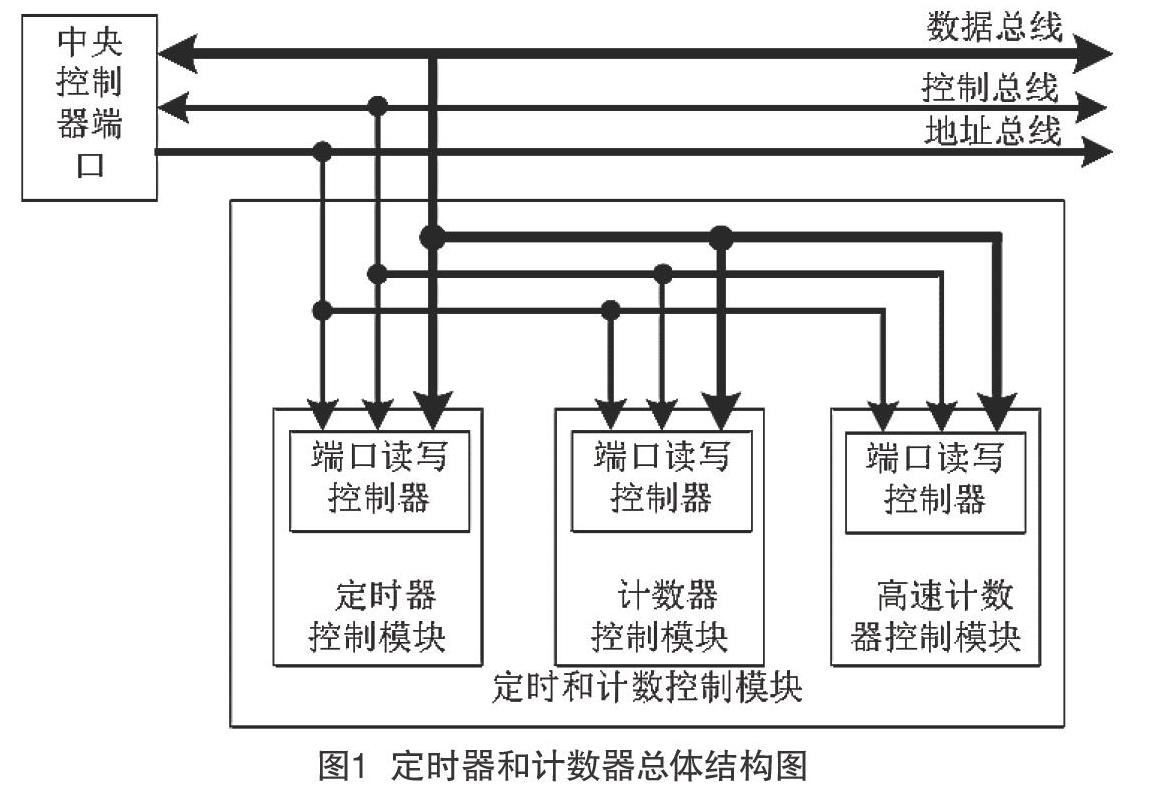

定时器和计数器控制模块的总体结构设计如图1所示。

其中,定时器模块包括1ms、10ms、100ms这3种定时器,计数器分为内部信号计数器(简称计数器)和高速计数器两种。按照断电数据的保持情况,计数器分为断电保持型计数器和通用型计数器两种,高速计数器用于对外部高速脉冲信号进行技术,按照中断方式工作,不受PLC扫描周期影响。

定时器、计数器和高速计数器控制模块并行工作,通过总线和结构、功能相同的端口读写控制器与中央控制器进行的数据交互。

2 控制模块设计

定时器与计数器控制模块的封装如图2所示。

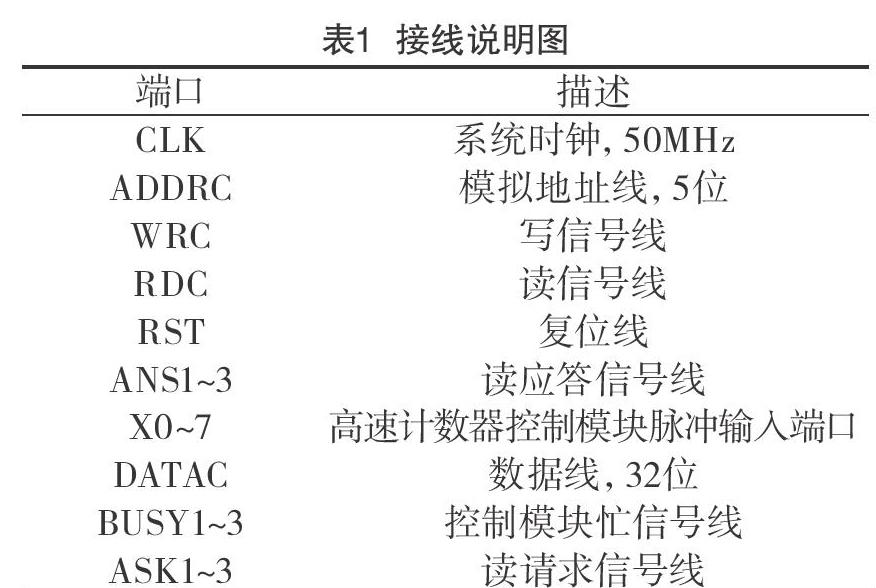

图2的定时器与计数器控制模块接线说明如表1所示。

其中,CLK、ADDRC、WRC、RDC、RST、DATAC端口为定时器、计数器和高速计数器共用的端口,而BUSY1/2/3、ANS1/2/3、ASK1/2/3分别为定时器、计数器和高速计数器控制模块使用的单独使用的忙信号线、中央控制器度应道信号线、读请求信号线。

3 端口读写控制器设计

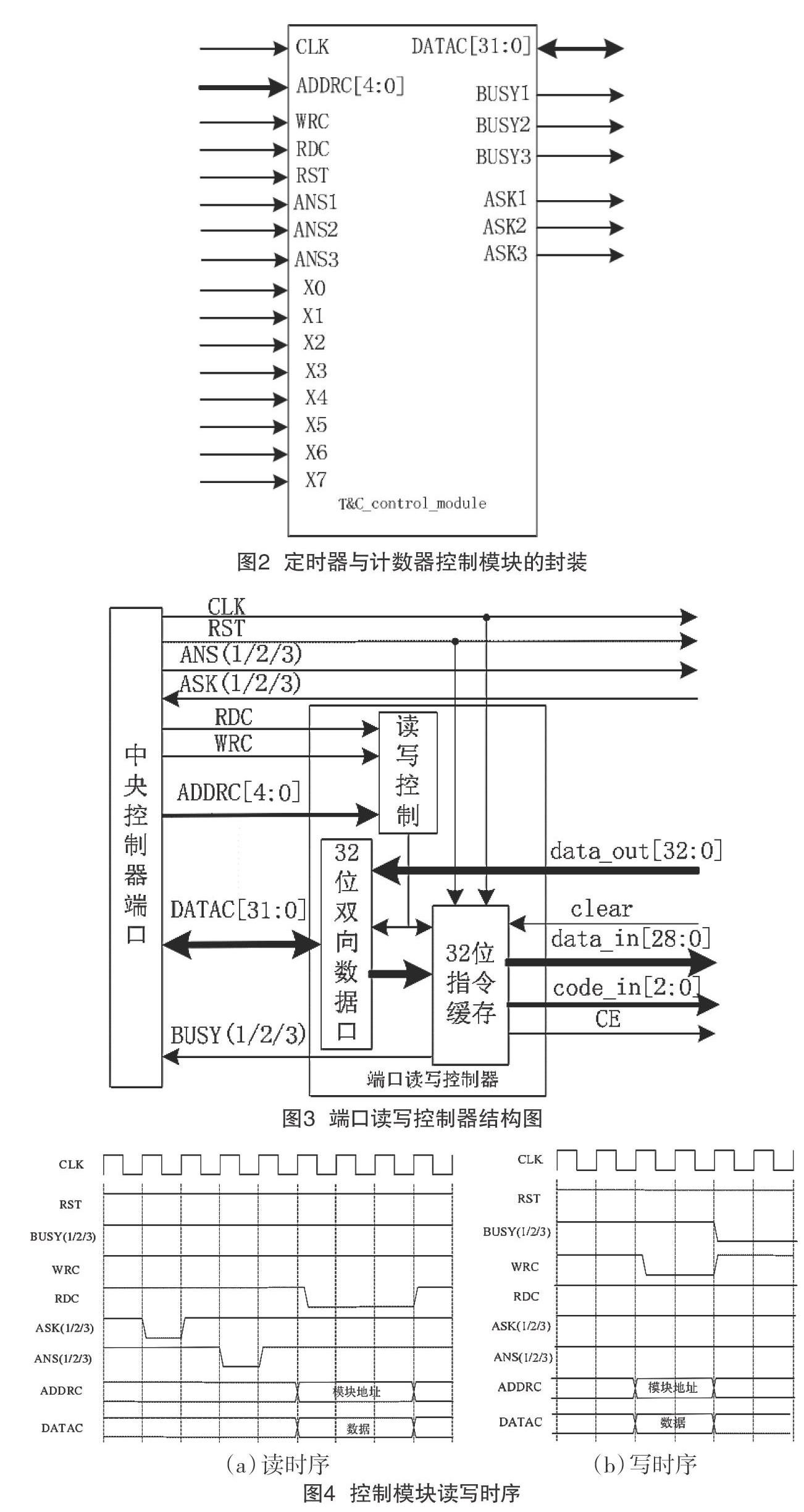

如图1所示,定时器、计数器和高速计数器通过端口读写控制器实现与中央控制器的接口。定时器、计数器和高速计数器的端口读写控制器结构、功能均相同,其结构如图3所示。

若RST复位线的低电平保持时间超过40ns,则触发RST复位,RDC读信号线、WRC写信号线、ASK读请求信号线、读应答信号线均为低电平使能。CE指令执行标志线,当CE、BUSY线为低电平时,实现数据存储。由RDC、WRC和ADDRC状态,控制组合逻辑三态门构成的I/O口,决定读写控制器状态,和数据的输入输出控制。端口读写控制器的指令由3位code_in线输出的D29~D31指令类型,和29位data_in线输出的D0~D28指令数据组成32位指令。若clear线接收到来自指令执行线发送的指令执行结束信息时,设置BUSY线和CE线为高电平,并清除32位指令数据。

控制模块的读写时序设计如图4所示。

如图4所示,当中央控制器检测到BUSY忙信号输出线的电平状态为高电平时,可实现定时器(或计数器,或高速计数器)的写操作,DATAC、ADDRC和WRC的低电平保持30ns以上(时钟周期为20ns)。中央控制器对定时器和计数器控制模块进行读写操作控制时,首先通过ASK发送20ns的请求脉冲,然后读ANS上读来自中央控制器的20ns的应答脉冲,最终通过设置RDC低电平,后可从DATAC线中读取60ns的数据。

参考文献

[1] 徐晓宇,李克俭,蔡启仲,等.基于FPGA的PLC并行执行定时器/计数器的设计[J].计算机测量与控制,2016(1):182-186.

[2] 侯肖霞.关于利用PLC定时器和计数器进行长计时功能的探讨[J].电气技术,2014(2):105-107.

[3] 乔桥.由浅入深学习PLC定时器及计数器的应用[J].中国科教创新导刊,2011(28):205.

[4] 郝敏钗.PLC中定时器和计数器的配合应用[J].科技资讯,2011(12):99.

[5] 李英辉,曲昀卿,郝敏钗,等.PLC中定时器/计数器的拓展应用[J].石家庄职业技术学院学报,2010,22(4):19-21.

[6] 游珍珍.西门子S7-200PLC定时器的实际应用[J].湖南科技学院学报,2017(6):28-29.

[7] 吳国伟.S7-200 PLC定时器的实际应用[J].装备制造技术,2016(5):165-167.

[8] 甄天作.浅谈PLC中定时器的用法及其精度的影响[J].中国高新技术企业,2016(6):76-77.

[9] 陆雪影.基于PLC技术的并行定时器设计研究[J].科技与企业,2016(4):99.