基于ECMA-369的MAC层设计与实现

2019-11-27黄大晴

黄大晴

(南京先锋硕通无线技术有限公司,江苏 南京 211100)

0 引 言

超宽带(Ultra-Wideband,UWB)技术由于具有低功耗、高速率等特点,是无线个域网(Wireless Personal Area Network,WPAN)领域理想的物理层技术。2005年底,由英特尔inter、惠普HP、诺基亚Nokia、三星samsung等国际公司组成的非营利民间组织wimedia联盟的ECMA-368和ECMA-369标准方案[1],由欧洲国际计算机制造商协会推出。ECMA-368标准详细描述了基于多带正交频分利用调制的物理层(PHY)和分布式架构的媒体访问控制层(MAC)。ECMA-369则定义了与ECMA-368相配的接口规范,使得物理层(PHY)和分布式架构的媒体访问控制层(MAC)能够独立实施并互连。

1 MAC层端接口的实现

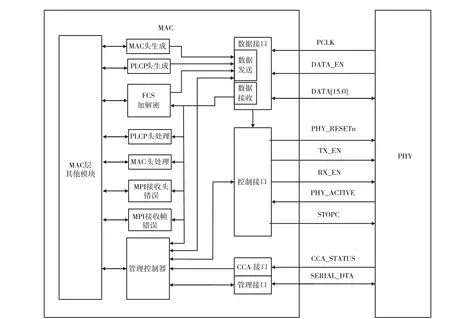

ECMA-369标准规定了ECMA-368中规定的PHY与MAC之间的接口。MAC层端接口主要包括MACPHY Interface中MAC层输出至PHY的接口及与MAC层其他模块的接口,由数据接口、控制接口、CCA接口及管理接口4个模块组成[2-3],如图1所示。

图1 MAC层模块与PHY的接口

(1)数据接口:实现MAC层和PHY层间的数据交互,包括数据发送和数据接收两部分。系统处于发送状态时,系统按顺序依次将PLCP头、MAC头、MAC_PAYLAOD和FCS写入数据发送模块的发送FIFO。PHY每次使能DATA_EN,数据接口将从发送FIFO中取一个数据发送给PHY。系统处于接收状态时,对于每帧,数据接收模块按顺序将接收到的数据发给MAC层的PLCP头处理模块、MAC头处理模块、MPI接收头错误模块、FCS加解密模块、管理控制器模块和MPI接收帧错误模块。

(2)控制接口:控制接口控制PHY复位、系统的数据收发、指示帧接收或发送及开关PCLK。MAC可通过拉低PHY_RESETn来reset PHY;系统要发送数据时,拉高TX_EN,系统进入发送状态;系统要接收数据时,拉高R X_EN,系统进入接收状态;系统进入发送或接收状态后,PHY会在对应的时刻拉高PHY_ACTIVE,指示PHY处于帧发送或接收状态;系统处于STANDBY状态时,可通过STOPC信号来开关PCLK信号。

(3)CCA接口:指示CCA状态。MAC通过管理接口设置CONTROL寄存器的CCRE域为1,发起CCA测量;在CCAValidTime后,CCA_STATUS将被驱动。只要PHY不是处于TRANSMIT、STANDBY或SLEEP状态且CCRE一直为1,CCA将一直进行。

(4)管理接口:读取或者修改PHY层中寄存器。读操作时,管理接口先发送需要读的寄存器的地址给PHY,PHY读到有效地址后将此地址的寄存器值发给MAC;写操作时,管理接口按先后顺序发送地址和数据给PHY。

2 MPI与MAC接口的实现

2.1 数据接口

2.1.1 数据发送

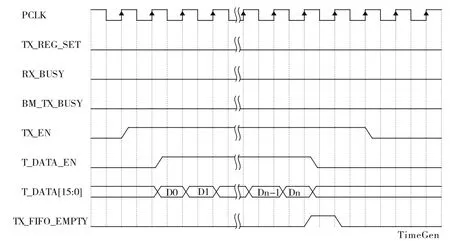

PMMODE在READY状态及TX_REG_SET、RX_BUSY和BM_TX_BUSY都为低的条件下,将TX_EN置高,拉高数据使能信号(图2中,用T_DATA_EN代表 TX_PH_DATA_EN、TX_HD_DATA_EN、TX_PL_DATA_EN),往数据线上写数据,将数据写入发送FIFO。写入的顺序:PLCP头生成模块先往发送FIFO写入总共8 Byte的PLCP头数据;MAC头生成模块写入10 Byte的MAC头数据;由FCS加解密模块写入MAC_PAYLOAD及4 Byte的FCS数据。发送FIFO中数据后,TX_FIFO_EMPTY拉高,表示FIFO中数据发完,MAC拉低TX_EN。系统可以通过拉低TX_EN中断发送操作。TX_EN拉低后,MAC停止将数据发送给PHY。发送中断产生后,可能TX FIFO中还有未发送的数据,可通过TX_FIFO_RST来清空发送FIFO中未发送的数据。图2为数据发送时序图。

2.1.2 数据接收

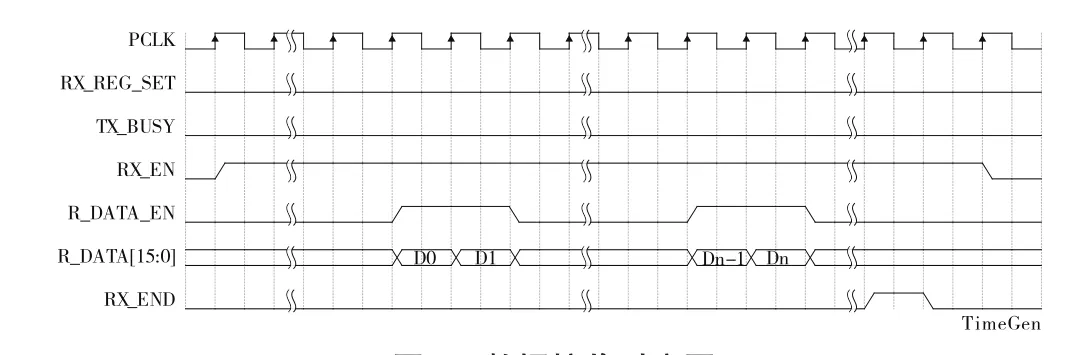

PMMODE在READY状态、RX_REG_SET为低和TX_BUSY为低的条件下,将RX_EN置高,系统进入接收数据状态。接收到数据后,前面5 Byte数据拉高RX_PH_DATA_EN,通过数据线R_DATA[15:0]给PLCP头处理模块;紧接着后面10 Byte数据拉高RX_HD_DATA_EN,通过数据线R_DATA[15:0]给MAC头处理模块;然后1 Byte给MPI接收头错误模块;后面是将MAC_PAYLOAD及FCS拉高RX_PL_DATA_EN,通过数据线R_DATA[15:0]给FCS加解密模块;接着拉高RX_MAN_DATA_EN通过数据线R_DATA[15:0]将接收质量信息给管理控制器模块;最后将RXERROR[4:0]给MPI接收帧错误模块。系统可以通过拉低RX_EN产生接收中断。拉低RX_EN后,PHY需在33个时钟周期内将接收参数传送给MAC和拉低PHY_ACTIVE。如果接收头校验和错误,则按照接收零长度帧的时序来操作。这种情况下,如果系统没有拉低RX_EN,系统将继续接收下一帧数据。图3为数据接收时序图。

图2 数据发送时序图

图3 数据接收时序图

2.2 控制接口与数据接口和MAC层管理控制器的接口

2.2.1 控制接口与数据接口

PAYLOAD_LEN[11:0]是RX控制器模块中的计数器,指示MAC PAYLOAD中还有多少字节数据未接收。

2.2.2 控制接口与MAC层管理控制器的接口

(1)发送控制:系统拉高TX_EN进入发送状态。TX_EN被拉高后,MPI控制接口拉高TX_BUSY和BM_TX_BUSY,在TxHoldTime个时钟周期内拉高TX_REG_HOLD。TX_EN拉低后Tx2RxDwellTime个时钟周期后,TX_BUSY拉低,系统可以进入接收状态;3个时钟后拉低BM_TX_BUSY,如果系统处于突发发送模式,系统可以发送下一帧数据。

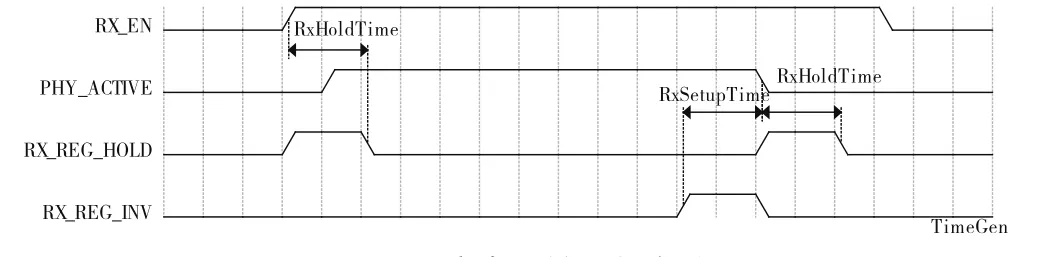

(2)接收控制:系统拉高RX_EN进入接收状态。RX_EN被拉高后,MPI控制接口拉高RX_BUSY,在RxHoldTime个时钟周期内拉高RX_REG_HOLD。RX_EN下降沿后Rx2TxDwellTime个时钟周期后,MAC拉低RX_BUSY。在RECEIVE状态下,在PHY_ACTIVE下降沿之前RxSetupTime个时钟周期内,MPI控制接口将RX_REG_INV拉高。下降沿后,在RxHoldTime个时钟周期内拉高RX_REG_HOLD。图4为RX寄存器控制状态信图。数据接收完成后,PHY会拉低PHY_ACTIVE。PHY_ACTIVE拉低后RxEOFDelay个PCLK时钟周期后,RX_END拉高一个PCLK时钟,表示接收完成,MAC拉低RX_EN。

图4 RX寄存器控制状态信号

2.2.3 管理接口与管理控制器的接口

(1)写PHY寄存器操作。管理接口检测到WR为高、RD为低,系统锁存数据线MAN_TDATA[7:0]和地址线MAN_ADD[7:0]的数据,系统进入管理接口发送状态。如果需要操作的是发送控制寄存器(TXCHAN或TXCTL),必须在TX_REG_HOLD为低的情况下操作。在操作发送寄存器后的TxSetupTime个PCLK时钟内,TX_REG_SET为高电平。如果需要操作的是接收控制寄存器(RXCHAN或RXCTL),必须在RX_REG_HOLD和RX_REG_INV为低的情况下操作。在操作接收寄存器后的RxSetupTime个PCLK时钟内,RX_REG_SET为高电平。

(2)读PHY寄存器操作。管理接口检测到WR为低、RD为高,系统锁存地址线MAN_ADD[7:0]的数据,系统进入管理接口接收状态。管理接口读入寄存器数据后,将信号RDATA_RDY拉高,且将数据放到数据信号MAN_TDATA[7:0]。特殊情况,当PHY在SLEEP状态下时,可同时将TX_EN和RX_EN拉高,这时PHY将进入STANDBY状态。

3 MAC对PHY接口的实现

3.1 数据发送

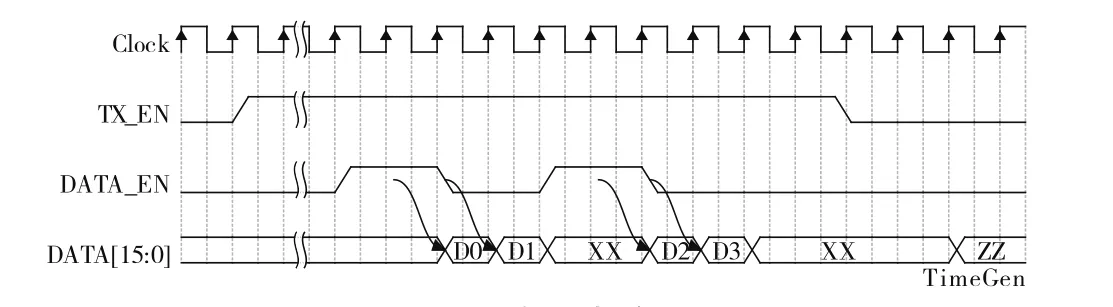

在TX_EN为高电平的情况下,检测到DATA_EN为高,则在一个时钟周期后TX控制器将发送FIFO中的数据置到数据线DATA[15:0]。数据发送完后(发送FIFO数据空),MAC将TX_EN置低。TX_EN下降沿后2个时钟周期,释放数据线的控制权。图5为MAC数据发送时序图。

图5 MAC 数据发送时序图

3.2 数据接收

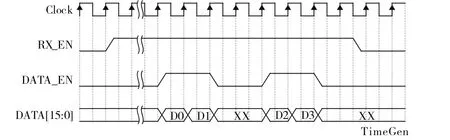

在RX_EN为高的情况下,检测到DATA_EN为高电平,则RX控制器锁存数据线DATA[15:0]上的数据。图6为MAC数据接收时序图。

图6 MAC数据接收时序图

4 结 论

针对ECMA-369标准中规定的PHY与MAC之间的接口,对MAC-PHY Interface中MAC层输出至PHY的接口以及与MAC层其他模块的接口进行设计,利用数据接收时序图和数据接收时序图分析MPI与MAC接口的数据传输。ECMA-369标准中MAC设计实现了设备管理和控制,满足了电子设备之间的通信需求。