基于电导线性技术的高线性折叠CMOS LNA

2019-11-19霍炜李彦锋

霍炜, 李彦锋

(1.西安工程大学 计算机科学学院, 西安 710048; 2.西安蓝海本立信息科技有限公司, 西安 710077)

0 引言

随着CMOS工艺的快速发展,为了使电路取得越来越低的功耗,最直接有效的方法便是降低供电电压[1]。然而,在射频和模拟电路的关键模块中,例如低噪声放大器(LNA)和功率放大器,由于它们具有严格的性能标准,通过降低供电电压来达到降低功耗的目的变得很难实现,并且很难在较低供电电压下,实现较优的线性度。

引起共源放大器非线性的主要因素来自于跨导的非线性[2-4],然而,在较低的电压下,漏极电导非线性也逐渐开始对其造成影响,因而,在低电压LNA设计中,需要同时对漏极电导非线性和跨导非线性进行优化。为了降低跨导的非线性,我们采用多栅晶体管技术,该技术通过对辅晶体管(AT)的尺寸和偏置进行合理选择,来线性化主晶体管(MT)的跨导[5-7]。而且,通过LC折叠共源共栅结构的采用,得到较高的漏极电导线性度。

本文中,首先讨论了低电压LNA的设计方法,然后,基于分析结论,为了在低工作电压下,提高LNA的输入三阶截止点(IIP3),我们建议采用LC折叠共源共栅结构,利用多栅晶体管技术。LC折叠共源共栅结构的采用,可在低工作电压下,利用多栅晶体管技术。并且,该结构减少了谐波反馈分量,确保了较高的漏极电导线性度。最终,本文设计了一款工作于极低工作电压下的,具有较优性能的LNA。

1 考虑线性度的低电压LNA设计

基于泰勒级数展开,共源晶体管结构下晶体管的漏极电流可表示为式(1)[8]。

(1)

其中式(2)。

(2)

上式中,gmx为n阶跨导非线性系数,gdx为n阶漏极电导非线性系数,gdmx为n阶交调系数,RL为负载阻抗,vgs为晶体管栅源极间电压,vds为晶体管漏源极间电压。包含有非线性特性的共源晶体管结构的小信号等效电路,如图1所示。

图1 共源放大器的小信号等效电路

鉴于在典型MOSFET器件中,交调系数非常低,在等效电路中,忽略它的影响,并且,由于2阶非线性系数(gm2,gd2)对IIP3的影响较小,因而在IIP3的计算中,也忽略它们的影响。

由图1以及式(1)和(2),可以推得三阶截止点电压VIP3可表示为式(3)。

(3)

由式(3)可见,VIP3不仅取决于三阶跨导非线性gm3,也由三阶漏极电导非线性gd3所决定,而在传统的高电压LNA设计中,通常忽略gd3的影响。gd3的仿真结果,如图2所示。

图2 gd3随着漏源极间电压变化的仿真结果

随着电压的变小,gd3逐渐增大,例如,0.6 V漏源极间电压下的gd3约是1.2 V下的10倍大小。因此,在低电压LNA设计中,可以采用以下的研究思路:首先,尽可能地增加漏源极间电压,这样可得到较高的电导线性度。然后,由于输出端口处的漏极电导非线性正比例于1/{gd3RL(1/RL+gd1)4}[8],因而,在考虑线性度的问题上,使用较低的负载阻抗RL更好些,但是较低的RL,会导致电路的增益较低,然而,如果采用电流缓冲器结构,如图3所示。

(a) 共源共栅

(b) 折叠共源共栅

例如图3(a)所示的共源共栅结构,可以在不降低RL的前提下,降低M1的负载阻抗,进而实现较优的线性度和增益,因而,共源共栅结构可以优化M1的漏极电导线性度,然而,该结构降低了晶体管M1的漏源极间电压,限制了漏极电导线性度的最优化,这种问题在低电压工作模式下尤其严重。考虑到共源共栅结构的限制,可以采用图3(b)所示的折叠共源共栅结构,此结构可以将晶体管M3的漏源极间电压设置到较高的数值。并且,由于晶体管M4的跨导gm可以表示为式(4)所示的形式,因此可以通过增加M4晶体管漏极电流ID的方法,来降低M4的输入阻抗(=1/gm),进而补偿M3的漏极电导非线性。而在共源共栅结构当中,由于晶体管M1和M2共用相等的漏极电流,限制了M2输入阻抗的可调度。折叠共源共栅结构可以自由地调节晶体管的尺寸和电流,因而可以采用较低的M4输入阻抗优化M3漏极电导的非线性。如式(4)。

(4)

上式中,μn为电子的表面有效迁移率,Cox为单位面积栅氧化层电容,ID为漏极电流,W和L分别为晶体管的沟道宽度和长度。

2 提出的LNA电路设计与测试

导致共源放大器三阶非线性的主要因素来源于gm3和gd3,可以采用多栅晶体管技术降低gm3,采用折叠共源共栅结构,在较低的输入阻抗下优化gd3,并且,LC折叠共源共栅结构也可以抵消二阶谐波分量,进一步优化电路线性度[4][7]。

本文所提出的LNA电路,如图4所示。

图4 提出的LNA电路

M3和M4为共源晶体管,其中M3为主晶体管,M4为辅晶体管。M5为共栅晶体管,M1、M2和M6为偏置晶体管。电容Cdd为脱敏电容,用于降低晶体管栅源极间的二阶谐波分量对三阶互调失真的影响,并且也可以降低栅极噪声对电路噪声系数的贡献[7]。L2和C2构成LC谐振器,谐振频率为900 MHz,即为本文所设计电路的工作频率,LC谐振器在谐振频率下具有最大的阻抗,而在其它频率下的阻抗较低,通过LC谐振器的引入实现降低谐波反馈分量的目的。LC折叠共源共栅结构不仅可以保持较高的漏源极间电压,而且可以降低谐波反馈分量,是低电压LNA电路设计的首选结构。

所提出LNA的芯片照片,如图5所示。

图5 提出的LNA显微镜照片

该芯片基于TSMC 0.13 μm CMOS工艺制造,大小为900 μm×680 μm。芯片在0.6 V电压供电下,消耗了1.26 mW的功耗。辅晶体管偏置于0.23 V下,电路在900 MHz工作频率下的IIP3测试结果,如图6所示。

图6 IIP3随着输入功率变化的测试结果

IIP3取得了3.8 dBm的较高值。IIP3随着辅晶体管偏置变化的测试结果,如图7所示。

图7 IIP3随着辅晶体管偏置变化的测试结果

可见IIP3在较宽的偏置范围0.2 V~0.3 V下都具有较优的线性度。IIP3随着温度变化的仿真结果,如图8所示。

图8 IIP3随着温度变化的仿真结果

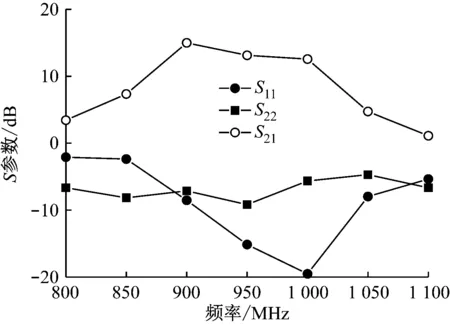

其中将辅晶体管偏置于最优状态下,由辅晶体管开启和关闭的两种状态对比可见,虽然温度发生了较大的变化,辅晶体管在开启状态下仍能够取得较高的数值。S参数和噪声系数NF的测试结果,在900 MHz的工作频率下,增益S21为15 dB,噪声系数NF为1.74 dB,并且输入输出反射系数良好,如图9和图10所示。

图9 S参数测试结果

图10 噪声系数测试结果

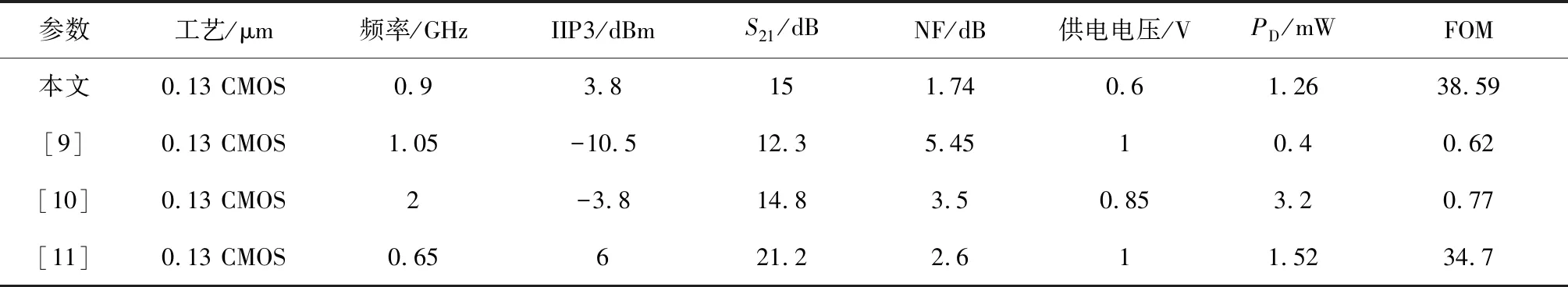

在不大于1 V电压工作下的LNA[9-11],由于技术采用得比较合理,本文所提出的LNA在较低的功耗下取得了较优的线性度性能、较优的增益和噪声系数特性。如表1所示。

表1 低电压LNA比较结果

为了便于比较,采用式(5)所示的优值FOM表达式进行对比[12]。本文设计的LNA取得了最高的FOM值,综合性能最优如式(5)。

(5)

式中,PD为电路所消耗的功耗。

3 总结

本文研究了工作于低电压下高线性度LNA的设计策略,基于该研究结论,提出了采用多栅晶体管技术和LC折叠共源共栅结构同时对跨导以及漏极电导进行线性化。LC折叠共源共栅结构可为主晶体管和辅晶体管提供较高的漏源极间电压,降低了漏极电导非线性对LNA的影响,而且降低了谐波反馈分量,提高了电路线性度。流片实现的LNA在0.6 V电压供电,1.26 mW的功耗消耗下,取得了3.8 dBm的IIP3,15 dB的增益以及1.74 dB的噪声系数。