快速锁定锁相环技术综述

2019-11-13许莎莎卢萌

许莎莎 卢萌

【摘 要】锁相环是把输出相位和输入相位相比较的负反馈系统。快速锁定的锁相环电路一直以来都是锁相环研究工作中的重点。本文对快速锁定锁相环技术做了综述性介绍,归纳得出快速锁定锁相环的发展历程及研究现状。

【关键词】快速锁定;锁相环;专利分析

中图分类号: TN763.3文献标识码: A文章编号: 2095-2457(2019)30-0219-002

DOI:10.19694/j.cnki.issn2095-2457.2019.30.112

1 锁相环技术简介

锁相环是一种自动调节系统,检测两信号的相位差,主要控制的是信号的相位而不是电压幅值。在锁定状态下,锁相环输入信号的相位差值为零或保持不变,如果出现相位差,一种控制机理会作用在振荡器上,之后将振荡器的输出信号反馈回去,使相位差值不断减小,直到最后使输出信号的相位与参考信号的相位相同,保持在锁定状态。下图为锁相环的基本结构,这个控制回路可以使输出信号和输入信号的频率和相位同步。

图1 锁相环的基本结构框图

2 快速锁定锁相环的主流技术

目前针对锁相环的研究工作,大多在选取合适结构的基础上,致力于如何提高电路的性能,包括低噪声、宽输出频带、高输出频率、低工作功耗和低响应时间等性能。其中锁定时间是锁相环的一项重要指标,在快速移动设备和蓝牙收发技术等电子系统中都需要具有快速锁定功能的锁相环。

目前快速锁定锁相环领域的研究主要涉及以下四类:延迟锁相环,电荷泵锁相环,扩展捕获带宽,存储锁定电压。其中延迟锁相环和电荷泵锁相环技术发展较多,技术相对成熟。接下来对主流技术进行说明。

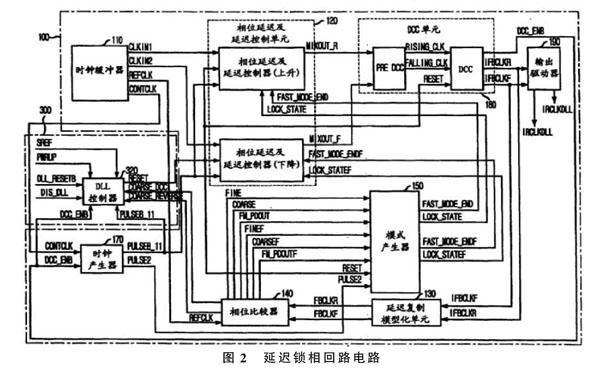

1)延迟锁相环。以一个专利为例说明,申请号为CN200610159334A(发明名称:延迟锁相回路电路,申请人:海力士半导体有限公司)的专利技术方案为(参考图2):提供一种与外部时钟同步地操作的同步存储器装置,其包括:DLL,其用于执行相位更新以产生锁定状态的DLL时钟,并在该锁定状态下以小于一个单位延迟的延迟量实施该相位更新;及控制单元,其用于在该锁定状态被外部变化破坏时重设该DLL,从而使其能够在锁定状态由于指示延迟复制模型化单元的延迟在该锁定状态下的突然变化的外部影响(诸如tCK或电源电压VDD的变化)而被破坏时,迅速再次恢复该锁定状态。

2)电荷泵锁相环。以一个专利为例说明,申请号为CN201610525483(发明名称:一种减小环路锁定时间的锁相环电路,申请人:中国电子科技集团公司第五十八研究所)的技术方案为(参见图3):在该锁相环电路中,电荷泵(CP)的电流源分为两部分,并分别由两个控制电路来控制输出:一个是由鉴相器的输出信号直接控制,另一个是由鉴相器输出信号与相位锁定检测电路输出的Lock信号一同控制。该电路在PLL系统锁定的过程中开启由Lock信号控制的电流源部分来增加CP的输出电流,提高压控振荡器(VCO)控制电压的响应速度、增加环路带宽来减小环路锁定所需的时间,从而实现PLL系统的快速锁定。

图3 一种减小环路锁定时间的锁相环电路

图4

3)扩展捕获带宽。以一个专利为例说明,申请号为CN00800446A(发明名称:锁相环装置,申请人:松下电器产业株式会社)的技术方案为(参见图4):提供一钟锁相环装置,它能根据复制信号检测相位信息,以及根据相位信息的瞬时变化检测频率信息,与模拟锁相环电路的捕获区相比,它具有更宽的捕获区,当锁相环电路被数字化时,本发明能高速执行相位锁定。

4)存储锁定电压。以一个专利为例说明,申请号为CN94109157(发明名称:PLL频率合成器和使用该合成器的高速频率锁定法,申请人:日本电气株式会社)的技术方案为(参见图5):PLL频率合成器包括:AD变换器,存储单元,DA变换器,环路滤波器,压控振荡器,控制單元。其中AD变换器接收频率稳定状态中的频率控制电压并将频率控制电压变换为相应的数字信号;存储单元存储AD变换器发出的数字信号;DA变换器将存储单元中的数字信号变换为相应的频率控制电压模拟信号;控制单元可控制AD变换器和DA变换器的变换,并控制从存储单元读取数字信号;环路滤波器在频率合成器起动之前,将模拟信号的输出电压由控制单元加到压控振荡器上,可稳定地实现高速频率锁定。

图5

3 总结

本文针对快速锁定锁相环的主流技术进行了分析,通过对快速锁定锁相环技术专利文献的研究发现,快速锁定锁相环的技术相对已经很成熟了,随着现代电子技术的发展,对于快速锁定锁相环性能的要求越来越高。我国的快速锁定锁相环技术正处于快速发展的阶段,然而由于起步较晚,与国外还存在一定的差距,因此具有很大的发展空间。

【参考文献】

[1]王丽,CMOS快速锁定锁相环的研究与设计[D].合肥工业大学,2015,04.

[2]任传阳,快速锁定电荷泵锁相环研究与设计[D].山东大学,2016,04.