关于AI算力问题的思考

2019-10-18胡剑浩陈杰男

胡剑浩 陈杰男

【摘 要】人工智能技术已经成为国家发展战略。目前人工智能技术对算力需求与集成电路所能提供支持的差距日益加大,人工智能信息处理平台需要在处理速度、复杂度和功耗等方面有数量级的改善,才能满足人工智能技术在军民领域的应用,因而需要寻求新颖的技术路线解决人工智能的算力问题。介绍了一种颠覆性的技术——概率计算方法,该技术采用了一种类脑的非精确的模糊计算模式。相关研究工作表明,在现有工艺条件下该技术能够满足人工智能系统对处理速度、复杂度和功耗的要求,可以支持未来人工智能系统应用的要求。

【关键词】人工智能;计算能力;概率计算

doi:10.3969/j.issn.1006-1010.2019.08.001 中图分类号:TN929.5

文献标志码:A 文章编号:1006-1010(2019)08-0002-06

引用格式:胡剑浩,陈杰男. 关于AI算力问题的思考[J]. 移动通信, 2019,43(8): 2-7.

Artificial intelligence (AI) technology is an important support of national development strategy. At present, the gap between the computing demand of AI technology and the capability of integrated circuits is increasing. The information processing platform based on AI technology should be improved by orders of magnitude in terms of the processing speed, complexity and power consumption for meeting future military and civilian application requirements. Hence, it is necessary to seek a novel technology roadmap to solve the problem of computing power of AI. This paper introduces a subversive technique, i.e., probability calculation method, which adopts a brain-like inaccurate fuzzy computing model. Relevant research shows that it can meet the requirements of processing speed, complexity and power consumption of AI systems under the current technological conditions, and can support the requirements of future applications of AI systems.

artificial intelligence; computation power; stochastic computation

1 引言

人类世界的信息业务量正在呈爆发式的增长,传统的数字信号处理和统计方式已经难以满足未来的数据和信息处理的需求[1]。在此背景下,出现了一批以机器学习算法为代表的处理算法和系统,来协助人类处理“大数据”时代下的海量信息与数据[2]。同时,随着机器算法的不断发展优化,计算机处理能力的突飞猛进,机器学习算法的能力越来越强,完成的功能越来越强大。最近有关机器学习最出名的案例就是Google的AlphaGo与人类进行的围棋人机大战,AlphaGo完胜了人类顶尖棋手,展现出了机器学习算法和系统的强大分析和处理能力[3-4]。因此,将机器学习算法应用到目前的数字信号处理系统中,这将是未来重要的一个发展和研究方向[5-6],有很高的实用价值和战略价值。

而基于机器学习的大数据处理算法和系统需要极高的计算复杂度,因此对后摩尔时代的计算处理器和芯片提出了巨大的挑战。当前,随着集成电路工艺的发展,芯片的特征尺寸已经接近1 nm的界限[7]。这个界限在工业界看来是基于硅工艺的芯片发展的极限,如若不能突破这个极限,未来的芯片生产和制造将举步维艰。同时一些新兴的技术,如量子计算、碳纳米管等,真正进入实用还有很长的路需要探索[8]。

推动AI技术发展和应用的三大助力是:大数据、算法和算力。很多企业和高校的研究重点都集中在大数据和算法上面,只有Intel、Nvidia等芯片供应商和HP、浪潮等服务器供应商在对算力问题进行研究。本文将简单分析一下对AI算力研究的思考。

2 算力问题目前的技术路线

近年來深度学习的处理芯片蓬勃发展。大致来看可以分为以下几种:

(1)GPU:英伟达以其大规模的[23]并行GPU和专用GPU编程框架CUDA主导着当前的深度学习市场[24]。GPU在处理图形的时候,从最初的设计就能够执行并行指令,从一个GPU核心收到一组多边形数据,到完成所有处理并输出图像可以做到完全独立[25]。由于最初GPU就采用了大量的执行单元,这些执行单元可以轻松地加载并行处理,而不像CPU那样的单线程处理。另外,现代的GPU也可以在每个指令周期执行更多的单一指令。所以GPU比CPU更适合深度学习的大量矩阵、卷积运算的需求[26]。

(2)NPU:中科院研制的人工智能芯片——寒武纪1号(DianNao,面向神经网络的原型处理器结构)、寒武纪2号(DaDianNao,面向大规模神经网络)、寒武纪3号(PuDianNao,面向多种机器学习算法)[27]。CPU、GPU与NPU相比,会有百倍以上的性能或能耗比差距,以寒武纪团队和Inria联合发表的DianNao论文为例,DianNao为单核处理器,主频为0.98 GHz,峰值性能达每秒4 520亿次神经网络基本运算,65 nm工艺下功耗为0.485 W,面积3.02 mm2。在若干代表性神经网络上的实验结果表明[28]:DianNao的平均性能超过主流CPU核的100倍,但是面积和功耗仅为1/10,效能提升可达三个数量级;DianNao的平均性能与主流GPU相当,但面积和功耗仅为主流GPU百分之一量级。另有IBM主导的SyNAPSE巨型神经网络芯片(类人脑芯片)TrueNorth,在70 mW的功率上提供100万个神经元内核、2.56亿个突触内核以及4 096个神经突触内核,神经网络和机器学习负载超越了冯·诺依曼架构[29]。

(3)TPU:张量处理单元(Tensor Processing Unit, TPU)。这是一款由Google开发的,为了机器学习而定制的ASIC,并且经过了TensorFlow的调教。TPU已经在Google数据中心运行了一年多,实践表明它可以为机器学习带来相当出色的每瓦特性能表现。TPU是专为机器学习应用而定制的,它的宽容度更高,可以降低计算的精度(所需的晶体管操作也更少)[30]。

(4)FPGA:在2017现场可编程门阵列国际大会(ISFPGA)上,来自英特尔加速器架构实验室(AAL)的Eriko Nurvitadhi博士展示了有关“在加速新一代深度神经网络方面,FPGA可否击败GPU”的研究。该项研究使用最新的DNN算法在两代英特尔FPGA(Arria 10与Stratix 10)与目前最高性能的英伟达Titan X Pascal GPU之间做了对比评估。和高端GPU相比,FPGA的能量效率(性能/功率)会更好,而且它们还可以提供顶级的浮点运算性能(Floating-Point Performance)。FPGA技术正在快速发展。即将上市的Intel Stratix 10 FPGA能提供超过5 000个硬浮点单元(DSP),超过28 MB的片上内存(M20K),同时整合了高带宽内存(最高可达4×250 GB/s/stack或1 TB/s),以及由新的HyperFlex技术改善了的频率。英特尔FPGA能提供全面的软件生态系统——从低级硬件描述语言到OpenCL、C和C++的高级软件开发环境。使用MKL-DNN库,英特尔将进一步将FPGA与英特尔机器学习生态系统和诸如Caffe这样的传统架构结合起来。Intel Stratix 10基于英特尔的14 nm技术开发,拥有FP32吞吐量上9.2 TFLOP/s的峰值速度。相比之下,最新的Titan X Pascal GPU提供FP32吞吐量11 TLOP/s的速度[31]。

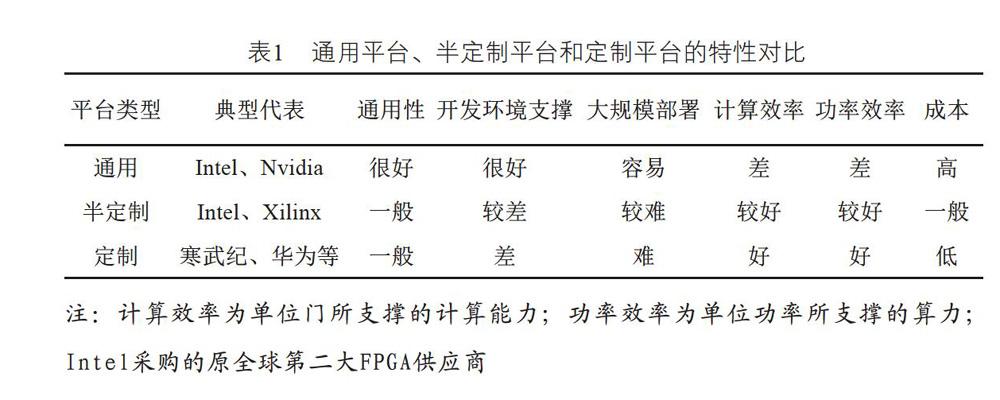

綜上所述,目前工业界解决AI算力有三个方法,通用平台、半定制平台和定制平台。这三种平台的特性对比如表1所示。

从表1可以看出,通用平台在开发软件环境支撑和大规模部署方面有得天独厚的优势,成为AI应用落地和云端部署的主力。因此,当今绝大多数的AI示范工程和云端部署都采用GPU和CPU服务器或服务器阵列完成。然而通用平台在计算效率和功率效率与半定制平台、定制平台有数量级的差距。面向嵌入式应用、移动设备应用,通用平台则难以支撑。对于云端应用,当越来越多的AI应用被部署到云端,功率保障可能会成为其瓶颈。如正在研发的“天河3”超算平台(该平台依然采用CPU+GPU架构),其功率可能达到百万千瓦量级。CMOS工艺已经接近理论极限,而以量子计算为代表的新型计算平台距实际应用还有很长的道路。因此,通过工艺和计算介质进步解决目前通用平台功率效率问题不是十分现实,未来可能会出现发电量不足以支持全社会大规模AI应用的困境。

半定制和定制平台对于嵌入式应用和移动设备应用非常友好,可以成为未来在嵌入式或移动设备实现本地AI应用的主力。由于这些平台在功率效率和计算效率方面的优势,在大规模云端部署也有一定的空间。如阿里云和亚马逊都采用了以FPGA阵列为核心的计算平台。面向半定制和定制平台的大规模部署需要解决软件开发环境支持的问题。现在的AI应用开发已经形成以开源的开发环境为主流的情况,而且这些开发环境支持GPU、CPU平台以及阵列平台。因此,需要解决通用开发环境面向FPGA阵列部署的软件中间件问题,即利用Python设计的AI应用可以一键部署到FPGA阵列平台上,而不需要AI设计者面对硬件描述语言的开发问题。这样才能够很好地解决AI应用在以FPGA阵列为代表的半定制平台上大规模部署的问题。

3 基于概率计算方法的解决方法

计算效率和功率效率是AI算力面临的永恒的挑战,AI应用对算力的需求每3.5个月增加一倍,而基础电路工艺已经进入后摩尔时代,AI系统应用在算力上的“鸿沟”将越来越大。随着集成电路工艺的发展,芯片的特征尺寸已经接近1 nm的界限,如若突破这个极限,未来的芯片生产和制造将举步维艰。同时一些新兴的技术,如量子计算、碳纳米管等,真正进入实用还有很长的路需要探索。因此,目前迫切需求一种新颖数值系统,即数的表征和计算模式来打破传统密集计算的不足,同时该方法可以在现有的集成电路工艺条件下实现且兼容未来的集成电路工艺。

在此背景下,基于概率计算的新型计算方式应运而生。2010年,当基于概率计算的图像处理芯片横空出世后,概率计算的发展就开始突飞猛进了,并且于当年被《美国科技评述》评为未来十大最有前景的技术。此后,MIT的研究团队更是提出了概率计算是继云计算之后最有潜力的一项技术。概率计算中最基本的运算单元采取一种非精确的近似计算的模式打破了传统电路的实现方式,可以对传统的算法进行向概率域的重新映射,使其符合满足概率计算的模式。概率计算再通过误差分析和建模,设计各种系统参数,使其满足系统的需求,最后根据设计的算法映射到实际的电路架构中,完成算法的最终实现。其基本的原理就是利用大量的非精确计算模拟出复杂的系统功能,这其实和人类强大的大脑工作原理不谋而合。人类大脑就是基于大量的直观和非精确的计算方式来处理当今信息社会的海量数据。而AI的算法也是模拟人类的大脑,在此环境下概率计算应运而生,因此概率计算能够非常好地乘载复杂的AI算法。据悉,Google AlphaGo所使用的处理器就是基于一种非精确的概率计算模式。相信基于概率计算和AI的结合能够使得未来的数据处理和信息分析达到一个新的高度。如今人工智能的一个关键障碍是——给计算机提供的自然数据大多是非结构化和“嘈杂”的数据。Intel公司认为,概率计算可以使计算机在处理大规模的概率时更有效率,这是将当前系统和应用程序从先进的计算辅助工具转变为理解和决策的智能合作伙伴的关键。

2018年5月,英特尔人工智能实验室决定对概率计算(Probabilistic Computing)方面的研究增加投资,并呼吁学术界与产业界与其合作,将概率计算从实验室引入现实应用,包括基准程序测试(Benchmark Applications)、概率框架(Probabilistic Frameworks)以及软硬件优化(Software and Hardware Optimization)等[13]。英特尔的人工智能实验负责人Mayberry在接受IEEE Spectrum的采访中提到了MIT的概率计算研究团队,MIT的概率计算团队正在构建新一代概率计算系统,将概率和随机性集成到软件和硬件的基本构建模块中,MIT的PC研究团队,近些年来致力于概率程序语言(Probabilistic Programming)与系统的开发[18]。概率程序语言或称为概率编程为人工智能提供了一个编程语言,并提供了知识如何表示的基础方法,可以对不确定性建模,为不同研究领域的人提供一个工具,在这基础上进行自动推理。国内外各大高校和公司也推出概率编程的工具和库,达到应对不同领域下的智能化与通用化建模与推理。

电子科技大学研究团队从2010年开始尝试利用这种颠覆性的技术,将概率计算方法应用于通信信号处理系统的电路实现上,设计了基于概率计算方法的滤波器、信道译码器、MIMO信号检测器、非正交接入信号检测器等单元模块,在保证这些模块的信号处理性能的前提下,大幅度降低了电路的复杂度。电子科技大学研究团队目前正在探索基于概率计算方法的新型数值表征和计算技术在人工智能系统中应用的特点,研究典型人工智能算法到概率计算空间的算法映射方法,设计关键模块及其电路架构,突破可配置概率计算人工智能硬件加速器设计方法和集成电路实现技术。目前利用FPGA完成的支持100维的支持向量机(SVM)特征分类器实现,其速度较GPU服务器提高30倍,同时功耗降低了100倍。这表明概率计算方法在解决AI应用算力问题是有前途的。

4 基于概率计算方法的AI芯片面临的挑战

随着信息技术的发展,人们对数据的需求也日益增长,人类将逐步跨入大数据时代,而作为大数据时代的一个重要支撑就是人工智能技术(AI)。然而随着AI算法的复杂度呈指数增加,这会对基于AI的系统带来巨大的压力,因此必须利用颠覆性的方案来设计和实现面向未来的AI芯片,以使得其所带来的巨大优势能够真正得以实现和应用。概率计算方法是解决这一技术难题的途径之一,同时面临如下的技术挑战:

(1)基于AI算法的概率计算基本计算单元设计与实现

当前的人工智能算法主要利用了类脑的计算,而这种计算的概率性质允许数量级的加速和减少电力的大量消耗。计算以偏离而不是采用直接的方式来建模,随后可以通过嘈杂自然数据(异同甚至相互矛盾的信息)分析技术提高计算精度,其目的是在需要高智能、认知等场景中协助人类的选择行为达到期望的水平,同时将能源的成本节省到忽略不计的程度。其核心思想是基本算子映射、概率框架、软件和硬件优化。因此,需要研究一种适用于AI芯片设计的基本计算单元设计与实现方法。

(2)基于人工智能的概率计算算法映射方法

首先将AI算法映射到概率域中,称之为规则的映射,其次将构建概率算子并使其能够产生所需的结果称之为目标的映射,最后将信号处理与学习搜索网络相对应和加工,使得其能够高效完成所指定的目标。由此可得在传统AI中,物理参数模型都是人为构建的,这在特定场景设计下的AI芯片必定是最优的。但如前面所述,随着AI算法的发展,这种模式将难以为继。因此只要基于概率计算将映射规则和基本算子等定义清楚,就能辅助完成AI芯片的设计。为了适应AI算法快速变化的需求,本项目采用的认知计算的模型和算法具有高效和快速收敛的特征;同时该方法具有低复杂度的特点,从而可以保障在工程实践中的应用。前期的研究表明,在典型的AI算法环境中,基于概率计算的AI设计法可以在保证检测性能的条件下满足“在线”实时处理的要求,且硬件实现效率优于传统检测方法。因此,需要研究一种基于人工智能的概率计算算法映射方法。

(3)高性能的概率AI芯片的实现设计方法

对AI的概率计算基本运算模块进行硬件架构设计,并且针对当前的工艺,给出设计和实现方案。根据之前形成的映射方法和基本单元的设计,形成一套完整的芯片架构设计和实现方案。最后制作一套针对所设计人工智能芯片的测试平台,来验证所设计芯片的正确性。

5 结束语

满足未来的新型人工智能装备及产业的需求,不能简单地认为仅仅依靠硬件平台就可以解决所有问题。原来依赖集成电路技术进步来适应系统需求增长的“老路”已经走到头了。而系统和装备依然需要不断的更新和升级,因此需要从算法、算法架构、算法的表征和实现技术、系统优化等方面开展深入的研究,才能在新的时代条件下,支持人工智能裝备及产业快速发展的需求。因此,概率计算将为人工智能爆发式的增长提供有力的支持;需要研究以概率计算方法在人工智能系统应用为核心,研究面向人工智能系统的概率计算方法及其集成电路的实现技术,为未来人工智能系统应用提供新颖的技术路线和保障。

参考文献:

[1] Glorol X, Bonles A, Bengio Y. Deep sparee rectifier neural networks[C]//International Conference on Artificial Intelligence and Statistics. Piscalaway, NJ, USA: IEEE, 2011: 315-323.

[2] Deng J, Dong W, Socher R, et al. ImageNet: A large-scale hierarchical image database[C]//IEEE Conference on Computer Vision and Pattern Recognition. Piscataway, NJ, USA: IEEE, 2009.

[3] 張荣,李伟平,莫同. 深度学习研究综述[J]. 信息与控制, 2018,47(4).

[4] Lecun Y, Bengio Y, Hinton G. Deep learning[J]. Nature, 2015,521(7553): 436.

[5] Ghahramani, Zoubin. Probabilistic machine learning and artificial intelligence[Z].

[6] Wang S, Zhang X, Li Y, et al. Accelerating Markov Random Field Inference Using Molecular Optical Gibbs Sampling Units[C]//ACM IEEE International Symposium on Computer Architecture. IEEE, 2016.

[7] Zhang X, Bashizade R, Laboda C, et al. Architecting a Stochastic Computing Unit with Molecular Optical Devices[C]//ACM IEEE International Symposium on Computer Architecture. IEEE Computer Society, 2018.

[8] Cusumano Towner, M F, Mansinghka, et al. A design proposal for Gen: Probabilistic programming with fast custom inference via code generation[C]//In Workshop on Machine Learning and Programming Languages (MAPL, co-located with PLDI). 2018: 52-57.

[9] Cusumano Towner, M F, Mansinghka, et al. Using probabilistic programs as proposals[C]//Workshop on Probabilistic Programming Languages, Semantics, and Systems (PPS, co-located with POPL). 2018.

[10] Cusumano Towner, M F, Bichsel, et al. Incremental inference for probabilistic programs[C]//Proceedings of the 39th ACM SIGPLAN Conference on Programming Language Design and Implementation (PLDI). ACM, 2018: 571-585.

[11] Saeedi A, Kulkarni T D, Mansinghka V K, et al. Variational particle approximations[J]. Journal of Machine Learning Research, 2014.

[12] Cusumano Towner M F, Mansinghka V K. AIDE: An algorithm for measuring the accuracy of probabilistic inference algorithms[Z]. 2017.

[13] Nepal K, Hashemi S, Tann H, et al. Automated High-Level Generation of Low-Power Approximate Computing Circuits[J]. IEEE Transactions on Emerging Topics in Computing, 2019(1): 18-30.

[14] Cusumano Towner M F, Radul A, Wingate D, et al. Probabilistic programs for inferring the goals of autonomous agents[Z]. 2017.

[15] Schaechtle U, Saad F, Radul A, et al. Time Series Structure Discovery via Probabilistic Program Synthesis[Z]. 2017.

[16] Saad F, Casarsa L, Mansinghka V. Probabilistic Search for Structured Data via Probabilistic Programming and Nonparametric Bayes[J]. 2017.

[17] Saad F, Mansinghka V. Detecting Dependencies in Sparse, Multivariate Databases Using Probabilistic Programming and Non-parametric Bayes[J]. Proceedings of the 20th International Conference on Artificial Intelligence and Statistics, 2017(54): 632-641.

[18] Chien C, Longinotti L, Steimer A, et al. Hardware Implementation of an Event-Based Message Passing Graphical Model Network[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2018,65(9): 2739-2752.

[19] Yi Wu, Lei Li, Stuart Russell, et al. Swift: Compiled Inference for Probabilistic Programming Languages[Z]. 2016.

[20] Shi J, Chen J, Zhu J, et al. ZhuSuan: A Library for Bayesian Deep Learning[Z]. 2017.

[21] Tran D, Hoffman M D, Saurous R A, et al. Deep Probabilistic Programming[Z]. 2017.

[22] Bingham E, Chen J P, Jankowiak M, et al. Pyro: Deep Universal Probabilistic Programming[Z].

[23] Coyle P. Probabilistic Programming and PyMC3[Z]. 2016.

[24] Rejimon T, Bhanja S. Scalable probabilistic computing models using Bayesian networks[C]//Symposium on Circuits & Systems. IEEE, 2005.

[25] Davies M, Srinivasa N, Lin T H, et al. Loihi: A Neuromorphic Manycore Processor with On-Chip Learning[J]. IEEE Micro, 2018: 1.

[26] Sze V, Chen Y, Yang T, et al. Efficient Processing of Deep Neural Networks: A Tutorial and Survey[J]. Proceedings of the IEEE, 2017(12): 2295-2329.

[27] Xu J, Huan Y, Yang K, et al. Optimized Near-Zero Quantization Method for Flexible Memristor Based Neural Network[J]. IEEE Access, 2018: 29320-29331.

[28] Ren L, Fletcher C W, A Kwon, et al. Design and Implementation of the Ascend Secure Processor[J]. IEEE Transactions on Dependable and Secure Computing, 2019,16(2): 204-216.

[29] Knag P, Kim J K, Chen T, et al. A Sparse Coding Neural Network ASIC With On-Chip Learning for Feature Extraction and Encoding[J]. IEEE Journal of Solid-State Circuits, 2015,50(4): 1070-1079.

[30] Shin D, Lee J, Yoo H. DNPU: An Energy-Efficient Deep-Learning Processor with Heterogeneous Multi-Core Architecture[J]. IEEE Microwave, 2018,38(5): 85-93.

[31] Lee J, Kim C, Kang S, et al. UNPU: An Energy-Efficient Deep Neural Network Accelerator With Fully Variable Weight Bit Precision[J]. IEEE Journal of Solid-State Circuits, 2019,54(1): 173-185.★