4K裸眼立体显示系统设计

2019-10-17宋振声刘银萍刘卿卿蔡静怡

严 飞,宋振声,刘银萍,刘卿卿,2,蔡静怡

(1. 南京信息工程大学 自动化学院,江苏 南京 21004;2. 江苏省大气环境与装备技术协同创新中心,江苏 南京 210044;3. 南京信息工程大学 大气物理学院,江苏 南京 210044)

1 引 言

视觉在人们日常生活中扮演着重要的角色,研究表明人类80%的环境信息是通过视觉获取的[1],这说明视觉是人们获取外界信息最主要的方式。近年来,随着3D电影行业的火热,立体显示技术被推向一个新的发展热潮。立体显示具有很好的立体感和纵深感,被广泛应用于医疗等领域[2]。

在国外,2010年世界上首例3D内窥镜微创手术在英国吉尔福德顺利实施[3]。BAlaraimi等人于2014年针对3D内窥镜摄像系统与传统2D内窥镜系统的优劣做了相关研究。研究发现,对于未经过视觉问题矫正的新手来说,他们操作3D内窥镜系统时可以更快地上手,并且重复操作和操作错误次数均比他们操作传统2D内窥镜要少[4]。Storz等人在比较传统的2D内窥镜系统和3D内窥镜系统时,针对操作精度和工作速度方面进行了测试研究。在其中的4项任务中,参与者在3D系统中操作的错误和操作的时间比2D系统下少。有经验的外科医生在3D系统下操作困难的任务时则节省了更多的时间[5]。Sinha等人对 200例3D腹腔镜手术和200例2D腹腔镜手术进行了分析,统计结果直接体现了3D内窥镜较传统2D系统在手术时的优势[6]。另外,一些研究表明,3D内窥镜摄像系统在微创手术中的表现都要优于传统的2D内窥镜系统[7~9]。Kong等人对3D内窥镜系统与传统2D系统的性能进行了比较。在这项研究中,新手在使用2D和3D操作时间上没有太大的差异,但是3D系统上的操作误差明显比2D要少[10]。

在国内,2012年首例3D内窥镜下肾盂旁囊肿切除术在于北京协和医院顺利进行[11]。蒋堃等人针对传统内窥镜和3D内窥镜技术治疗效果进行了对比研究[12]。就肾上腺肿瘤切除术的案例对比发现,使用3D内窥镜系统进行手术的时间比传统内窥镜手术时间缩短很多,并且手术中出血量也少。李汉忠和刘皓等分别就3D内窥镜系统在泌尿外科手术和膀胱前列腺切除手术中的成功应用[13-14],国内首例3D内窥镜在神经外科手术中成功实施,见证了3D内窥镜在高难度手术中的成功应用[15]。由此可见,3D内窥镜提供的3D医疗影像给医生带来很好的立体视野的优势,并且手术操作准确性大大提高。

针对3D内窥镜摄像系统的研究,Liu等人提出以FPGA为核心的小体积、低成本、高性能的辅助式3D内窥镜系统,能显著降低手术体腔损伤的风险[16]。也有部分学者利用其他技术手段对传统2D内窥镜进行立体化处理,例如Oh等人提出的对2D腹腔镜成像系统进行三维重建的研究[17]。另外,Lee等人提出的利用特征追踪技术对内窥镜系统进行深度采样进而生成深度图,可以将传统的2D内窥镜视频进行3D可视化转换[18]。Zhao等人提出了一种基于交互式三维导航系统的图像导航手术,可以提高医学成像效果和诊断准确性,为图像引导手术相关方向提供了参考价值[19]。

综上所述,立体显示已经被证实能够为医生诊断病人提供非常好的帮助。本文拟开发一种基于FPGA的4K裸眼立体显示系统,旨在为医用高清晰3D显示领域提供一种切实可行的设计方案。

2 系统组成

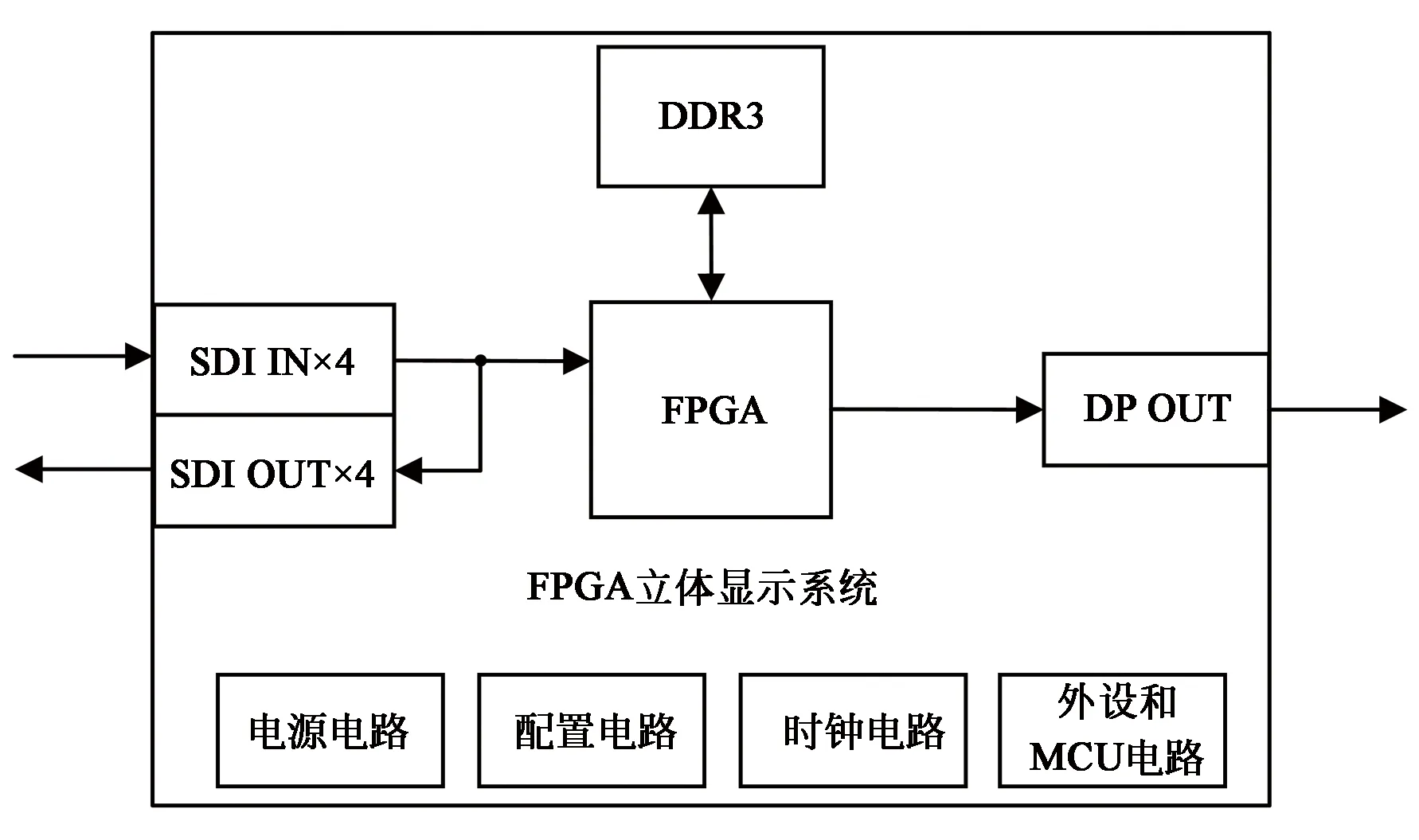

立体显示系统控制卡如图1所示,包括4路SDI输入接口、4路SDI环路输出接口、DP输出接口、DDR3存储模块以及外围电路(电源电路、配置电路和时钟电路)模块,硬件组成部分如图2所示。其中,4路SDI输入接口在FPGA逻辑设计时仅用了2路,其余两路输入为冗余设计。

系统支持3G-SDI视频输入和DP 1.2视频输出。系统主控芯片使用的是型号为XC7K325TFFG900-2的一款FPGA,属于Xilinx 公司Kintex 7系列。

图1 立体显示系统控制卡Fig.1 Control card of stereo display system

图2 立体显示系统硬件组成Fig.2 Hardware components of three-dimensional display system

据FPGA特性如下:

(1)采用FFG900封装,速度等级为-2;

(2)拥有16个GTX(GTX Transceivers,7系列FPGA高速吉比特收发器)收发器,传输速率高达6.6 Gbit/s;

(3)拥有500个I/O,分别有350个支持1.2 V至3.3 V I/O电压的HR(High-range,高范围)I/O和150个支持1.2~1.8 V I/O电压的HP(High-performance,高性能)I/O。其中高性能I/O口为FPGA与外部高速器件之间数据交互提供保障。

该系统采用模块化的设计思路,对系统图像采集模块、图像格式解析模块、图像处理模块以及图像输出模块进行详细设计。其中图像处理模块包括图像缩放、图像缓存以及图像拼接。

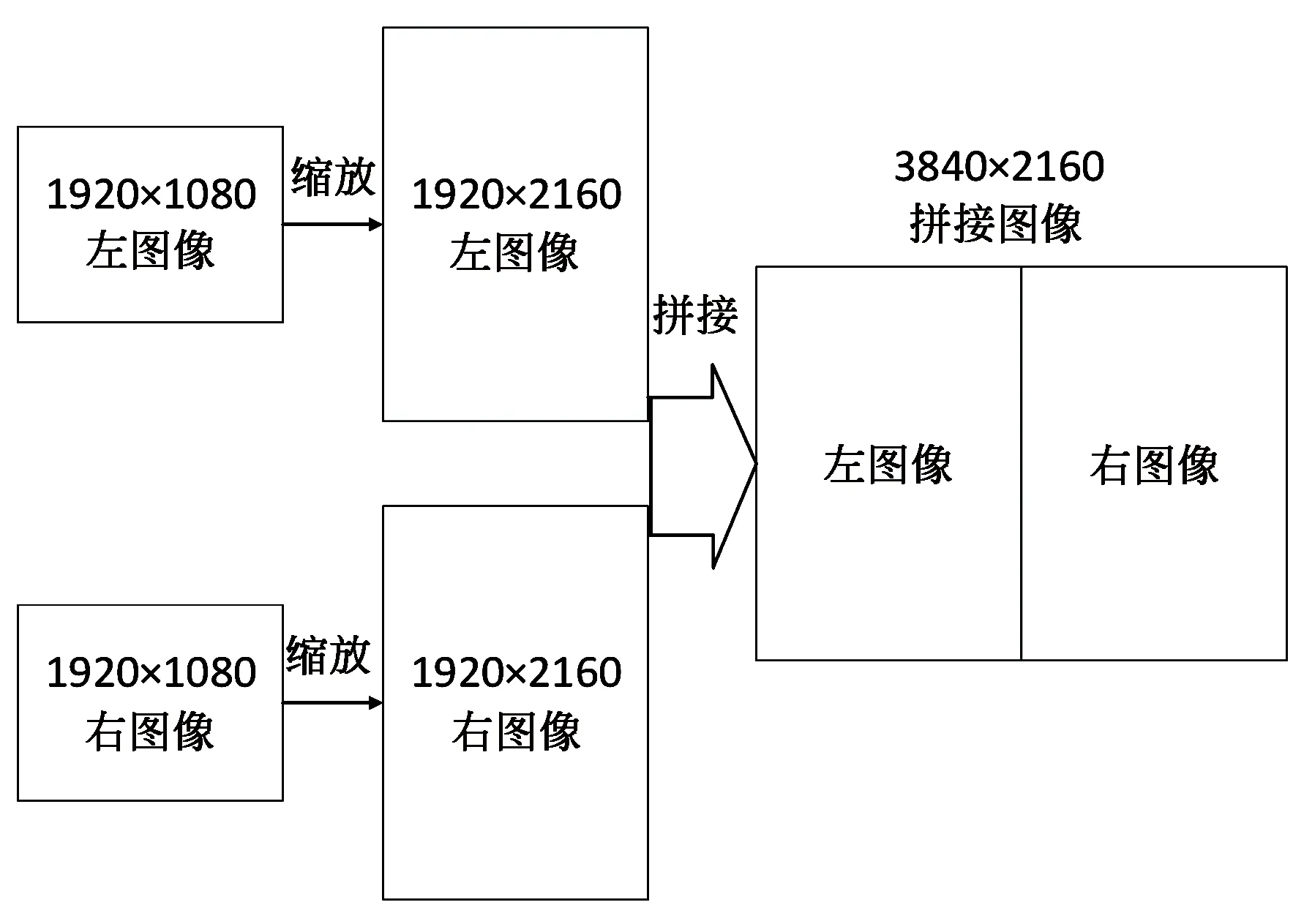

前端采集到的图像经过缩放处理、同步缓存后再拼接输出。图像输入为1 920×1 080,经过缩放模块后放大至1 920×2 160,最后两路视频拼接为4K(3 840×2 160)输出,输出的图像采用SBS拼接方式。图像处理过程如图3所示,在设计各个模块时,以单路图像处理的方式进行设计,当两路图像同时处理时,能够直接复用部分功能模块,以达到节约资源的目的。

图3 本文图像处理流程Fig.3 Image processing process in this paper

3 3G-SDI图像输入解析

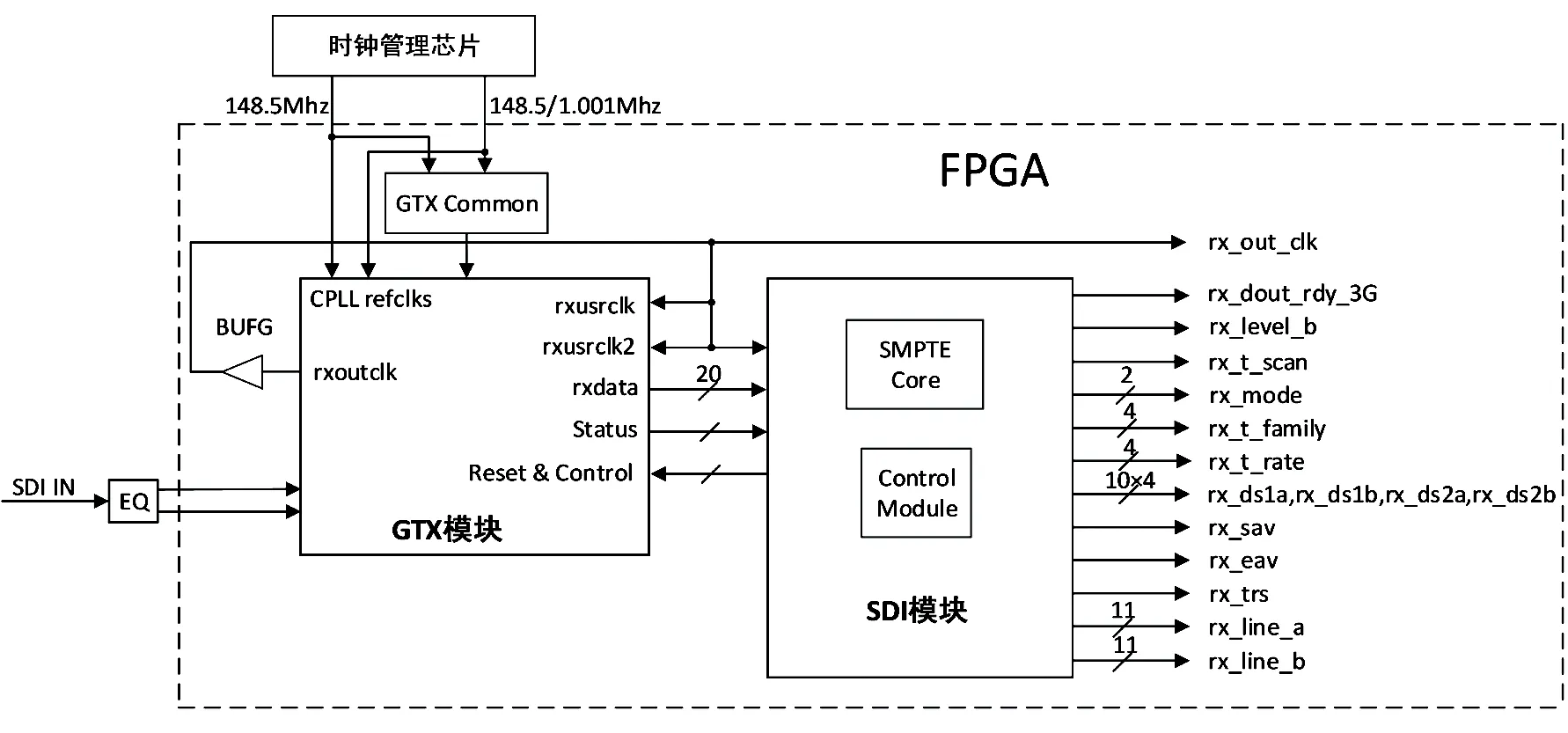

SDI输入参考时钟为148.5 MHz和148.5/1.001 MHz,硬件上由时钟管理芯片SI5338提供。另外,该参考时钟频率也兼容HD-SDI模式。SDI输入逻辑设计框图如图4所示。

SDI输入逻辑设计模块中,主要包括GTX模块以及SDI模块。GTX模块包含GTX收发器(7 Series FPGAs Transceviers),根据GTX收发器的结构特性,其参考时钟可以直接接入CPLL或者通过GTX Common模块接入QPLL。

图4 SDI输入逻辑设计框图Fig.4 Block diagram of SDI input logic design

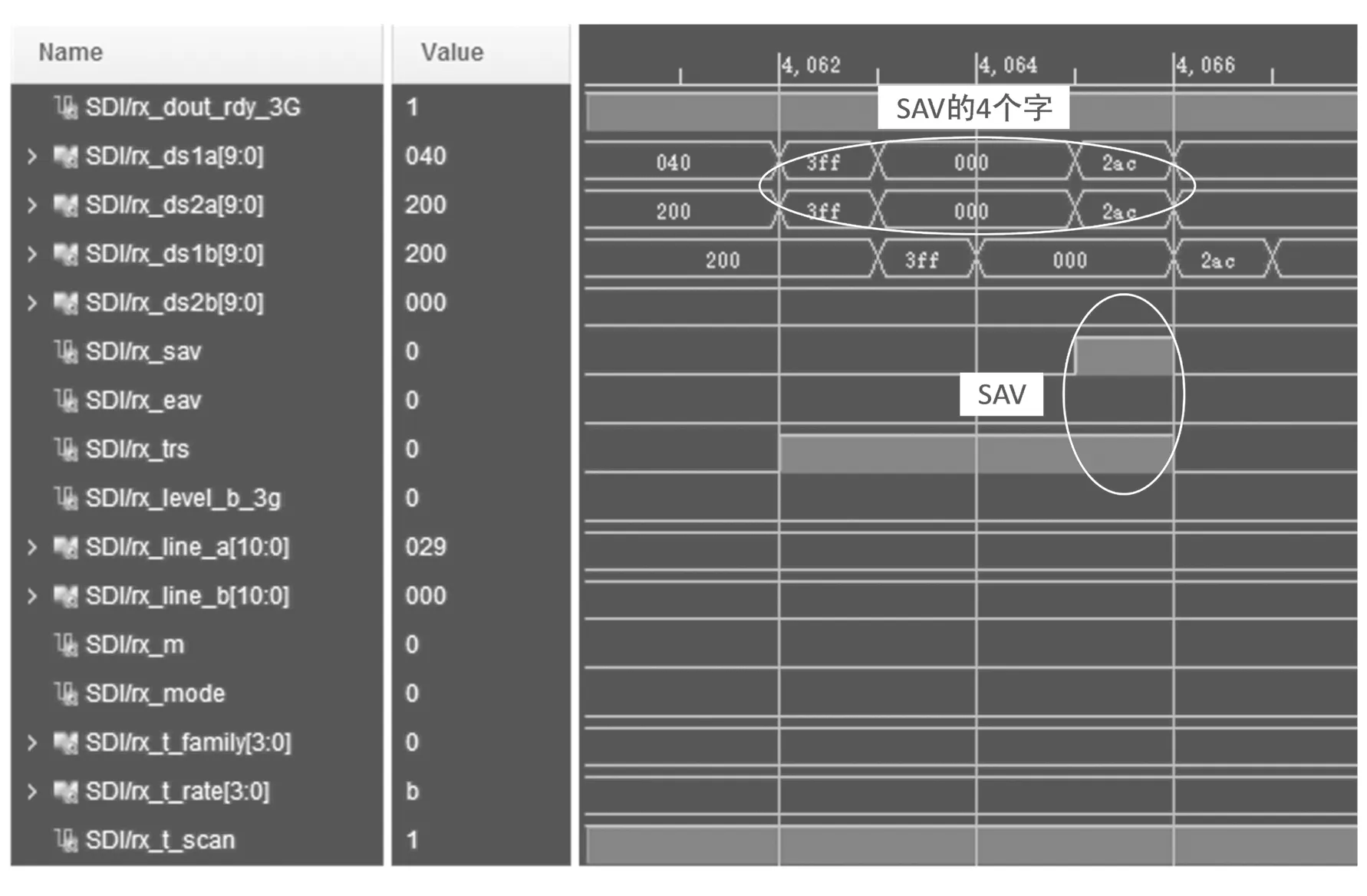

SDI模块包含SMPTE Core和Control模块。SMPTE Core支持SD-SDI、HD-SDI、3G-SDI Level A、3G-SDI Level B-DL和LeveB-DS传输模式,在本文中仅讨论3G-SDI传输模式。Control模块用于当SDI输入模式改变时重配置GTX核以及实时检测SDI输入比特率。SDI模块输出的rx_ds1a、rx_ds1b、rx_ds2a和rx_ds2b为视频数据,其中rx_ds1a和rx_ds2a用于输出视频信号的亮度分量,rx_ds1b和rx_ds2b用于输出视频信号的色彩分量。仅当传输3G-SDI level B信号时,rx_ds2a和rx_ds2b才有有效值输出。

图5 3G-SDI Level A 解析Fig.5 Analysis of 3G-SDI Level A

在3G-SDI Level B模式下,数据流双链路传输,在链路上存在EAV的4个字时,rx_trs信号被置高。采集到的数据如图5所示,rx_level_b_3g为高电平,表示当前传输的是3G-SDI Level B视频流。

解析后的图像需要进行YUV到RGB的格式转换,然后使用Xilinx提供的VPSS核实现图像缩放,每路视频放大至1 920×2 160再拼接输出,下节重点阐述图像的缩放过程。

4 图像缩放

本文使用VPSS核实现双三次插值缩放算法仅适用于逐行扫描的图像,即需要输入图像满足从左到右和从上到下的扫描方式,有效输出图像也按此顺序给出。

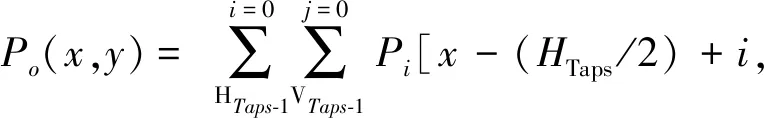

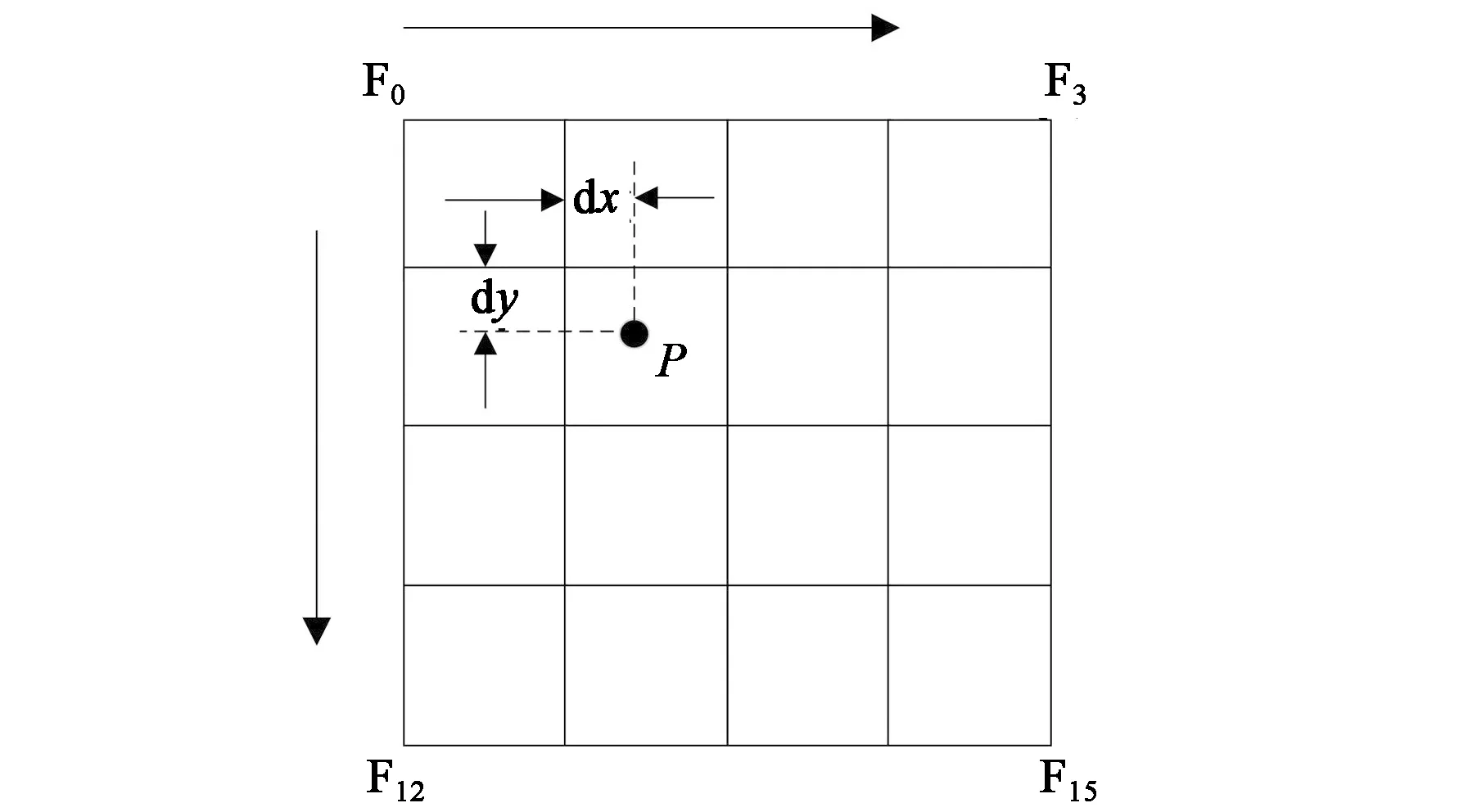

视频缩放是一种二维滤波操作形式,可以近似为公式(1)。其中,x和y是图像上离散的像素点的坐标,Po(x,y)是在(x,y)位置生成的输出像素;Pi(x,y)是参与运算的输入图像的(x,y)位置的像素;在双三次插值缩放算法中,C(i,j)是取决于双三次插值基函数的系数数组;HTaps和Vtaps分别为滤波器中的水平和垂直步长,在双三次插值中,步长为4,即新产生的像素是由源图像中16个关联像素点计算而来。

(1)

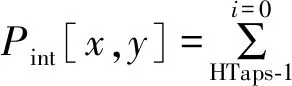

缩放模块中,先对图像进行垂直滤波运算,产生一个中间结果Pint,见式(2),A[i]是垂直插值系数权重。

(2)

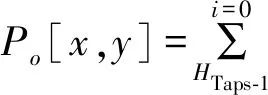

垂直分量的输出结果Pint输入到水平滤波运算中,见式(3),B[i]是水平插值系数权重。

(3)

垂直和水平运算分离意味着可以简化乘法操作,以达到节省FPGA资源的目的。例如,在图像缩放过程中,输出期望像素P在源图像中的位置如图6所示,F0~F15为点P关联的16个像素。

图6 期望像素的位置Fig.6 Position of the desired pixel

系数权重通过将期望像素位置的小数部分dx和dy计算得出,水平方向系数权重A[i]和垂直方向系数权重B[i]如式(4)所示。

在双三次插值算法中,采用不同的插值基函数,其计算量以及缩放效果都有所不同,常用的基函数如keys的双三次插值基函数如式(5)所示,它是一个连续并且具有连续一阶导数的函数。

(4)

(5)

通常来讲,FPGA执行插值运算时,插值系数数组的权重值被定义成一个小型的查找表,这样可以节省FPGA运算资源的使用。

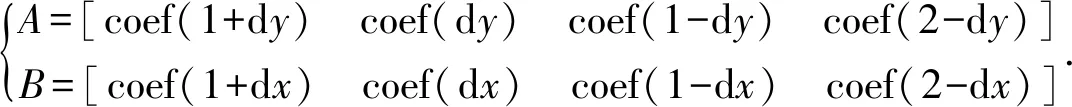

图像缩放模块逻辑架构如图7所示。AXI4总线用于配置Scaler模块的工作模式,图像先经过Video In to AXI4-Stream模块转换成AXI4S的形式输入到Scaler模块,在Scaler模块内图像并以AXI4S的形式参与运算及输出。Video Timing Controller与AXI4-Stream to Video Out协同工作,vtg_ce信号用于使能Video Timing Controller输出时序给AXI4-Stream to Video Out用于输出图像数据以及时序。

图7 缩放模块逻辑架构Fig.7 Logical architecture of scaling module

缩放后,将两路分辨率为1 920×2 160的图像存储到内存中,读取时采用左右拼接的输出方案,实现3 840×2 160的图像数据流,然后将该数据流按照DP图像时序输出,即实现双路3G-SDI图像的SBS格式输出。

5 DP图像输出

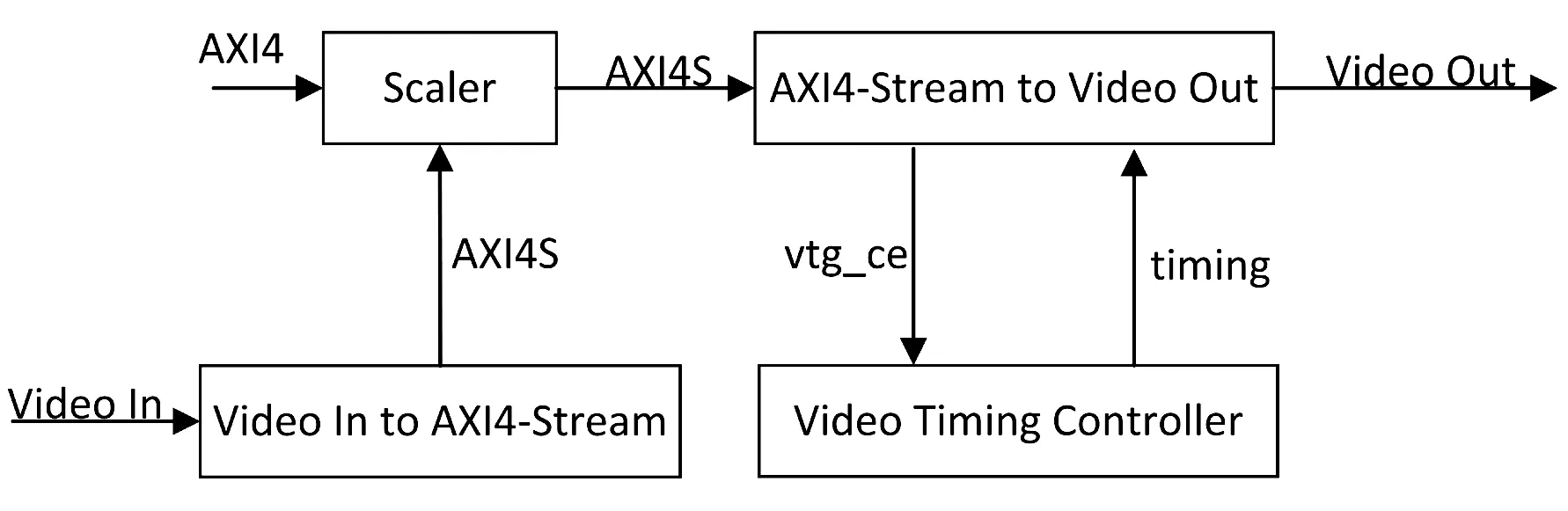

根据裸眼3D显示器的技术规格,需提供固定拼接方式的3D图像输入格式。有2种拼接方式的3D图像格式,分别为SBS和TOP-BOTTOM的拼接方式。SBS拼接方式即左边一半为左图,右边一半为右图。TOP-BOTTOM即左、右图上下排布,上一半为左图,下一半为右图。该系统采用SBS拼接方式,拼接后的图像采用DP 1.2接口输出,输出逻辑设计框图如图8所示。

图8 DP输出逻辑设计图Fig.8 Diagram of DP output logic design

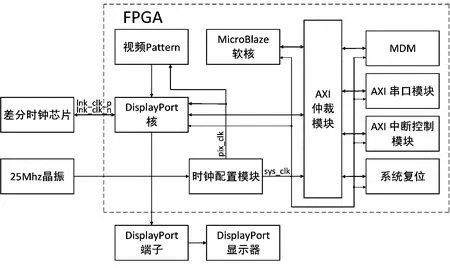

输出部分包括时钟配置模块、系统复位模块MicroBlaze处理器、AXI 仲裁模块和一些AXI4接口的外设。AXI4外设包括串口UART模块、中断控制模块和DP核。各模块之间通过AXI4总线挂在AXI仲裁模块上。视频信号由DP核输出,通过DP端子输出到带有DP接口的显示器。

图像输出模块的设计,包括图像输出逻辑设计图中的硬件时钟配置、输出接口配置、图像输出时序以及MicroBlaze 软核控制流程几个部分,旨在输出3 840×2 160@60 Hz的图像。

图像输出模块用到的时钟分别为sys_clk,pix_clk和DP参考时钟lnk_clk_p,lnk_clk_n。sys_clk为Microblaze处理器和AXI域时钟,其频率为100 MHz。DP核参考时钟为135 MHz差分时钟,由时钟管理芯片SI5338提供。视频像素时钟pix_clk频率根据实际图像分辨率、帧率以及采用几线制像素输出接口共同决定。这里采用4像素接口输出3 840×2 160@60 Hz图像,因此pix_clk频率为148.5 MHz。DisplayPort核定制为DP 1.2,色彩深度为16 bit,支持4像素接口,最大通道数为4,最大链接速率为5.4 Gbit/s。

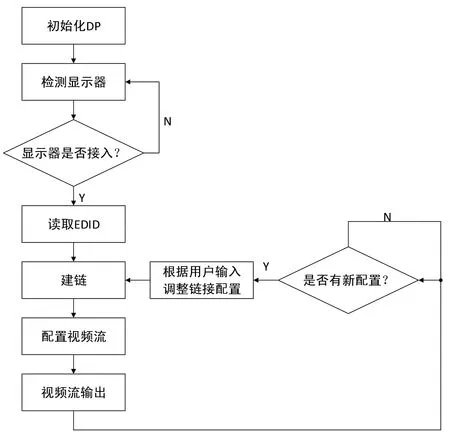

DisplayPort物理层使用双向AUX通道接口信号,4个高速通道的4个收发器映射到FPGA的MGT_BANK_118中的4个GTX收发器,DP内核基于AXI4-Lite接口用以配置,支持1.62、2.7或5.4 Gbps/s的1、2或4通道的自动通道速率和宽度调整。MicroBlaze处理器通过AXI4-Lite接口与DP核连接。用户可以通过软核对TX进行初始化,MicroBlaze处理器通过对DP核的相关寄存器写入和读取操作来启动和维护主链路。MicroBlaze首先完成对各AXI外设包括AXI Uart lite和DisplayPort Source IP的初始化,然后对DP核进行控制。MicroBlaze对DP核的控制流程图如图9所示。

图9 MicroBlaze控制DP流程Fig.9 Control flow diagram of MicroBlaze on DP

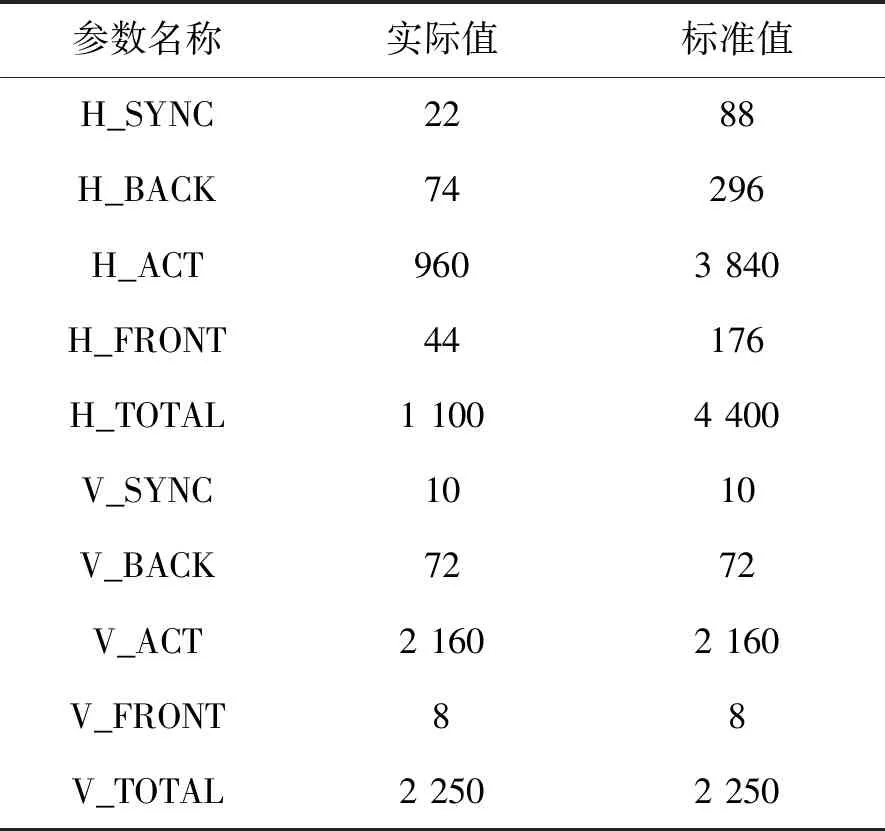

在VESA标准里面,3 840×2 160@60 +消隐 = 4 400×2 250@60,像素时钟频率为594 MHz。若采用4像素接口,则像素时钟频率变为594 MHz/4=148.5 MHz,满足设计需求。一个像素时钟传输4个像素,因此传输一行3 840个像素需要960个像素时钟周期。输出的3 840×2 160@ 60Hz图像行、场各参数如表1所示,水平相关的几个参数是标准值的1/4,垂直相关的几个参数与标准一致。

表1 输出图像的行、场参数Tab.1 Row and field parameters of output image

图10 DP输出3 840×2 160@60Hz图像Fig.10 DP outputs 3 840×2 160@60Hz images

图11 显示器的EDID信息Fig.11 EDID information of display

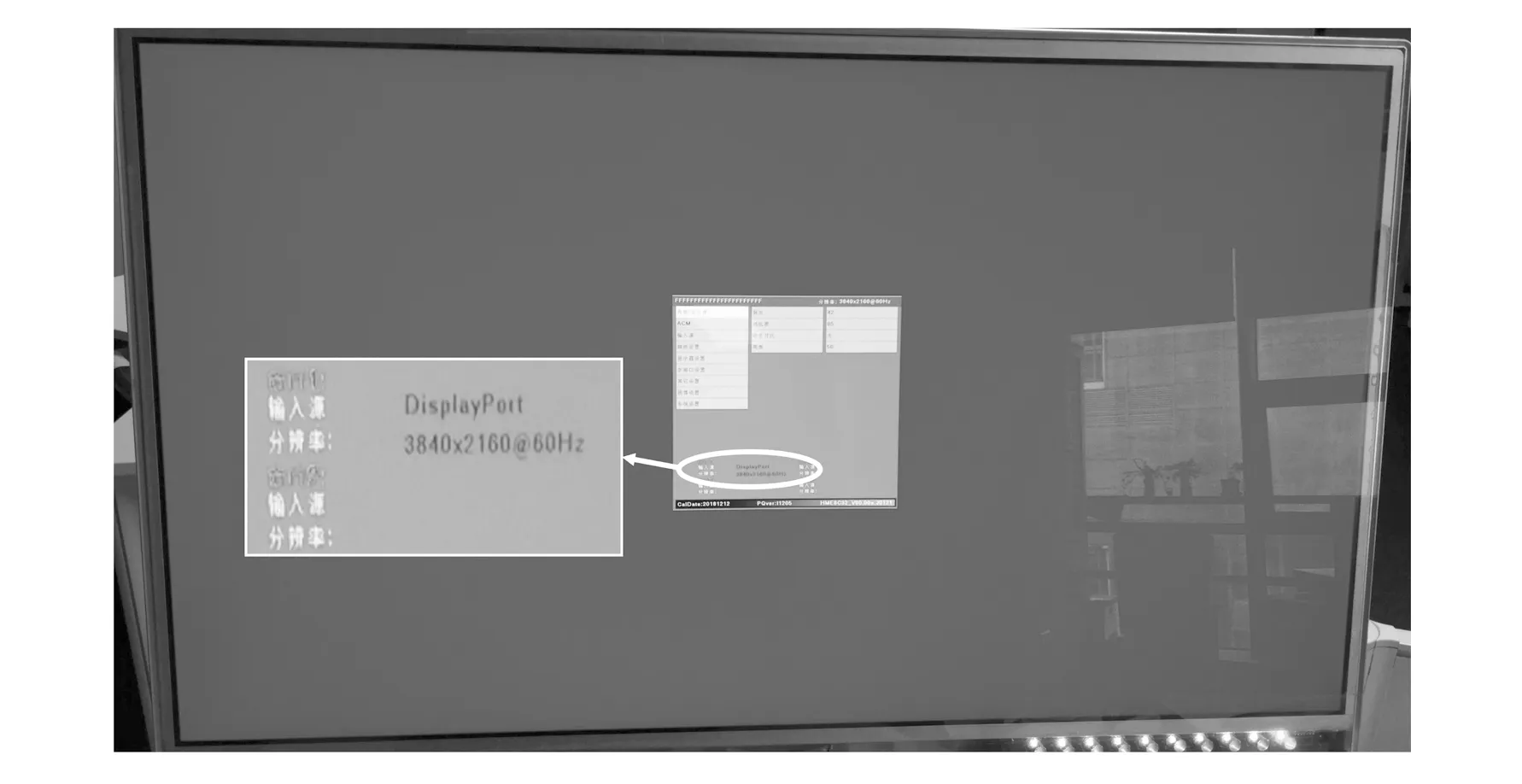

验证设备使用医疗4K超高清显示器,通过MicroBlaze软核配置DP核输出3 840×2 160@60 Hz的工作模式,同时Video Pattern模块输出4像素接口时序,图像数据为47’h0000_0000_FFFF即颜色为纯蓝色。如图10所示,从局部放大的显示器的控制界面可以看到当前显示的图像分辨率的信息。

通过AUX通道读取的显示器的EDID信息如图11所示,EDID信息由串口打印。

6 实验结果

对FPGA进行编程时,JTAG编程器与下载电路的连接通过一个7 PIN间距1 mm的接插件端子,端子的接口定义为一种非常规接口的JTAG编程口。两路SDI输入,一路DP输出。验证设备使用的是普通的医疗4K超高清显示器。通过MicroBlaze软核配置DP核输出3 840×2 160@60 Hz的工作模式。

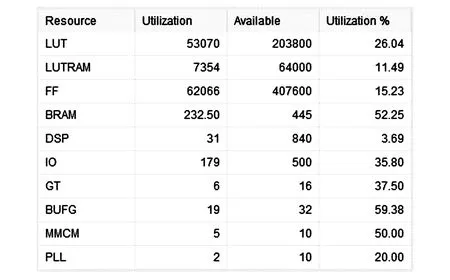

图12 系统逻辑资源使用情况Fig.12 Usage of system logical resource

系统逻辑资源消耗如图12所示,该统计数据来自Vivado 2017.3工具对本设计编译后的结果,BUFG、MMCM、BRAM使用较多,占到资源的50%以上。

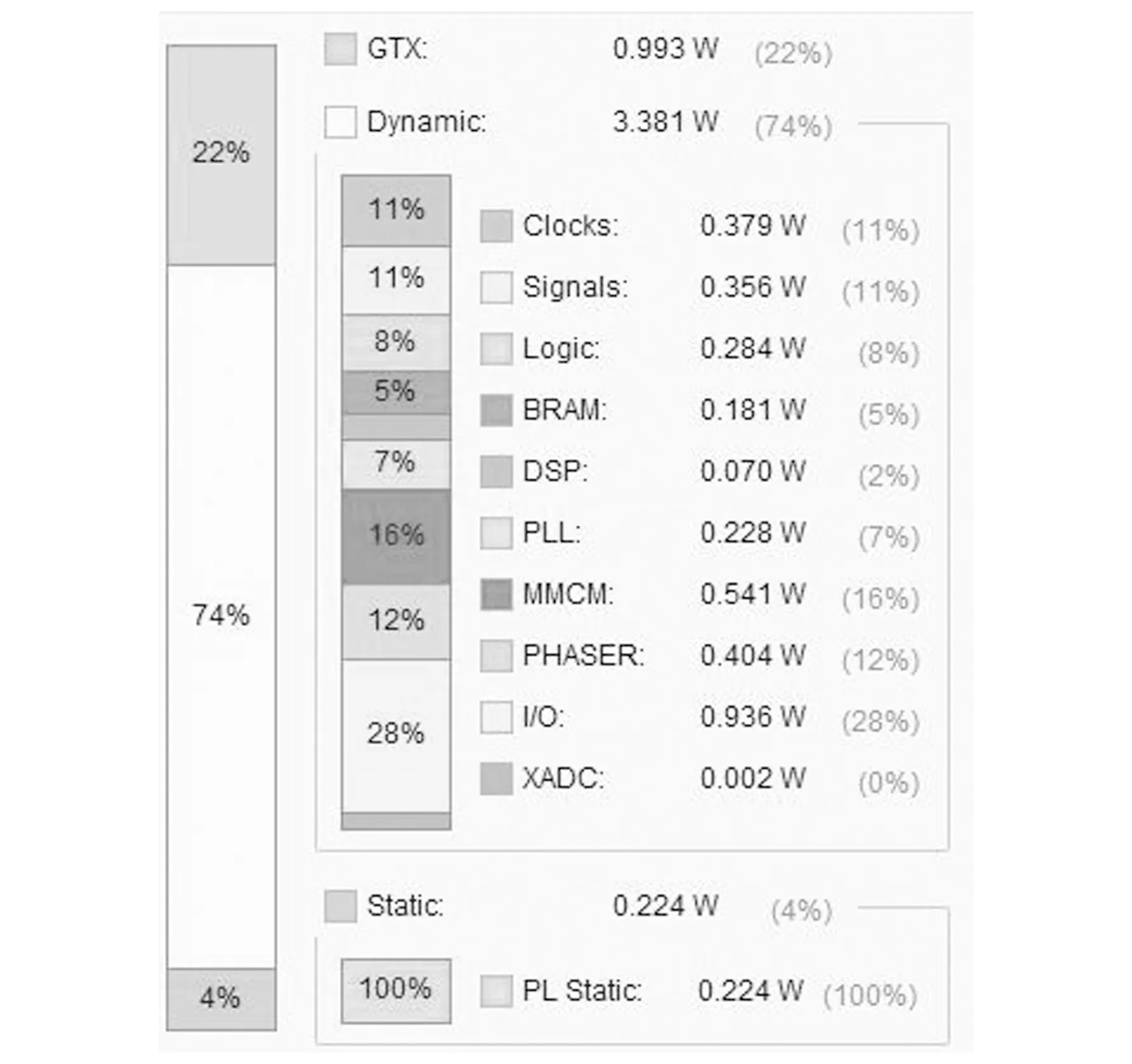

系统总片上功耗主要分为设计的动态功耗和静态功耗。静态功耗分为器件静态和设计静态,器件静态表示当器件上电并且没有设置时晶体管泄露功率,设计静态表示当器件被设置也没有切换活动时消耗的功率。本设计编译后的功耗统计如图13所示。

图13 系统功耗分析Fig.13 Analysis of system power

图14 系统实验环境Fig.14 System experimental environment

图15 2D模式SBS图像Fig.15 2D mode SBS image

从图13可以计算出,总的片上功耗为4.598 W,其中动态功耗占系统总功耗的96%。FPGA的功耗统计为系统的散热设计和电源设计提供了参考。

系统实验环境如图14所示,右侧显示器为4K高清医用裸眼3D显示器,左侧电脑主机为控制电脑。系统前端采用两路SDI信号输入,通过DP接口输出SBS格式的立体图像到裸眼3D显示器,显示器输出3D立体的效果。由于拍摄的是二维图片,所以从照片上不能明显看出裸眼3D效果。

输出给3D显示器之前的图像显示效果如图15所示,图像采用SBS拼接方式,分辨率为3 840×2 160,刷新率为60 Hz。

7 结 论

本文设计的基于FPGA的4K裸眼立体显示系统支持参考时钟为148.5 MHz的双路SDI-1080P高清视频输入,经FPGA做格式变换、物理层编解码和拼接等图像处理后,可获得3 840×2 160@60 Hz的SBS拼接格式图像,该图像可直接驱动裸眼立体显示器。经验证,该系统支持单人两视点观看,最佳观看距离为2 m,可视角度为±35°。本系统为高清晰3D显示和高速视频处理领域提供一种切实可行的设计方案,有望在医疗教学、会诊和立体手术室等领域取得更进一步的发展。